Патенты с меткой «запоминающее»

Аналоговое запоминающее устройство

Номер патента: 1062794

Опубликовано: 23.12.1983

МПК: G11C 27/00

Метки: аналоговое, запоминающее

...устройства в режимевыборки и снижает его быстродействиеЦелью изобретения является повышение точности и быстродействия 60устройства,Поставленная цель достигаетсятем, что в аналоговом запоминающемустройстве, содержащем двенадцать , 65 активных элементов, выполненных в виде транзисторов, и три пассивных . элемента, выполненных в виде резисторов, один нывод первого резистора является входом устройства, другой вывод соединен с базами первого и второго транзисторов, эмиттеры кото- рых подключены к первым выводам второго и третьего резисторон соответственно, базы третьего и четвертого транзисторов соединены с эмиттерами пятого и шестого транзисторов соответственно, эмиттеры третьего и четвертого транзисторов являются выходом...

Запоминающее устройство с самоконтролем

Номер патента: 1065884

Опубликовано: 07.01.1984

Авторы: Акопов, Маркарян, Наджарян, Чахоян

МПК: G11C 11/00

Метки: запоминающее, самоконтролем

...третьего селектора, вторые входы второго и гретьего селекторов подключенык третьему входу блока управления, одни из выходов котороо соединены с входами сумматора по модулю два, выход которого подключен к информационному входу второго триггера, вход синхронизации и инверсный выход котороо соединены соответственно с первым выходом первого генератора импульсов и с во о элмснта задержки, выход которого подключсн к становочному входу второго тригсра, и"я 1065884мой выход которого соединен со счетным входом счетчика ошибок, установочный вход и выходы которого подключены соответственно к другому выходу блока управления и к входам элемента ИЛИ, выход которого соединен с информационным входом первого триггера, выход которого подключен к...

Динамическое запоминающее устройство

Номер патента: 1065886

Опубликовано: 07.01.1984

МПК: G11C 11/34

Метки: динамическое, запоминающее

...17 импульсов, первый десцифратор 8, сче 1 пк 19 адреса регецсрдции, блок 20 синхрснизации, дополнительный элемент ИЛИ 21 и второй дешифратор 22. Блок 8 имеет входы 23. 27 соответственно с первого по пятый и выхо. ды 2837 соответственно с первсгс) по десятый.Блок Ю синхронизации ( фиг. 2) содержит распределитель 38 импульсов, третий дешифратор 39, триггеры 40 и 41. элсченты И 42 и 43 и элементы И- Н Е 44 и 45.Рассмотр)м лва Режима рдбоГы мс 1 ройствд: режич записи-считывания д;цц 1 х при огсутствии регенерации и режим здпц игчитывдция при наличии рег и рации50 В первом режиме работы код адреса ячейки, к которой необходимо обратиться в режиме записи, выставляется на входах 7, а данные - на входах 2.На входе 27 выставляется код операции...

Буферное запоминающее устройство

Номер патента: 1065888

Опубликовано: 07.01.1984

Авторы: Гриц, Лупиков, Маслеников, Спиваков

МПК: G11C 11/00

Метки: буферное, запоминающее

...блока 5 формирования адреса. Вход первого элемента НЕ 8 соединен с шиной 6 КОД ОПЕРАЦИИ, а его выход подключен к третьему входу блока 5 формирования адреса и вторым входам элементов И 3 второй группы. Вход второго элемента НЕ 9 соединен с выходом сумматора 4 по модулю два, а его выход подключен к первому входу первого блока элементов И 10, второй вход которой соединен с выходом первого элемента НЕ 8. Первый и второй входы блока элементов И 11 соответственно подключены к выходу сумматора 4 по модулю два и входу первого элемента НЕ 8. Третьи входы первого 10 и второго 11 блока элементовИ подключены к шине 12 СИНХРОНИЗАЦИЯ. Блок 5 формирования адреса содержит счетчики адреса записи и чтения, элементы ИИЛИ, элементы И, пример реализации...

Аналоговое запоминающее устройство

Номер патента: 1065889

Опубликовано: 07.01.1984

Автор: Данилов

МПК: G11C 27/00

Метки: аналоговое, запоминающее

...пулевого потенциала, другая обкладка второго конденсатора соединена с неинвертируюшнм входом дифференциального усилителя и с выходом второго ключа, первый вход которого соединен с выходом активного фильтра низких частот, вход активного фильтра низких частот соединен с другим выводом первого резистора и с входом неинвертирующего усилителя, выход которого соединен с входом пассивного КС- фильтра высоких частот, выход которого соединен с вторым входом первого ключа, второй вход второго ключа соединен с шиной управления.На чертеже изображена функциональная схема предлагаемого устройства. Устройство содержит дифференциальный усилитель 1, накопительные элементы на первом и втором конденсаторах 2 и 3, пассивные элементы на первом и втором...

Аналоговое запоминающее устройство

Номер патента: 1067535

Опубликовано: 15.01.1984

Автор: Солонин

МПК: G11C 27/00

Метки: аналоговое, запоминающее

...фиг. 1 буквами а, б,в, г, д, е.Аналоговое запоминающее устройство работает следующим образом.В исходном состоянии разряды 5 сдвигающего регистра 13 находятся в нулевом состоянии. Управляемый генератор импульсов 14 находится в ждущем режиме.В режиме записи на один иэ входов элемента сравнения 1 подается входное напряжение через согласукщий элемент 3, на другой вход - линейно нарастающее напряжение с Выхода генератора 2. При достижении равенства этих напряжений изменяется состояние на выходе элемента. сравнения 1, и одновибратор 5 Формирует импульс 15, который через открытый ключ 8 (ключ 9 в режиме записи закрыт) поступает на информационный вход сдвигающего регистра 13 и навход формирователя импульсов 12,Сигнал с выхода Формирователя...

Запоминающее устройство

Номер патента: 1069000

Опубликовано: 23.01.1984

Автор: Беляков

МПК: G11C 19/00

Метки: запоминающее

...21. Каждый из блоков. 4 буферных регистров имеет.информационные входы 22, управляю щий вход 23 - вход записи информаций, управляющий вход 24 - вход сдвига информации; информационные выходы 25, управляющий выход 26 - выход признака отсутствия информации в 45 буферных регистрах, управляющий выход 27 -, выход признака отсутствия свободных буферных регистров, Каждый из блоков 5 синхронизации имеет; " вход 28 - вход кода операции, вход 29 - вход сигнала "Буфер обращений пуст", вход 30 - вход сигнала фБуфер информации заполнен", выход 31 выход сигнала "Сдвиг", выход 32 ъ выходы управляющих сигналов накопителя, выход 33 - выход сигнала "Запись".Коммутатор б имеет информационные входы 34, управляющие входы 35, информационные выходы 36. Блок 7...

Оперативное запоминающее устройство

Номер патента: 1069001

Опубликовано: 23.01.1984

МПК: G11C 11/00

Метки: запоминающее, оперативное

...регистра, к одним входам перного блока сравнения, к информационьщ входам второго регистра и к одним входам второго блока сравнения,другие входы второго блока сравненияподключены к выходам нторого регистра, выходы лесного регистра - к другим входам первого блока сравненияи нычитателя, выходы которого подключены к информационньщ входам адресного регистра и к одним нходам третьего блока сравнения, другой входкоторого янляется третьим входом устройства, выходы блоков сравненияподключены к соответствующим входамблока управления, выход накопителяпризнаков подключен к соответствующему входу блока управления и к одномувходу элемента И другой вход которого подключен к выходу накопителяданных, выход элемента И являетсявыходом...

Запоминающее устройство с последовательным доступом

Номер патента: 1070606

Опубликовано: 30.01.1984

МПК: G11C 9/00

Метки: доступом, запоминающее, последовательным

...н соответствии с которым генератор 1 синхросигналов формирует серию синхросигналов на прямом и инверсном выходах. Сигналы с инверсного выходагенератора 1 синхросигналов посту"пают на счетный вход адресногосчетчика 3, в соответствии с которыми на его выходах 11 формируетсяпоследовательный ряд М -разрядныхдвоичных кодов. Эти коды через переключатель б адресных шин поступаютна % -адресных входов одноразрядногоблока 2 памяти, на (-к) оставшиесявходы которого через переключательб адресных шин поступает неизменный 60код по шине 12 адреса обращения.Код, поступающий по шине 12 адресаобращения в режиме обращения, является статическим адресом, определяющим 2 адресную область ячеек памятиу одноразрядного блока 2 памяти, к которым осуществляется...

Резервированное запоминающее устройство

Номер патента: 1070608

Опубликовано: 30.01.1984

Авторы: Петровский, Полукеев, Шастин

МПК: G11C 29/00

Метки: запоминающее, резервированное

...5задержки, элемент НЕ и дешифраторкоманд, входы которого подключенысоответственно к первым входам первого и второго элементов И, к одномуиз входов РВ -триггера, выходу последнего разряда первого и информационному входу второго регистров сдвига,к выходу второго разряда второгорегистра сдвига, к тактовым входампервого, второго и информационномувходу третьего регистров сдвига ивыходу первого элемента ИЛИ, первыйвход которого соединен с информационным входом первого регистра и другим входом Р 5-триггера,. а второй2 Овход - с выходом второго разрядатретьего регистра сдвига, выход первого разряда которого подключен квторому входу второго элемента И,а установочный и тактовый входы -соответственно к выходу элемента НЕи установочным входам...

Резервированное запоминающее устройство с самоконтролем

Номер патента: 1070609

Опубликовано: 30.01.1984

Авторы: Балахонов, Огнев, Цурпал

МПК: G11C 29/00

Метки: запоминающее, резервированное, самоконтролем

...производятся его контроль и диагностикас целью обнаружения и локализациивсех дефектных запоминающих элементов. Для обнаружения и локализации дефектных запоминающих элементов,возникающих в процессе эксплуатацииустройства, проводятся дополнитель"ные контроль и диагностика, проведение которых облегчается и упротцается20 25 30 35 45 50 55 60 40 наличием оперативного контроля правильности работы адресных цепей устройства во время обращения.В случае обнаружения деФектов, приводящих к неправильной работе дешифраторов, запоминающих элементов, ключей выборки, строк, столбцов, уси. лителей считывания и т.д., произвоится отключение дефектной строки столбца) и подключение исправной резервной. Порядок замены дефектных строк, столбцов одинаков...

Запоминающее устройство с коррекцией информации

Номер патента: 1070610

Опубликовано: 30.01.1984

Автор: Конопелько

МПК: G11C 29/00

Метки: запоминающее, информации, коррекцией

...устройства, вход 21 разреше" ния записи и вход 22 разрешения считынания первого регистра, Крометого, устройство содержит блок 23сравнения с одними из входов 24,блок 25 суммирования сигналов ошибокс одними из входов 26 и блок 27 обнарукения ошибок. Позициями 28 и 29обозначены соответственно одни идругие выходы первого регистра. Устройство содержит также первый 30и второй 31 дешифраторы, предназначенные для декодирования первого ивторого признаков ошибок соответственно, формирователь 32 сигналовошибок,. постоянный накопитель 33с входами 34, блок 35 приоритета свходами Зб, первый блок 37 коррекции ошибок с входами 38 и 39, второй блок 40 коррекции ошибок с входами 41 и 42 и выходаи 43 и 44 и третий регистр 45Блок обнаружения ошибок содержит...

Оптоэлектронное запоминающее устройство

Номер патента: 1072096

Опубликовано: 07.02.1984

Авторы: Басов, Плотников, Сагитов, Селезнев

МПК: G11C 11/42

Метки: запоминающее, оптоэлектронное

...и оптически связаны с фокусирующим блоком, излучатели второй группы подключены к выходу первому адресного регистра и оптически связаны с фокусирующим блоком, Фотоприемники второй группы подключены к второму регистру адреса, выходы которого подключены к первым входам элемента памяти, фотоприемники третьей группы подклю" чены к второму входному регистру, выходы .которого подключены к вторым входам элемента памяти, излучатели третьей группы подключены к выходному регистру, входы которого подключены к выходам элемента памяти.Устранение связи накопительных блоков с первыми выходным и входным регистром посредством электрических проводов повышает помехозащищенность работы устройства. Свет воспринимают не сами элементы памяти, а...

Трансформаторное постоянное запоминающее устройство

Номер патента: 1072097

Опубликовано: 07.02.1984

МПК: G11C 17/00

Метки: запоминающее, постоянное, трансформаторное

...и по числу трансформаторов усилительные 4 и шунтирующие 5 транзисторы, причем один из концов обмотки считывания каждого иэ трансформаторов 2 подключен к шине нулевого потенциала, а другой - к базе соответствующего усилительного транзистораи-р-и-типа 4, эмиттер которого подключен к шине нулевого потенциала,а коллектор соединен с коллекторамисоответствующих усилительных транзисторов других числовых линеек 1 и через резистор 6 подключен к шине питания, Базы шунтирующих транзисторов 5, соответствующих каждой числовой линейке 1, объединены. Выходы ключей 3 выборки числовых линеек 1 через резисторы 7 подключены к шине питания. Устройство содержит дополнительный резистор 8 и развязываю.щие трансформаторы 9, Один конец первой обмотки каждого из...

Аналоговое запоминающее устройство

Номер патента: 1072101

Опубликовано: 07.02.1984

Авторы: Андреев, Мелихов, Николайчук, Шептебань

МПК: G11C 27/00

Метки: аналоговое, запоминающее

...известного устройстваявляется низкие быстродействие и точность, обусловленные тем, что припереключении каждого из запоминающих элементов в режим хранения,напряжение .на его выходе изменяется от нулевого значения до значениязапомненного напряжения. В режимехранения цепью обратной связи охватываются два последовательно включенных усилителя запоминающего элемента, Это приводит к значительномупереходному процессу и затягиваниювремени установления выходного напряжения, что снижает быстродействиеустройства. Кроме того, наличиеключей, не охваченных цепью стабилизирующей обратной связи, между выходом устройства и выходами запоминающих элементов приводит к появлению дополнительной погрешности в выходном сигнале.Наиболее близким по...

Запоминающее устройство с автономным контролем

Номер патента: 1072102

Опубликовано: 07.02.1984

Автор: Беспалов

МПК: G11C 29/00

Метки: автономным, запоминающее, контролем

...соответственно к вторым входам первого и второго блоков сравнения, введены элементы задержки, элементы И, второй, третий и четвертый триггеры, первые входы которых соединены с вторым входом дешифратора и подключены к входу первого элемента задержки, выход которого соединен с первыми входами второго и третьегоэлементов И и с входом второго элемента задержки, выход которого соединен с первым входом четвертого элемента И, выход последнего соединен с вторым входом второго элемента ИЛИ, второй вход второго элемента И соединен .с выходом первого блока сравнения, второй вход третьего элемента И соединен с выходом второго блока сравнения, выход первого элемента ИЛИ подключен к второму входу второго триггера, выходы второго и третьего...

Запоминающее устройство с коррекцией однократных ошибок

Номер патента: 1073799

Опубликовано: 15.02.1984

Авторы: Самойлов, Фокин, Щербаков

МПК: G11C 29/00

Метки: запоминающее, коррекцией, однократных, ошибок

...обусловлена наличием последовательной цепи, состоящей изшифратора, схемы сравнения, дешифратора и выходного регистра числа.Другим недостатком укаэанногоустройства является искажение выходной информации в случае отказа вотдельных узлах устройства, напримерв шифраторе, схеме сравнения или вдешифраторе, что снижает надежность.Цель изобретения - повышение быстродействия и надежности устройстваза счет исправления однократныхошибок не только в разрядах основнойи избыточной памяти, но и в другихблоках устройства и уменьшения глубины декодирования за счет увеличений,количества разрядов избыточной памяти 1Поставленная цель достигается тем,что в запоминающее устройство с коррекцией однократных ошибок, содержащее основной и дополнительный...

Буферное запоминающее устройство

Номер патента: 1075310

Опубликовано: 23.02.1984

Авторы: Гриц, Лупиков, Маслеников, Светников, Спиваков

МПК: G11C 19/00

Метки: буферное, запоминающее

...являются вторые входы триггеров.На чертеже изображена функциональная схема предложенного устройства.Устройство содержит накопитель 1,регистры 2, счетчик 3 адреса записи,счетчик 4 адреса считывания, блок 5задания приоритетов обращений, счетчик б слов, селекторы 7, триггеры 8,элементы И 9, дополнительные счетчики 10 адреса считывания, дополнительные счетчики 11 слов, первый 12,второй 13 управляющие входы и входы14 обращения устройства,Число регистров 2, селекторов 7,триггеров 8, счетчиков 4 и 10 адреса считывания и.счетчиков б и 11слов соответствует числу внешнихблоков обработки (не показаны), вкоторые выдается информация иэ буферного запоминающего устройства.Еслив различных сеансах работы устройства характер распределения каналовпо...

Запоминающее устройство с коррекцией ошибок

Номер патента: 1075312

Опубликовано: 23.02.1984

Авторы: Дичка, Забуранный, Корнейчук, Орлова, Палкин

МПК: G11C 29/00

Метки: запоминающее, коррекцией, ошибок

...первого и второгонакопителей,На чертеже приведена блоксхема . запоминающего устройства,содержащего регистр 1 адреса, дешифраторы 2 и 3 адреса, накопители4 и 5, регистры б - 9, блоки 10 и 11сравнения, блоки 12-14 элементов И,элемент ИЛИ 15, блок 1 б элементов ИЛИ,регистр 17 и блок 18 управления.В предлагаемом устройстве информация одновременно записывается(считывается) в оба накопителя 4 и 5.Слово, подлежащее записи, находится в выходном регистре 17, Содержимое одноименных ячеек накопителей 4и 5, в которые необходимо записатьинформацию, считывается на регистрыб. Обратный код содержимого регистров б и 7 записывается в те жеячейки накопителей 4 и 5 и считывается обратно на регистры б и 7.Коды с регистров б и 7, а также...

Полупроводниковое запоминающее устройство

Номер патента: 1076947

Опубликовано: 28.02.1984

Авторы: Вартанов, Круглова, Лашевский, Неустроев

МПК: G11C 11/10

Метки: запоминающее, полупроводниковое

...ОЗУ и ПЗУ. Входы дешифраторов 25 столбцов накопителей ОЗУ и ПЗУ также соединены с соответствующими адресными шинами, их управляющие входы - с управляюгцей:пипой, выходы - с соответствукнцими шинами столбцов накопителей ОЗУ и ПЗУ соответственно 12.Однако известное техническое решение является избыточным и приводит к большим аппаратурным затратам из-за наличия двух полных дешифраторов строк.Цель изобретения - упрощение устройства. Поставленная цель достигается тем, что в полупроводниковом запоминаюгцем устройстве, содержащем первый и второй накопители, входы первых групп которых 4 О являются соответственно входами первой и второй групп устройства, входы вторых групп первого и второго накопителей соедичены соответственно с выходами...

Запоминающее устройство с самоконтролем

Номер патента: 1076952

Опубликовано: 28.02.1984

Автор: Абузяров

МПК: G11C 29/00

Метки: запоминающее, самоконтролем

...вход регистра 6 ошибок. Блок 8 реализованна схемах сложения по модулю два, например, 500 ИЕ 60. Блок 9 сумматоров помодулю два служит для формирования попоступающим на его вход 64-м информационным разрядим кода коррекции по кодуЗО Хэммицга (первый выхол) и восьми контрольных разрядов для контроля по модулюдва второй выход). Блок 9 реализован,например, на интегральных схемах 500ИЕ 60.Блок 10 сравнения служит для формиравацця кода синдрома. Представляет собойвосемь схем сравнения, на каждую изкоторых поступает разряд кода коррекциис выхода регистра 5 информации и с выхода блока 9 сумматоров по модулю два.4 О Блок 11 сверток по модулю два служитдля контроля правильности приема кодаадреса на регистр 4 адреса. Реализованна 500 ИЕ 60....

Резервированное запоминающее устройство

Номер патента: 1076953

Опубликовано: 28.02.1984

Авторы: Виглин, Клепиков, Петровский, Шастин

МПК: G11C 29/00

Метки: запоминающее, резервированное

...являются 16 15 20 25 30 35 40 45 50 55 Выходами устройгтиз, друие и;Олы сумматра солиеы с Выходами рабочих блО К)ЕЕ ЕЗМ 51 ГИ И ЕЕРВЕ)ГО КОЛ ЫЛ ГЗТОРЯИсклкчецис из реультяОВ суммрова.и и я и н ф О р м я ц и и р сзе р и 1 у с ыеО В д 11 е 1 н ы Й момет блока пзмя 1 дЕстигегся Еутсм ес д В О й н О Г О с у л м и р О е я 11 и 51 1 и еф О р м я ц и я и я СЧМЛЗТОР ОДЗЕТС 51 1 ДВУМ ВХОЕЗМ . НС- посредственно с рабочеТ блока памяти и с Выхода первно коммутягоря). Б зтом случае орязрядяя сумма ЕО модулн) дня дВух ОдинякОВых дВОичыу чисел ряння (0, так кяк в каждом разряд чисел суммируется либо 0 с О, либо 1 сЕО Е ==- == О, 1 + 1 = О, переос Отбрасывается и остается 0), при зтом нс имсет значеия, правильцяя или неправильная информация...

Ассоциативное запоминающее устройство

Номер патента: 1080213

Опубликовано: 15.03.1984

МПК: G11C 15/00

Метки: ассоциативное, запоминающее

...причем первые входы дополнительных ассоциативных элементов памяти подключены к одному из выходов входного регистра, вторые входы - к шинам разрешения считывания, третьи - к шинам разрешения записи, первые выходы дополнительных ассоциативных элементов памяти соединены с одними из входон выходного регистра, вторые выходы - с одним из, входов соответстнующего формирователя сигналов состояния ячеек памяти.Каждый Формирователь сигналовсостояния ячеек памяти содержит триггеры и элементы И и ИЛИ, причем выходы первого и второго элементов Иподключены к единичным входам первого и второго триггеров, нулевые входы которых соединены с выходом первого элемента ИЛИ, а выходы - с входами третьего элемента И, выходтретьего триггера подключен к однимиз...

Постоянное запоминающее устройство

Номер патента: 1080214

Опубликовано: 15.03.1984

Авторы: Бузунов, Буренков, Валов, Зюканов, Прасолов

МПК: G11C 17/00

Метки: запоминающее, постоянное

...элементов ИЛИ первой группы, выходы которых подключены к управляющим входам элементов И соответствующих групп, выходы которых соединены с соответствующими входами элементов ИЛИ второй группы, регистр числа, выходы элементов ИЛИ второй группы подключены к соответствующим входам регистра числа, установочные входы которого соединены с адресным входом старшего разряда адреса дешифратора адреса, разрядные шины накопителя соединены с входами элементов И соответствующих групп в соответствии с формулойМ= (Я+Р) вооп,где М - номер выходной строки накопителя;Б - номер,.элемента И (8=0,1,2,,п),Р = 0,1,2 п и - разрядность хранимых слов.В накопителе, содержащем в пересечении адресных и разрядных шинэлементы памяти, входы П"1 элементов памяти,...

Постоянное запоминающее устройство

Номер патента: 1080215

Опубликовано: 15.03.1984

Авторы: Ефимов, Нестерук, Потапов

МПК: G11C 17/00

Метки: запоминающее, постоянное

...выходампервого нагрузочного элемента ипервого накопительного элемента,вход которого соединен с выходомвторого элемента НЕ, вход которогои вход второго нагрузочного элементасоединены с выходом второго накопительного элемента, вход которого ивход первого делителя частоты подключены к выходу элемента И-НЕ, входпервого и выход второго нагрузочныхэлементов соединены с шиной нулевого потенциала, выход каждого предыдущего делителя частоты, кромепоследнего, соединен с входом последующего делителя частоты, выход;последнего делителя частоты являетсявыходом генератора, управляющимивходами которого являются входыустановки коэффициента деления делителей частоты.На фнг.1 изображенафункциональная схема предложенного устройства;на фиг.2 -...

Резервированное запоминающее устройство

Номер патента: 1080217

Опубликовано: 15.03.1984

Авторы: Обухов, Петровский, Шастин

МПК: G11C 29/00

Метки: запоминающее, резервированное

...е5 О Предложенное устройство содержит(Фиг. 1) основные блоки 1 - 1 памяти (где и 1 - целое число) с адресными входами 2 и выходами 3,резервный блок 4 памяти, дополнительный блок 5 памяти, первый дешифратор б с выходами 7 и выходом 8,первую группу элементов И 9, - 9 л,генератор 1 О тактовых импульсов, сумматор 11 по модулю два с входом 12,коммутаторы 13- 13 д с выходами 14,вторую группу элементов И 15 - 15 яс выходами 1 б и Формирователь 17сигнала неисправности с выходом 18.Формирователь сигналов неисправс ности содержит (фиг. 2) второй дешифратор 19, элемент НЕ 20 и элементИ 21,Резервный блок 4 памяти предназначен для записи и хранения .пораз,рядной суммы по модулю два инфор 1 мации соответствующих ячеек блоков 5 11- 1...

Запоминающее устройство с автономным контролем

Номер патента: 1081669

Опубликовано: 23.03.1984

Автор: Горшков

МПК: G11C 29/00

Метки: автономным, запоминающее, контролем

...в случае, когда необходимо вместо одного слова массива записать другое. При этом производится считывание из накопителя 2 ранее записанного слова на дополнительный регистр 3. Записываемое слово с входа 14 поступает на регистр 1. При этом на вход 20 и входы 19 поступает код О, Элемент И 7 закрыт. С выхода 16 дополнительного регистра 3 на вход элемента ИЛИ 8 поступает нулевое значение маркерного разряда. Так как на оба входа элемента ИЛИ 8 поступает код 0, то на выходе его также будет нулевой сигнал, разрешающий работу реверсивных счетчиков блока 12, Содержимое регистров 1 и 3 поступает на вход блока 5 сумматоров по модулю два, где формируется поразряд- . 1081669 устройства, второй выход регистра числа подключен к первому входу...

Запоминающее устройство с сохранением информации при отключении питания

Номер патента: 1083236

Опубликовано: 30.03.1984

Авторы: Бурченко, Кучерявый, Прокопенко, Трепашко

МПК: G11C 29/00

Метки: запоминающее, информации, отключении, питания, сохранением

...накопителя, третьи входы регистра адреса, первого и второго элементов И, вторые входы формирователей импульсов и элемента задержки соединены с первым входом накопителя.На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - пример реализации порогового элемента; на фиг. 3 - временная диаграмма работы устройства.Устройство содержит накопитель 1, блок 2 сопряжения, разделительный элемент 3, например диод, резервный источник 4 питания, выполненный, например, в виде блока ионисторов КИ 1-1 или КИ 1-2 ограничи-тельный элемент 5, например, резистор,фильтрующий элемент 6, например, конденсатор, пороговый элемент 7, регистр 8адреса, элемент ИЛИ 9, первый элементИ 10, первый формирователь 11 импульсов,элемент 12 задержки, второй...

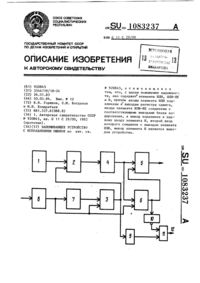

Запоминающее устройство с исправлением ошибок

Номер патента: 1083237

Опубликовано: 30.03.1984

Авторы: Богданов, Горшков, Кондратьев

МПК: G11C 29/00

Метки: запоминающее, исправлением, ошибок

...сдвига имитируется ошибка,которая с помощью сумматоров по модулю два вносится в считываемое из на копителя слово, При этом, если в сумматорах по модулю два в одном илинескольких разрядах имеются отказы,которые равносильны наличию кода "О"на соответствующих входах сумматоров,соединенных с выходами регистра сдви.га, то при этом контроль аппаратуры для коррекции ошибок либо Совсемне производится (при отказах в "О"всех входов сумматоров по модулюдва, соединенных с выходами регистрасдвига), либо производится не в полной мере (при отказах рассмотренноготипа на одном или нескольких входахсумматоров по модулю два). Следовательно, недостатком этого устройстваявляется неполнота контроля его узлов, что обуславливает низкую достоверность...

Буферное запоминающее устройство с самоконтролем

Номер патента: 1084890

Опубликовано: 07.04.1984

МПК: G11C 19/00, G11C 29/00

Метки: буферное, запоминающее, самоконтролем

...к 5первому входу второго элемента И,выход которого является другим управляющим выходом устройства, второйвход второго элемента И подключен ксоответствующему выходу блока управления, выход второго триггера подключен к первому входу второго эле -мента И, выход которого являетсядругим управляющим выходом устройства, второй вход второго элемента 25И подключен к соответствующему ныхо.ду блока управления, вход элементаНЕ подключен к третьему входу первого триггера и к соответствующемувыходу блока управления. 30Второй сдвиговый.регистр предназначен для считывания побитно информации, хранимой в ЗУ, и выдачи словаили байта информации приемнику инФормации, что позволяет проводить З 5контроль данных, записанных в ЗУ попериметру. Кроме того, в...