Запоминающее устройство с исправлением ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1083237

Авторы: Богданов, Горшков, Кондратьев

Текст

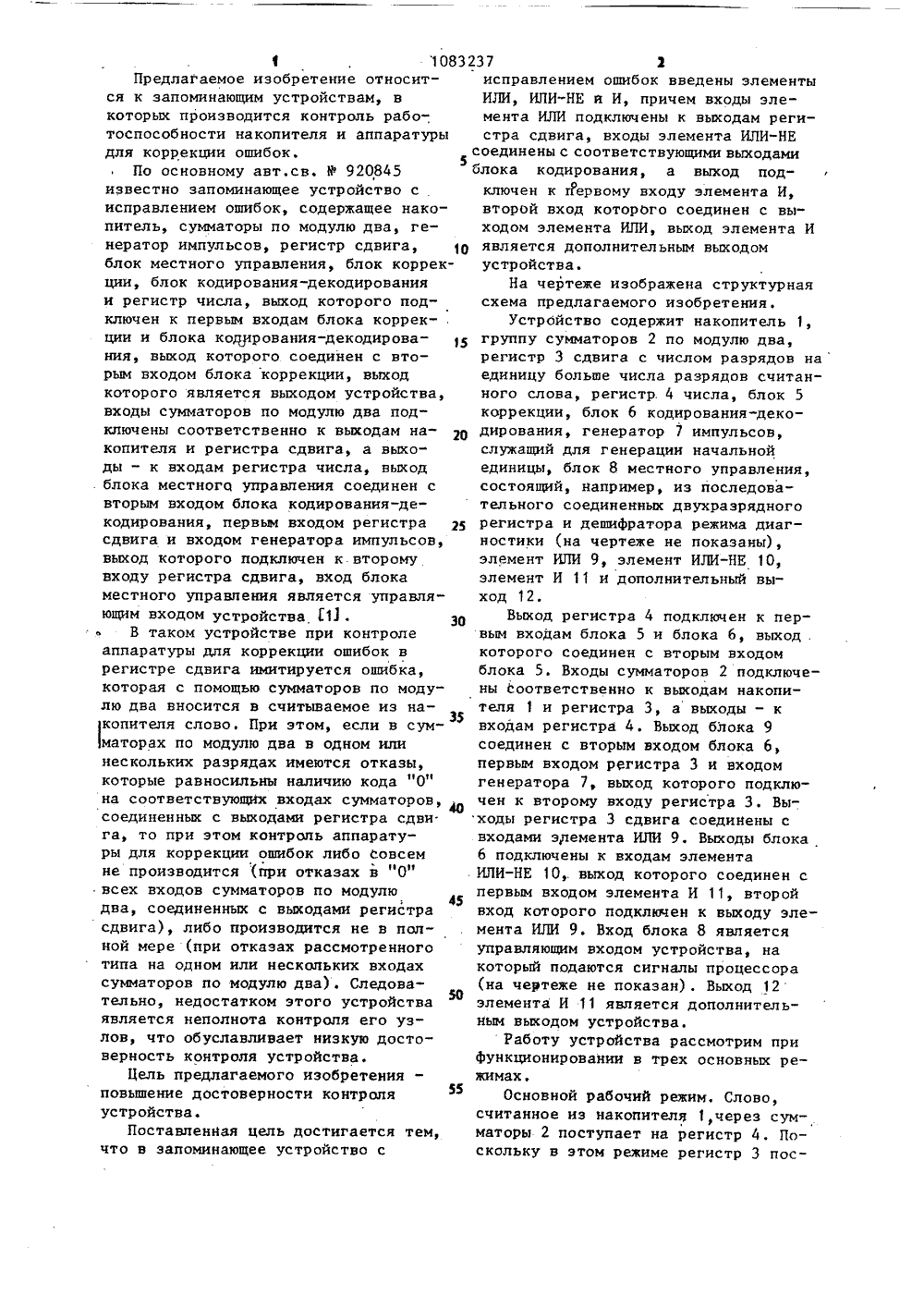

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 1083 3) С 11 С 29 00 РЕТТОН ство ССС1982ЙСТВОвт. св. ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ4 ОПИСАНИ АВТОРСКОМУ СВИДЕТ(54) (57) ЗАПОМИНАЮЩЕЕ УСТРС ИСПРАВЛЕНИЕМ ОШИБОК по В 920845, о т л и ч а ю щ е е с ятем, что, с целью повышения надежности, оно содержит элементы ИЛИ, ИЛИ-НЕи И, причем входы элемента ИЛИ подключены к выходам регистра сдвига,входы элемента ИЛИ-НЕ соединены ссоответствующими выходами блока кодирования, а выход подключен к первому входу .элемента И, второй входкоторого соединен с выходом элементаИЛИ, выход элемента И является выходом устройства.исправлением ошибок введены элементыИЛИ, ИЛИ-НЕ и И, причем входы элемента ИЛИ подключены к выходам регистра сдвига, входы элемента ИЛИ-НЕ5соединены с соответствующими выходамиблока кодирования, а выход подключен к первому входу элемента И,второй вход которого соединен с выходом элемента ИЛИ, выход элемента И1 О является дополнительным выходомустройства.На чертеже изображена структурнаясхема предлагаемого изобретения,Устройство содержит накопитель 1,группу сумматоров 2 по модулю два,регистр 3 сдвига с числом разрядов наединицу больше числа разрядов считанного слова, регистр. 4 числа, блок 5коррекции, блок б кодирования-декодирования, генератор 7 импульсов,служащий для генерации начальнойединицы, блок 8 местного управления,состоящий, например, из последовательного соединенных двухразрядногод 5 регистра и дешифратора режима диагностики (на чертеже не показаны),элемент ИЛИ 9, элемент ИЛИ-НЕ 10,элемент И 11 и дополнительный выход 12.Выход регистра 4 подключен к первым входам блока 5 н блока 6, выход .которого соединен с вторым входомблока 5. Входы сумматоров 2 подключены соответственно к выходам накопи 35теля 1 и регистра 3 а выходы - кФвходам регистра 4. Выход блока 9соединен с вторым входом блока 6,первым входом регистра 3 и входомгенератора 7, выход которого подключен к второму входу регистра 3. Выходы регистра 3 сдвига соединены свходами эпемента ИЛИ 9. Выходы блока6 подключены к входам элементаИЛИ-НЕ 10, выход которого соединен спервым входом элемента И 11, второйвход которого подключен к выходу элемента ИЛИ 9. Вход блока 8 являетсяуправляющим входом устройства, накоторый подаются сигналы процессора50(на чертеже не показан) . Выход 12элемента И 11 является дополнительным выходом устройства,Работу устройства рассмотрим прифункционировании в трех основных режимах.Основной рабочий режим, Слово,считанное из накопителя 1,через сумматоры 2 поступает на регистр 4. Поскольку в этом режиме регистр 3 пос 1 08Предлагаемое изобретение относится к запоминающим устройствам, вкоторых производится контроль работоспособности накопителя и аппаратурыдля коррекции ошибок.По основному авт.св, В 920845известно запоминающее устройство сисправлением ошибок, содержащее накопитель, сумматоры по модулю два, генератор импульсов, регистр сдвига,блок местного управления, блок коррекции, блок кодирования-декодированияи регистр числа, выход которого подключен к первым входам блока коррек- .ции и блока копирования-декодирования, выход которого соединен с вторым входом блока коррекции, выходкоторого является выходом устройства,входы сумматоров по модулю два подключены соответственно к выходам накопителя и регистра сдвига, а выходы - к входам регистра числа, выход. блока местного управления соединен свторым входом блока кодирования-декодирования, первым входом регистрасдвига и входом генератора импульсов,выход которого подключен к второмувходу регистра сдвига, вход блокаместного управления является управляющим входом устройства 113 .В таком устройстве при контролеаппаратуры для коррекции ошибок врегистре сдвига имитируется ошибка,которая с помощью сумматоров по модулю два вносится в считываемое из на копителя слово, При этом, если в сумматорах по модулю два в одном илинескольких разрядах имеются отказы,которые равносильны наличию кода "О"на соответствующих входах сумматоров,соединенных с выходами регистра сдви.га, то при этом контроль аппаратуры для коррекции ошибок либо Совсемне производится (при отказах в "О"всех входов сумматоров по модулюдва, соединенных с выходами регистрасдвига), либо производится не в полной мере (при отказах рассмотренноготипа на одном или нескольких входахсумматоров по модулю два). Следовательно, недостатком этого устройстваявляется неполнота контроля его узлов, что обуславливает низкую достоверность контроля устройства.Цель предлагаемого изобретения -повышение достоверности контроляустройства,Поставленная цель достигается тем,что в запоминающее устройство с 3237 1Составитель В, ГордоноваРедактор Е. Кривина Техред О.Неце Корректор А. Ильин,Заказ 3464 Тираж 575 ПодписноеВНИИПИ Государственного комитета СССРпо делам изобретений и открытий113035, Москва, Ж; Раушская наб., д. 4/5 Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 з 1083тоянно находится в нулевом состоянии,то слово поступает на регистр 4 безизменения. На выходе элемента ИЛИ 9при этом код "0", который закрываетэлемент И 11. Следовательно, на выходе 12 в этом режиме код "0". Еслипри считывании данных произошлаошибка, то блок 6 формирует корректирующий код и блок 5 исправляетошибку или, если произошпа двойная 1 бошибка, то блок 6 запрещает коррекцию и выдает сигнал сбоя.Первый режим диагностики. Из процессора выдается код режима Д 1, прикотором блок 8 формирует сигнал, запрещающий коррекцию ошибок. В этомрежиме регистр сдвига 3 также обнулен. Поэтому на выходе элемента ИЛИ 9и выходе 12 устройства код "0". Считанная информация поступает в процес сор без исправления и сравнивается сэталоном. Таким образом может бытьобнаруженанеработоспособная ячейкапамяти,Второй режим диагностики. Из процессора выдается код режима Д 2, прикотором блок 8 снимает запрет коррекции ошибки и включает генератор 7,При считывании информации накопителя 1 начальная единица заноситсяв нулевой разряд регистра сдвига 3,что приводит при правильной работесоответствующего сумматора 2 по модулю два к инверсии нулевого разрядасчитанного слова. Таким образом ими 35тируется одиночная ошибка в нулевомразряде, которая должна быть исправлена, что контролируется процессоромпутем сравнивания с эталоном, Приэтом на выходе 7 элемента ИЛИ 9 код"1", а на выходе элемента ИЛИ-НЕ 10 -код "0", Элемент И 11 закрыт и навыходе Я устройства нулевой сигнал.Если сумматор 2 по модулю два, соответствующий нулевому разряду, отказалтаким образом, что это равносильноподаче на его вход, соединенный с 237 4выходом регистра 3 сдвига, кода "0",то ошибка вноситься не будет, В этомслучае на всех выходах блока 6 кодирования-Декодирования код "0". Следовательно, на выходе элемента ИЛИ-НЕ10 будет код "1". Так как на выходеэлемента ИЛИ 9 также код "1", тоэлемент И 11 открывается и на выходе12 устройства формируется единичныйсигнал, соответствующий о неработоспособности сумматора 2 по модулю дванулевого разряда. При каждом последующем считывании информации единицав регистре 3 передаетея в следующийразряд, то есть происходит имитация.одиночной ошибки поочередно в каждомразряде считанного слова. Одновременно также производится, контроль сумматоров 2 по модулю два соответствующихразрядов. При переходе единицы в последний разряд регистра 3 происходитинверсия сразу в двух разрядах считанного слова, то есть имитируетсядвойная ошибка, которая не исправляется, но должна быть обранужена.Таким образом, при правильной работе блока 6 и сумматоров 2 по модулю два в К циклах считывания (где К -число разрядов считанного слова)происходит сравнение с эталоном, ав (К+1) цикле считывания происходитзапланированный сбой, который учитывается процессором. Если сумматоры 2по модулю два неработоспособны и невносят в этом режиме искусственнуюошибку, то на выходе 12 устройстваформируется единичный сигнал,Технико-экономическим преимуществом предлагаемого устройства посравнению с прототипом является более высокая достоверность контроляузлов, которая обусловлена тем, чтоза счет введения всеготрех нескольких элементов И, ИЛИ и ИЛИ-НЕ в режиме диагностики Д 2 производитсяконтроль работоспособности сумматоров по модулю два.

СмотретьЗаявка

3544719, 26.01.1983

ПУШКИНСКОЕ ВЫСШЕЕ ОРДЕНА КРАСНОЙ ЗВЕЗДЫ УЧИЛИЩЕ РАДИОЭЛЕКТРОНИКИ ПРОТИВОВОЗДУШНОЙ ОБОРОНЫ

ГОРШКОВ ВИКТОР НИКОЛАЕВИЧ, БОГДАНОВ СЕРГЕЙ МИХАЙЛОВИЧ, КОНДРАТЬЕВ МИХАИЛ НИКОЛАЕВИЧ

МПК / Метки

МПК: G11C 29/00

Метки: запоминающее, исправлением, ошибок

Опубликовано: 30.03.1984

Код ссылки

<a href="https://patents.su/3-1083237-zapominayushhee-ustrojjstvo-s-ispravleniem-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Запоминающее устройство с исправлением ошибок</a>

Предыдущий патент: Запоминающее устройство с сохранением информации при отключении питания

Следующий патент: Связующее для электроизоляционного фенопласта

Случайный патент: Способ обогащения асбестовой руды