G11C 29/00 — Контроль правильности работы запоминающих устройств; испытание запоминающих устройств во время режима ожидания или автономного режима работы

Запоминающее устройство с автономным контролем

Номер патента: 1081669

Опубликовано: 23.03.1984

Автор: Горшков

МПК: G11C 29/00

Метки: автономным, запоминающее, контролем

...в случае, когда необходимо вместо одного слова массива записать другое. При этом производится считывание из накопителя 2 ранее записанного слова на дополнительный регистр 3. Записываемое слово с входа 14 поступает на регистр 1. При этом на вход 20 и входы 19 поступает код О, Элемент И 7 закрыт. С выхода 16 дополнительного регистра 3 на вход элемента ИЛИ 8 поступает нулевое значение маркерного разряда. Так как на оба входа элемента ИЛИ 8 поступает код 0, то на выходе его также будет нулевой сигнал, разрешающий работу реверсивных счетчиков блока 12, Содержимое регистров 1 и 3 поступает на вход блока 5 сумматоров по модулю два, где формируется поразряд- . 1081669 устройства, второй выход регистра числа подключен к первому входу...

Устройство для тестового контроля памяти

Номер патента: 1083234

Опубликовано: 30.03.1984

Авторы: Белалов, Рудаков, Саламатов, Чалчинский

МПК: G11C 29/00

...входы которого соединены с другими выходами первого блока местного управления, другие входы второго коммутатора подключены соответственно к одним из выходов первого блока местного управления и к контрольным входам первого коммутатора и выходам регистра контрольной информации, входы которого соединены с выходами третьего коммутатора.На фиг. 1 представлена функциональная схема предлагаемого устройства; на фиг. 2 и 3 - функциональные схемы первого и второго блоков местного управления соответственно; на фиг. 4 - функциональ; ная схема блока контроля считанной информации. Устройство содержит (фиг. 1) первый 1и второй 2 коммутаторы, регистр 3 контроль25 30 35 40 45 50 55 ной информации, формирователь 4 контроль.- ных сигналов, первый...

Устройство для контроля постоянной памяти

Номер патента: 1083235

Опубликовано: 30.03.1984

Авторы: Кандирал, Коверга, Шраев

МПК: G11C 29/00

Метки: памяти, постоянной

...коммутаторы 3 и 4, дешифратор 5 (дешифратор начального состояния (и + 1) младших разрядов с О-го по 1-й счетчика 2), блоки 6 и 7 элементов И, выходы 8, эталонный блок 9 памяти, входы 10, блок 11 сравнения и блок 12 индикации, контролируемый блок 13 памяти.В исходном состоянии все разряды счетчика 2 находятся в нулевом состоянии. На нулевом выходе младшего О-го разряда счетчика 2 разрешающий, а на единичном запрещающий уровень сигнала. Запрещающий уровень сигнала на нулевом выходеУ3дешифратора 5 блокирует первые информационные входы коммутатора 4, а разрешающий уровень на единичном выходе дешифратора 5 пропускает по вторым информационным входам на выходы коммутатора 4 значения старших разрядов счетчика. На входах эталонного 9 и...

Запоминающее устройство с сохранением информации при отключении питания

Номер патента: 1083236

Опубликовано: 30.03.1984

Авторы: Бурченко, Кучерявый, Прокопенко, Трепашко

МПК: G11C 29/00

Метки: запоминающее, информации, отключении, питания, сохранением

...накопителя, третьи входы регистра адреса, первого и второго элементов И, вторые входы формирователей импульсов и элемента задержки соединены с первым входом накопителя.На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - пример реализации порогового элемента; на фиг. 3 - временная диаграмма работы устройства.Устройство содержит накопитель 1, блок 2 сопряжения, разделительный элемент 3, например диод, резервный источник 4 питания, выполненный, например, в виде блока ионисторов КИ 1-1 или КИ 1-2 ограничи-тельный элемент 5, например, резистор,фильтрующий элемент 6, например, конденсатор, пороговый элемент 7, регистр 8адреса, элемент ИЛИ 9, первый элементИ 10, первый формирователь 11 импульсов,элемент 12 задержки, второй...

Запоминающее устройство с исправлением ошибок

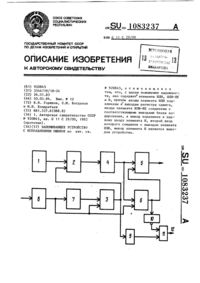

Номер патента: 1083237

Опубликовано: 30.03.1984

Авторы: Богданов, Горшков, Кондратьев

МПК: G11C 29/00

Метки: запоминающее, исправлением, ошибок

...сдвига имитируется ошибка,которая с помощью сумматоров по модулю два вносится в считываемое из на копителя слово, При этом, если в сумматорах по модулю два в одном илинескольких разрядах имеются отказы,которые равносильны наличию кода "О"на соответствующих входах сумматоров,соединенных с выходами регистра сдви.га, то при этом контроль аппаратуры для коррекции ошибок либо Совсемне производится (при отказах в "О"всех входов сумматоров по модулюдва, соединенных с выходами регистрасдвига), либо производится не в полной мере (при отказах рассмотренноготипа на одном или нескольких входахсумматоров по модулю два). Следовательно, недостатком этого устройстваявляется неполнота контроля его узлов, что обуславливает низкую достоверность...

Буферное запоминающее устройство с самоконтролем

Номер патента: 1084890

Опубликовано: 07.04.1984

МПК: G11C 19/00, G11C 29/00

Метки: буферное, запоминающее, самоконтролем

...к 5первому входу второго элемента И,выход которого является другим управляющим выходом устройства, второйвход второго элемента И подключен ксоответствующему выходу блока управления, выход второго триггера подключен к первому входу второго эле -мента И, выход которого являетсядругим управляющим выходом устройства, второй вход второго элемента 25И подключен к соответствующему ныхо.ду блока управления, вход элементаНЕ подключен к третьему входу первого триггера и к соответствующемувыходу блока управления. 30Второй сдвиговый.регистр предназначен для считывания побитно информации, хранимой в ЗУ, и выдачи словаили байта информации приемнику инФормации, что позволяет проводить З 5контроль данных, записанных в ЗУ попериметру. Кроме того, в...

Полупроводниковое запоминающее устройство с побайтовой модульной организацией

Номер патента: 1084900

Опубликовано: 07.04.1984

Авторы: Бородин, Егорова, Огнев, Столяров

МПК: G11C 29/00

Метки: запоминающее, модульной, организацией, побайтовой, полупроводниковое

...группа входов которого соединена с выходами второго блока формирования контрольных разрядов по вой 15, введены первый и второй блоки формирования четности, входы первого из которых соединены соответственно с первым и пятым информационными входами всех Имодулей памяти, а входы второго блока формирования четности соединены соответственно с первым и пятым информационными выходами всех Имодулей памяти, причем выход первого блока формирования четности соединен с входом дополнительного пятогс контрольного разряда И-го модуля памяти, выход которого соединен с первым дополнительным входом блока выработки сигнала ошибки, второй дополнительный вход которого соединен с выходом второго блока формирования четности.На чертеже представлена...

Устройство для контроля блоков памяти

Номер патента: 1084901

Опубликовано: 07.04.1984

МПК: G11C 29/00

...регистра подключен к второму входу второго элемента И, выход которого подключен ктактовому входу первого сдвиговогорегистра, второй выход первого триггера подключен к второму входу четвертого,элемента И, выход которого подключен к входу адресного счетчика иявляется соответствующим управляющимвыходом устройства, выходы адресногосчетчика подключены к входам пятогоэлемента И, выход которого подключенк первому входу шестого элемента И,установочный вход второго триггераподключен к выходу шестого элемента И,второй вхоц которого подключен к выходу блока сравнения, вход генератора тактовых импульсов подключен кпервому вьиоду второго триггера,второй вьиод которого является соот -ветствующим управляющим выходом устройства. На фиг, 1...

Постоянное запоминающее устройство с самоконтролем

Номер патента: 1084902

Опубликовано: 07.04.1984

МПК: G11C 29/00

Метки: запоминающее, постоянное, самоконтролем

...комбинации с О-м, 255-м,256-м, 511-м, 512-м, 767-м, 768-м и1028-м адресами) и позволяет выйтина контрольные ячейки ПЗУ, соответствующие вышеуказанным адресам, чтодает возможность определить исправность ПЗУ по адресным шинами, а так"же неисправность схемы, Формирующейадрес ячейки ПЗУ.На чертеже представлена структур ная схема постоянного запоминающегоустройства с самоконтролем,Устройство содержит адресную шину 1, шину 2 управления, блок 3 постоянной 1:мяти, первый дешиФратор 4адреса, второй дешифратор 5 а;реса,элемент ИЛИ 6, блок 7 сверткг па мо.дулю два, блок элементов И 8, элементИ-НЕ 9, счетчик 10, третий дешифратор адреса 11, информационный выход12, второй контрольный выход 13, первый контрольный выход 143 1084Работу ПЗУ с...

Запоминающее устройство

Номер патента: 1084903

Опубликовано: 07.04.1984

Автор: Безручко

МПК: G11C 29/00

Метки: запоминающее

...подключены к входам дешифратора,выход которого подключен к управляющему входу элемента сравнения, информационные входы которого подключенык соответствующим выходам второго итретьего счетчиков, входы которыхподключены к старшему разряду соответственно первого и второго регистров сдвига, выход элемента сравненияподключен к входу второго формирователя одиночных импульсов, к входутретьего триггера и к одному входупервого элемента ИЛИ, другой вход которого соединен с выходом второго элемента ИЛИ входы данного элемента ИЛИсоединены с выходами элементов Ивторой дополнительной группы, выходыэлементов И первой дополнительнойгруппы подключены к входам третьегоэлемента ИЛИ, вцход которого подклю чен к одному входу четвертого триггера и к одному...

Устройство для защиты информации в блоке памяти

Номер патента: 1084904

Опубликовано: 07.04.1984

Авторы: Абрамов, Агарок, Бабинов, Чулкина

МПК: G11C 29/00

Метки: блоке, защиты, информации, памяти

...источника пита.-ияподключены соответственно к входутретьего ключа и к вторым входам пер-.вого и второго ключей второму входу второго аднавибратора и пе .вомувходу элемента И, второй вход которого соединен с выходам гтарого одновибратора, а третий вход и выходявляются соответственно управляюпимВХОДОМ И ьтОРЫМ ВЫХОДОМ УСтРОйстВа,На фиг, 1 изображена Функциональ -ная схема предложенного устройства:на Фг. 2 - временные диаграм ,поясняющие работу ус;"ойства:Предложенное устройства соде"-.жи г (щи 1основной 1 и дополнительный 2 источники питания, компаратар 3, первый 4 и вта 1 ой 5 оп.-.овнбратсры, интегратор с, червьЙвторой 8 глючи, элемент " 9 .;.зервный источник 1 О питая.я, наверОатаре 0 э мен ) 1 г ад- " "аю.и втораи ;...

Устройство для коррекции ошибок в блоках памяти

Номер патента: 1086460

Опубликовано: 15.04.1984

Автор: Осмоловский

МПК: G11C 29/00

Метки: блоках, коррекции, ошибок, памяти

...по модулю два информа .циоинцх символов, обозначенных бук-.вами А-Л.1 А+ Б+ Г+Д+Ж+И+Д2 фА+ В+.Г+Е+Ж+ К+Д (1) 403 Б+ В+ Г+ 3+И+.К+В4Д+ Е + Ж+ 3 + И+ К+ ЛЗатем каждый иэ цичных символовподвергается стохастичесхому (квазислучайкому) преобразованию код воэдействиеи кваэислучайной кодирующейпоследовательности, На .этом процесскодирования заканчивается.Прямое и обраткое стохастическоепреобразование - этоизвестные опера ции, реализуемюе как умножение иделение полиномов по модулю иепрнводкмого полинома или выполняемые таб-лично 3 и 4,.При декодировании вначале вылняется обратное стохастическое пре-образование каждого ц-ичного символа под воздействием той же кваэислу 460 4 чайной последовательности,что и при кодировании, В результате, если...

Запоминающее устройство с самоконтролем

Номер патента: 1086461

Опубликовано: 15.04.1984

МПК: G11C 29/00

Метки: запоминающее, самоконтролем

...И являются контрольныьы выходами устройства.На чертеже изображена принципиальная схема предлагаемого устройства.Устройство содержит два блока 1 памяти, блоки 2 поразрядного сравнения, блоки 3 контроля, четыре элемента И 4, 42,4 , 4 , входные шины 5, управляющую шину 6, выходные шины 7, первую контрольную шину 8, инвертор 9, элемент 10 задержки,два блока 111 и 112 сравнения, вторую контрольную шину 12.Устройство работает следующим образом.На входы двух блоков 1 памяти и двух блоков 3 контроля по коду Хэмминга поступают коды адреса, числа команд по входным шинам 5 и запрос по шине 6 от арифметического устройства (на чертеже не показано) , Считанная из блоков памяти инФормация контролируется блоками 3 контроля по коду Хэмминга. В случае...

Запоминающее устройство с обнаружением ошибок

Номер патента: 1088073

Опубликовано: 23.04.1984

Автор: Горшков

МПК: G11C 29/00

Метки: запоминающее, обнаружением, ошибок

...записи массива слов код адреса и код записываемого слова подаются соответственно на входы регистра 4 и, через группу элементов ИЛИ 6, на входы регистра 2, и производится запись слова в соответствующую ячейку накопителя 1. На управляющие входы 21-23 при "этом подается нулевой уровень. Одновременно код адреса и код записываемого слова подаются соответственно на сумматор 7 и, через элементы ИЛИ 5, на сумматор 8, которые вырабатывают биты четности адреса и записываемо,го слова.Биты четности объединяются сумматором 9 в результирующий битС управляющего входы 20 на вход элемента НЕ 18 при этом поступает нулевой сигнал. Следовательно, на выходе элемента НЕ 18 при этом будет единичный уровень. В случае единичного значения результирующего бита он...

Запоминающее устройство с самоконтролем

Номер патента: 1089627

Опубликовано: 30.04.1984

Авторы: Колесник, Масленников

МПК: G11C 29/00

Метки: запоминающее, самоконтролем

...одними из выходов блока сравнения,одни из входов которого подключенык выходам второго накопителя информации, а другие - к выходам блокаконтроля, входы которого соединены с выходами первого накопителя информации, введены генератор тактовых импульсов, элемент задержки, элемент И и Формирователь сигналов, выход которого подключен к управляющему входу регистра числа, а входыподключены к выходу элемента задержки и выходу элемента И, первый входкоторого соединен с выходом генератора тактовых импульсов, а второйвход - с другим выходом блокасравнения, причем входы элементазадержки и генератора тактовых импульсов объединены и являются одним из управляющих входов устройства.На чертеже изображена структурная схема запоминающего устройства с...

Оперативное запоминающее устройство с обнаружением ошибок

Номер патента: 1089628

Опубликовано: 30.04.1984

Автор: Марголин

МПК: G11C 29/00

Метки: запоминающее, обнаружением, оперативное, ошибок

...коммутации устройства,контрольный выход 24 блока памяти,информационные 25 и адресные 26входы и информационные выходы 27 устройства. Устройство содержит такжесумматоры 28-33 по модулю два с первого по шестой,Логический блок содержит (см.фиг. 1) первый 34 и второй 35 элементы И, первый элемент И-НЕ 36, третий 37 и четвертый 38 элементы И ивторой элемент И-НЕ 39. Устройствосодержит также ключи 40-40 п .Во втором варианте выполнения логический блок содержит также (см. фиг. 2) третий элемент И-НЕ 4 1.Устройство работает следующим образом.В том случае, когда отсутствует необходимость в наращивании информационной емкости устройства, сумма- торы 32 и 33 (см. фиг. 1) используются для инвертирования и формирования сигнала управления ключами...

Оперативное запоминающее устройство

Номер патента: 1091226

Опубликовано: 07.05.1984

МПК: G11C 29/00

Метки: запоминающее, оперативное

...генератораи третьему входу накопителя, четвертый вход которого соединен с выходомпервого счетчика, информационныйвход устройства является одновременно и его выходом.На чертеже изображена схема устройства,Устройство содержит информационный вход 1, соединенный с регистром2 числа, подключенным к накопителю3, адресный вход 4, соединеный свходом регистра адреса, выход поляадреса ячеек которого соединен свходом поля адреса ячеек накогителя3, выход поля адреса запоминающихмодулей регистра 5 адреса соединен с 20,вторым входом блока б сравнения, первый вход которого соединен с выходомвторого счетчика 7, управляющийвход 8 устройства, соединенный спервым входом генератора 9, установочным входом первого счетчика 10и установочным входом второго...

Устройство для контроля оперативной памяти

Номер патента: 1091227

Опубликовано: 07.05.1984

Автор: Фадеев

МПК: G11C 29/00

Метки: оперативной, памяти

...на дополнительный сумматор помодулю два, изменяет единичный сигнал в цепи обратной связи на нулевой,в результате чего на четвертом тактев регистр сдвига запишется кодоваякомбинация 0000. При этом единичныйсигнал на выходе дешифратора сохраняется и производится инвертированиенулевого сигнала в цепи обратнойсвязи так, что на пятом такте врегистр записывается комбинация 000.После этого единичный сигнал на выходе дешифратора 8 исчезает и производится генерация рекурренты по правилукодирования Ф -последовательности доследующей комбинации 0001, после чегоснова формируется нулевая комбинация,т.е. кодовая последовательность будетциклически повторяться.Влок управления обеспечиваетформирование в соответствии с требуе"мыми временными диаграммами...

Запоминающее устройство с самоконтролем

Номер патента: 1091228

Опубликовано: 07.05.1984

Авторы: Гарбузов, Ковалев, Огнев

МПК: G11C 29/00

Метки: запоминающее, самоконтролем

...выходами устройства,введены логические блоки, перьыйэлемент И и коммутатор, одни из входов которого подключены соответствен. 20но к выходам первого формирователясигналов четности и к выходам формирователя сигналов кода Хемминга, авыходы - к входам первого регистрачисла, причем одни из вхацов первогоэлемента И и логичесих блоков с первого по третий соединены соответственно с вьпсодами второго формирователя сигналов четности и с выходамиформирователя сигналов проверочного 30слова, а другие входы логических блоков и первого элемента И подключенык контрольному выходу второго регистра числа, инверсные выходы которогои выход третьегологического блокасоединены соответственно с другиивходами коммутатора, выходы логических блоков, первого...

Устройство для контроля памяти

Номер патента: 1092568

Опубликовано: 15.05.1984

Авторы: Батырев, Долгушев, Нуров, Пасенков, Черенков

МПК: G11C 29/00

Метки: памяти

...входы второй группы которогоподключены к выходам второй группымногоканального генератора 1 простейших потоков, управляющий вход - ковторому выходу блока 5 управления,а выходы - ко входам контролируемого блока 6 памяти, информационныйвход блока 7 статистической обработки соединен с выходом контролируемого блока 6 памяти, его управляющий вход соединен с третьим выходомблока 5 управления, а выходы с одними входами блока 8 сравнения, другие входы которого подключены к другим выходам блока 5 управления, управляющий вход - к четвертому выходублока 5 управления, а выходы - ковходам блока 9 индикации, управляющий вход которого соединен с пятымвыходом блока 5 управления, шестойи седьмой выходы которого подключены соответственно к...

Устройство для контроля блоков памяти

Номер патента: 1092569

Опубликовано: 15.05.1984

Авторы: Белалов, Мусиенко, Рудаков, Саламатов, Чалчинский

МПК: G11C 29/00

...5, индикаторы 28-30, клавишу входа 31режима ожидания блока управленияи блок 32 прерывания,Блок прерываний содержит (фиг.2)первый 33 и второй 34 элементы согласования, элемент И 35, первый36 и второй 37 триггеры первый 38и второй 39 формирователи одиночныхимпульсов, второй элемент НЕ 40,третий 41 и четвертый 42 элементы 45согласования.Блок управления содержит (фиг, 3)кварцевый генератор 43 импульсов,триггеры 44-53, генераторы 54 и 55одиночных импульсов, элементы5 ОИ-НЕ 56 и 57, элементы НЕ 58, элементы И 59-64 и элементы ИЛИ 65-67,первый элемент НЕ 68,Индикаторы 28-30 выполнены в виде светодиодов. Блок 1 и блок 3 реализованы на интегральных микросхемах ИИС К 559 ИП 2, блоки 4 и 5 - наИМС К 559 ИП 1, регистр 22 - на ИМС К 155 ЛРЗ,...

Запоминающее устройство с коррекцией групповых ошибок

Номер патента: 1092570

Опубликовано: 15.05.1984

Авторы: Бруевич, Воробьев, Вушкарник, Куликов, Оношко, Смирнов

МПК: G11C 29/00

Метки: групповых, запоминающее, коррекцией, ошибок

...И четвертой группы и одни из входов эле"мента ИЛИ соединены соответственнос выходами сумматоров по модулю двапервой группы и с выходом первогосумматора по модулю два, выходы сумматоров по модулю два второй группыи второго сумматора по модулю дваподключены ко вторым входам элементов И четвертой группы, другим входам элемента ИЛИ и другим входамкомпараторов, выходы которых соединены с третьми входами соответствующих элементов И четвертой группы ивходами элемента ИЛИ-НЕ, выход которого подключен к первому входу второго элемента И, второй вход которого соединен с выходом элемента ИЛИ,выходы элементов И четвертой группыи выход второго элемента И являютсявыходами блока,На фиг.1 представлена функциональная схема устройства с...

Запоминающее устройство с самоконтролем

Номер патента: 1094071

Опубликовано: 23.05.1984

Авторы: Барашенков, Дряпак, Коминаров

МПК: G11C 29/00

Метки: запоминающее, самоконтролем

...того, блок управления содержит регистр управляющих сигналов, регистр неисправности, группу элементов И, элементы ИЛИ, элементы НЕ и элемент задержки, вход которого и входы синхронизации регистра управляющих сигналов и регистра неисправности объединены и являются первым входом блока, вторым и треть" ии входом которого являются соответственно вход признака записисчитцвания и вход обращения регистра управляющих сигналов, установочный вход которого и установочный вход регистра неисправности объединены и являются четвертым входом блока, 094071 4 причем входы первого, второго итретьего элементов НЕ являются соответственно пять 1 м, шестым и седьмцивходами блока, первый и второй. вхо-.ды элементов И группы подключены.соответственно.к...

Запоминающее устройство с самоконтролем

Номер патента: 1095240

Опубликовано: 30.05.1984

Авторы: Колесник, Масленников

МПК: G11C 29/00

Метки: запоминающее, самоконтролем

...вторые входы которых подключены к соответствующим выходам дешифратора, выходы сумматоров соединены с другими .входами накопителя. На чертеже изображена структурная схема запоминающего устройства с самоконтролем.Устройство содержит накопитель 1, один вход которого соединен с входом регистра 2 старших разрядов адреса и является входом 3 устройства, а выходы регистра 2 старших разрядов адреса соединены со входами дешифратора 4, который предназначен для выработки унитарного кода выбора определенного сегмента 5, на которые разделен накопитель 1. Управляющий вход каждого сегмента 5 соединен с выходом соответствующего сумматора 6 по модулю два, предназначенного для выработки инверсного значения сигнала, поступающего,на первый вход от...

Устройство для контроля записи и считывания информации

Номер патента: 1095241

Опубликовано: 30.05.1984

Автор: Горшков

МПК: G11C 29/00

Метки: записи, информации, считывания

...и информационными выходами ко10 15 20 25 30 35 40 50 45 55 торого являются соответственно другие входы регистра прямого кода и выходы элементов ИЛИ группы, а контрольными выходами - выходы контрольного регистра, введены регистр обратного хода и блок анализа кратности ошибок, одни из входов которого подключены соответственно к выходам регистра прямого кода и к выходам регистра обратного кода, одни из входов которого соединены с другими входами регистра прямого кода, а другие входы -с инверсными выходами информационного регистра и первыми входами элементов И второй группы, выходы которых подключены ко вторым входам элементов ИЛИ группы, первый и второй выходы блока анализа кратности ошибок соединены соответственно со вторыми входами...

Устройство поиска и контроля адреса страницы для доменной памяти

Номер патента: 1095242

Опубликовано: 30.05.1984

Авторы: Иванов, Косов, Савельев

МПК: G11C 29/00

Метки: адреса, доменной, памяти, поиска, страницы

...соответствующей метки времени, его третий вход - к шине управляющих сигналов 6, с которой поступает из контроллера потенциал разрешения добавления 1 в счетчик 3, его четвертый выход - к шине управляющих сигналов 6, с которой поступает из контроллера сигнал неравенства содержимого адресного регистра 1 содержимому счетчика 3, разрешающий прибавить 1 к содержимому счетчика 3 страниц.Выход пятого элемента И 12 подключен к первому входу второго элемента ИЛИ 16, второй вход которого соединен с выходом шестого элемента И 13. Первый вход шестого элемента И 13 соединен с шиной управляющих сигналов 6, с которой поступает из контроллера импульс соответствующий метки времени, а второй его вход соединен с шиной управляющих сигналов 6; с которой...

Запоминающее устройство с автономным контролем

Номер патента: 1096697

Опубликовано: 07.06.1984

МПК: G11C 29/00

Метки: автономным, запоминающее, контролем

...устройство с автономным конт- ко. ролем, содержащее накопитель, входы первойгруппы которого являются адресными входа- длми устройства, входы второй группы соедине-анны с входами первого блока формирования расигналов четности и входами первого блока коформирования контрольных сигналов по не мочетному модулю и являются числовыми вхо. надами устройства, выходы первого блока фор- мнмнровання сигналов четности соединены с вхоЭ 1096 постоянного запоминающего устройства (ПЗУ), а на фиг, 7 дана таблица декодирования дешифратора для модуля 7. Запоминающее устройство с автономным контролем, содержит накопитель 1, состоящий из блоков 2 памяти, входы первой группы 3 накопителя 1 соединены с входами шифратора 4 и являются адресными входами...

Устройство для защиты памяти

Номер патента: 1098036

Опубликовано: 15.06.1984

Авторы: Дмитриев, Корбашов, Сборовский, Семин, Сиротин

МПК: G11C 29/00

...соединена с вторь 1 ми группамиинформационных входов первого и второго сумматоров,Кроме того, блок преобразованияадреса содержит регистр и группуэлементов ИСКЛЮЧАЮЩЕЕ ИЛИ, первыевходы которых соединены с группойинформационных входов блока, вторыевходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы соединены через регистр с группойуправляющих входов блока, выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ образуют группу выкодов блока.В результате преобразования адресов несмежных и непересекающихсяти поступает через группу входов 9 устройства в блок преобразования адреса 1 напервые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 13. Преобразованный в соответствии с алгоритмом преобразования и ключом преобразования адрес обращения с выхода блока преобразования адреса 1...

Запоминающее устройство с регенерацией информации

Номер патента: 1098037

Опубликовано: 15.06.1984

Авторы: Бородавка, Евсикова, Клюев, Микитченко, Раллев, Ткач

МПК: G11C 29/00

Метки: запоминающее, информации, регенерацией

...2 и элементов И. Кроме того, в этом устройстве увеличена нагрузка на информационные выходы накопителя, так как к ним подключены входы блока анализа и входы группы пороговых элементов, что ухудшает эксплуатационные характеристики устройства.Целью изобретения является упрощение устройства.Поставленная цель достигается тем, что в запоминающее устройство с регенерацией информации, содержащее накопитель, блок формирования сигнала регенерации, блок управления, подключенный к накопителю и блоку формирования сигнала регенерации, блок пороговых элементов, входы которого подключены к выходам накопителя, введен блок элементов И, входы которого подключены к выходам блока пороговых элементов, а выходы блока элементов И соединены с входами блока...

Запоминающее устройство с самоконтролем

Номер патента: 1100638

Опубликовано: 30.06.1984

Автор: Барашенков

МПК: G11C 29/00

Метки: запоминающее, самоконтролем

...проверок,в-третьих, хотя бы один ненулевой гектор, не равный вектору общей про- З 0 верки.В первых двух случаях "базисные"разряды частник проверок содержат "О"в последнем случае - 1 .И ИКод адреса одной иэ двух ошибок 35определяется проверками, содержащими Н 1 ф в базисном разряде. Кодадреса второй ошибки находится как результат сложения векторов первойошибки,и вектора общей проверки. В .40соответствии с рассмотренными эначефниями частичные суммы образуют тримножества.В случае тройной ошибки (измене-ние четности информации в трех адресах при считывании из накопителя 1)значения частичных проверок могутобразовывать Б, 8 , Яфво-первьи, нулевой вектор - дляпроверок, в которые не включены ад 50реса ошибок, т,е. эти адреса содержат "О"...