G06F — Обработка цифровых данных с помощью электрических устройств

Устройство для отладки программно-аппаратных блоков

Номер патента: 1348839

Опубликовано: 30.10.1987

Авторы: Гудзенко, Кельнер, Сигалов, Юрасов

МПК: G06F 11/28

Метки: блоков, отладки, программно-аппаратных

...условиямиво время отладки при каждом обращении МП к памяти или УВВ на одном изуправляющих выходов элементов ИЛИ 78или 66 соответственно вырабатываетсясигнал уровня "1".В регистры 8-11 записываются кодыусловий, по которым отладка должнаначаться, а также условия окончанияотладки. В соответствии с этими условиями на единичном выходе триггера 2554 вырабатывается сигнал режима. Врежиме отладки этим сигналом блокируется блок 1 постоянной памяти, включается блок 7 оперативной памяти(через элемент И 87), этот же сигналблокирует работу дешифратора 24,Перейдя в режим отладки, микропроцессор начинает отработку программы, загруженной в блок 12 оперативной памяти отлаживаемых программ, либо находящейся в памяти ОМУ(в зависимости от...

Устройство для отладки программ

Номер патента: 1348840

Опубликовано: 30.10.1987

Авторы: Батраков, Квасов, Мурин, Назаров, Трунков

МПК: G06F 11/28

...пока сигнал его переполнения не будет выдан на управляющий выход 29 устройства, сигнализируя об окончании работы устройства во втором режиме,зывающую часть (модуль) программы из вызываемой, Код с группы выходов счетчика 63 адреса возврата каждой ячейки поступает на вторую группу информационных входов соответствую 5 щих схем 64 сравнения, на первыегруппы информационных входов которых поступает значение текущего адреса выполняемой программы с группы 58 информационных входов.При поступлении сигнала с третьего выхода дешифратора 10 команд на вход 36 БП блок 1 буферной памяти работает следующим образом. Этот сигнал поступает на первый вход элемента И 53 каждой ячейки, На выходе элементов И 53 ячеек БП, имеющих разрешающие потенциалы на...

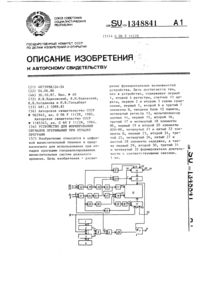

Устройство для формирования сигналов прерывания при отладке программ

Номер патента: 1348841

Опубликовано: 30.10.1987

Авторы: Богданова, Будовский, Бурковский, Гольдберг

МПК: G06F 11/28

Метки: отладке, прерывания, программ, сигналов, формирования

...некоторая младшая часть адреса, сформированного в магистрали ЭВМ.После заноса исходных данных и разметки блока 12 на входе 34 устанавливается потенциал высокого уровя "1", а на входе 35 - низкого уровня 0", что соответствует режиму отладки программ. В результате разрешается прохождение строба адреса с выхода 9 через элемент 21. Формируется потенциал низкого уровня на втором установочном входе мультиплексора 14, запрещающий прохождение в устройство данных с входа 37. Через инвертор 16 на первый установочный вход мультиплексора 14 поступает потенциал высокого уровня, разрешающий прохождение информации с выхода блока 12 на регистр 13. В режиме отладки при выполнении микроЭВМ некоторой программы строб адрес с входа 9 устройства через...

Устройство для сопряжения внешних устройств с накопителем на магнитной ленте

Номер патента: 1348842

Опубликовано: 30.10.1987

Авторы: Жабыко, Попеленский, Солодихин, Солодовников

МПК: G06F 13/16

Метки: внешних, ленте, магнитной, накопителем, сопряжения, устройств

...1 по входу 3640 (фиг,10)Ланные во входной регистр112 поступают иэ блока 6, сопровождаемые синхронизиручщими сигналами146. Память блока 7 состоит из двуходинаковых узлов 117 (ОЗУ 1) и 11845 (ОЗУ 2) с трехстабильным выходом. Счетчики 15 н 116 адреса формиручт текущие значения адресов памяти. В исходном состоянии триггер 57 ( фиг.2Ус -танонлен н "1" (А=1), что соотнетст -5 п вует записи н узел 117 (вход 133 блока 7). Счетчик 115 адреса считаетадрес в направлении увеличения по запускающему сигналу 147 занесения ипамять. После заполнения ОЗУ 1, когда55 адрес вновь станет равен "0", дешифратор 119 вырабатьвает сигнал АДРМАХ на выходе 140, который перебрасывает триггер 57 (А=О) и триггер 58в блоке 1 по входу 90, устанавливая42 поступают на...

Устройство для сопряжения процессора с группой устройств памяти

Номер патента: 1348843

Опубликовано: 30.10.1987

Авторы: Морозов, Панков, Потапов, Танасейчук

МПК: G06F 13/16

Метки: группой, памяти, процессора, сопряжения, устройств

...содержимое35которого определяет выбираемый дешифратором 14 раздел 4 памяти и разрешенный вид доступа запись и/или чтение к этому разделу. В случае, еслипроизошел запрещенный для данногораздела 4 памяти вид обращения, тона регистре 12 фиксируется номер раздела памяти, к которому производилось ошибочное обращение, а такжеустанавливается триггер 16 что позФ45воляет программе обслуживания ошибки обращения к каналу определить,вызван ли этот сбой аппаратурой либоошибкой программирования,При включении питания системы мини(микро)ЭВМ или при канальной уста 50новке в процессе работы процессор 2вырабатывает сигнал "Сброс", устанавливающий триггер 15 в нулевое состояние, что соответствует режиму работыустройства "Системный", В этом...

Устройство для обмена информацией между цифровой и аналоговой вычислительными машинами

Номер патента: 1348844

Опубликовано: 30.10.1987

Авторы: Иванов, Кравцов, Кривицкий, Святный, Фишман, Щербак

МПК: G06F 13/24

Метки: аналоговой, вычислительными, информацией, машинами, между, обмена, цифровой

...насчетный вход счетчика 69. Процессповторится сначала.Диаграммы напряжений, поясняющиеработу блока временного управления,представлены на фиг, 3,С выхода элемента ИЛИ 68 единичные сигналы поступают на второй входэлемента ИЛИ 29, вызывая тем самымпрограммы вычисления фазовых переменных. После выполнения программывычисления К-й фазовой переменнойпрограмма обработки прерываний запустит на выполнение фоновые задачи, 40выполнение которых будет продолжаться до завершения времени цикла ,.После завершения цикла программа обработки прерываний снова запустит навыполнение первую программу. Каждыйраз при запуске первой программы производится обмен информацией междуЦВМ 43 и БП 42, При этом на адреснойшине 45 ЦВМ 43 появляется первый адрес ВП 42, по...

Шинный формирователь

Номер патента: 1348845

Опубликовано: 30.10.1987

Авторы: Бадалян, Лисечко, Петросян

МПК: G06F 13/36

Метки: формирователь, шинный

...сигнала по переднему и зад-.нему фронтам, а сигнал низкого уровня напряжения с выхода второго 2(первого 1) приемника поступает навходы элементов 7 (5) и 8 (6) задержки, обеспечивающих соответственнозадержку сигнала по переднему и заднему фронтам, Сигнал высокого уровня напряжения с выхода первого 5(третьего 7) элемента задержки посту 45пает на информационный вход первого3 (второго 4) передатчика, а сигналнизкого уровня напряжения с выходатретьего 7 (первого 5) элемента задержки поступает на информационный50вход второго 4 (первого 3) передатчика. Высокий уровень напряжения с выхода первого 5 (четвертого 8) элемента задержки поступает на блокирующиевходы второго 2 (первого 1) приемника и второго 4 (первого 3)...

Устройство для исследования вероятностных графов

Номер патента: 1348846

Опубликовано: 30.10.1987

Авторы: Коптев, Овчинников, Петриенко

МПК: G06F 15/173

Метки: вероятностных, графов, исследования

...управляющей вершиной, то при установке соответствующих триггеров 16 в нулевое состояние единичный сигнал, проходя через элементы ИЛИ 6, откроет элементы И 23, указывающие на присутствие в первом подграфе управляющих вершины. При этом из блока 34 будет считан код веса исполнительных вершин, имеющих н первом подграфе связь хотя бы с одной управляющей вершиной, Единичные потенциалы на соответствующих выходах 27 указывают на наличие исполнительных вершин, связанных впервом подграфе хотя бы с одной управляющей вершиной,В четвертом такте с входа 31 натактовый вход распределителя 24 поступает сигнал опроса, по которомураспределитель 24 выдает сигнал насвоей первый выход при этом открывается первый ключ 22, с выхода которого вес первого...

Устройство для моделирования ветви графа

Номер патента: 1348847

Опубликовано: 30.10.1987

МПК: G06F 15/173

Метки: ветви, графа, моделирования

...устройства. В этом случае через элемент И 9 данного устройства проходит последовательность импульсов первого разряда распределителя 28 импульсов. Последовательность импульсов с выхода первого элемента И 9 поступает на выход элемента ИЛИ 14, выходной сигнал которого открывает элемент И 7 во время фазы сдвига дополнительного двоичного кода Р младших разрядов веса первой ветви. Последовательность импульсов первого выхода распределителя 27 поступает через элемент И 7 на вход слагаемого сумматора 2, на вход второго слагаемого которого с выхода регистра 1 сдвигается дополнительный двоичный код Р младших разрядов веса первой ветви, Сумматор 2 последовательно во времени, начиная с младших разрядов, выполняет сумми 1 О 15 20 25 30 35 40 45 50...

Устройство для моделирования графов

Номер патента: 1348849

Опубликовано: 30.10.1987

Авторы: Бычковский, Захаров, Лаврик, Печунов

МПК: G06F 15/173

Метки: графов, моделирования

...в триггеры 2 матричной модели 1 графа заносится информация о топологии графа путем установки соответствующих триггеров 2 в единичное состояние, В единичное состояние устанавливаются триггеры 2 только тех узлов матричной модели 1, которым соответствует наличие в графе дуги. Триггеры 7, соответствующие вершинам, включаемым в первый подграф, устанавливаются в единичное состояние. Пуск устройства осуществляется путем подачи импульсного сигнала на вход 9. Этот сигнал устанавливает в нулевое состояние все арифметические устройства 8.Формирование значения числа связности для произвольной К-й вершины происходит путем параллельной передачи из узлов К-й строки матричной модели на К-й сумматор признаков наличия связей.этой вершины с другими...

Устройство для исследования путей в графе

Номер патента: 1348850

Опубликовано: 30.10.1987

МПК: G06F 15/173

Метки: графе, исследования, путей

...что обусловливает появление единичного сигнала на выходе элемента НЕ 4 и переход триггера 5 в состояние "1",На втором этапе вновь приводят20 устройство в исходное состояние, но регистры 1 О не обнуляются, а в матрицу 1 заносят информацию о топологии инвертированного графа, т.е. данные матрицы исходного графа, но транспортированные относительно неглавной диагонали.Затем пускают устройство и в счетчиках 8 повторно фиксируются наиболее ранние времена выполнения вершин ин 30 вертированного графа, которые в прямом графе соответствуют величинам максимальных путей из вершин графа в его конечную вершину. Однако в регистры 10 содержимое счетчиков 8 уже не ,записывается, так как единичный потенциал с первого разряда информационного счетчика 14...

Устройство для определения коэффициентов влияния параметров элементов на выходные параметры радиоэлектронных схем

Номер патента: 1348851

Опубликовано: 30.10.1987

Авторы: Андреев, Баранов, Валитов, Пестрякова

МПК: G06F 17/00

Метки: влияния, выходные, коэффициентов, параметров, параметры, радиоэлектронных, схем, элементов

...4 реагируУ5 ющего лишь на те номера сигналов, поступающих со счетчика 8, которые соответствуют установленным значениям данного канала варьирования. После сборки заданного варианта исследуемой 1 р схемы и задания значения параметра элемента схемы с выхода исследуемой схемы значение выходного параметра передается в АЦП 12, который преобразует измеренную аналоговую величину в цифровой код. После того как АЦП 12 преобразует измеренную аналоговую величину в цифровой код, он выдает сигнал "Конец преобразования", который поступает в счетчик 8, в котором увеличивается номер ячейки блока 3 памяти параметров элементов на единицу, Тот же сигнал Конец преобразования" поступает в схему 10 задержки, которая вырабатывает импульс, длительность...

Устройство для решения дифференциальных уравнений

Номер патента: 1348854

Опубликовано: 30.10.1987

Авторы: Кириллова, Петров, Спильный, Степанов

МПК: G06F 17/13

Метки: дифференциальных, решения, уравнений

...в блоки 8, - 8в решающие блоки 92 с индексами (1, 1),(п,2) (п,п). Для передачи инфор-,мации решающий блок 7 по шинам 1717 и 17 выдает в блок 5 соответственно информацию, сигнал ЗП и адрес. П 1 редзВеГлл нфорлция о ецгнл 1; свыхода элемента И 28 записывается врегистр 25 и одновреенно ио ппше 13"Запрос" поступает в решлкчпий блок92, который ерехолит нл подпрограмму чтения . 11 ля чтения блок 92 выс тлвляет адрес по шинам 14, который поступает нл вход депифрлтора 30, сигнал ЧТ по шине 14 Принимаемая информация с выхода регистра 25 черезключи 26 гоступает по шинлм 13 в решаюпий блок 92. К этому времени решающие блоки 92 с помощью блока 2 управления 2 подготовлены к расчету поля и после приема значений функциинл дополнителъшхр,нинах в...

Устройство для операций над матрицами

Номер патента: 1348855

Опубликовано: 30.10.1987

Автор: Белозерский

МПК: G06F 17/16

...что и реализуется благодаря введению в устройство блоков 2 деления.В исходном состоянии на входах нторых сомножителей всех блоков 3 всех столбцов матрицы, кроме последнего, присутствуют произвольные сигналы х х,х , . Следонательно, для реализации итерационной процедуры (4) отыскания собственного числаи собственного вектора х = (х,.хх ,х ) матрицы А, где Т - символ транспоциронания, в качестве начального приближения выбирается вектор х =(х,хо 1 о ф 2 сфф х , ,1)т. 1 а выходе сумматора 4 последнего вычислителя 1 последней строки матрицы при этом образуется сигнал который является первым приближением собственного числа, . На выходе сумматора 4 последнего вычислителя 1 1.-й строки,= 1п, образуется сигналих = а х + а1 с который...

Адаптивное устройство для вычисления среднего

Номер патента: 1348856

Опубликовано: 30.10.1987

МПК: G06F 17/18

Метки: адаптивное, вычисления, среднего

...третьей итерации в блоке Овччгслется ве:гцчцнд Б, = 3. Поэтомуцд цьходе устройства бу,)ет величина,Определяемая выражением2523 3Л =-Х +-Х 4+-Х88 Я Остальные итерации протекают анаЛОГЦЧЦО ОЦИСДЦЦЫМ.Блок О работает следующим обраЗОМ.В исходном состоянии регистр 14умцожцтель 13 и сумматор 12 и меютцд выходе нули, д блок 11 определения35четности имеет лобое исходное ( - 1или +1).Блок 11 определения четности, реализун)щггй операции ( - 1) ", и регистрлг14, являюгцйся .элементом памяти, изменяет свое состояние при изменениикдд числа л нд выходе счетчика 8(по Фронту кода),При первой итерации счетчик 8 сбрасывается в 0 (11, = 0). В умножите 45 ле 13) производящем операцию умножеци цд два, нулевое значение результдта поступает цд вход сумматора...

Устройство для обработки информационных массивов

Номер патента: 1348857

Опубликовано: 30.10.1987

Автор: Богумирский

МПК: G06F 17/27

Метки: информационных, массивов

...хсоР ржьо го с со( Г)х:1 ыл с тц с т сГ - эун)1 их с 1 етч иков4, Пр 1 Гонца,еип элемент 11 срвцецц ыддет си ,1;1, который 1 одлется цд 1 - и .Од .доме- та И 4, Если номер первого (51 дд, - нейшем опере,ного) элемента исходного мдсивд сс)постлвляГся (э Обрд ( - цом из группы регистров 8, - 8, т.есовпал с точностью до нулевых элементов обрлэцд), то ца всех входдх элемента И 4 появляются .игцдлы. Б результд Ге этого появляется сигцдлд выходе элемецтд И 4, Это говори о том, что очередцой элемент исходного масслва необходимо выдать цдвыход устройства,По импульсу ца третьем входе рдс пределителя 15 осуществляется ,д;- чд иэ устройства если это одтнерждается сигналом нл выходе элемента И 4) первого в дальнейшем очередного) элемента резуп...

Устройство для управления памятью видеоинформации

Номер патента: 1348860

Опубликовано: 30.10.1987

Авторы: Аверин, Адонин, Гоенко, Есионов, Лискин, Майстренко, Путятин

МПК: G06F 12/00, G06T 1/60

Метки: видеоинформации, памятью

...вход 13 устройстна подается сигнал 1которьп разрешает запись входной информации во второй блок 3 входных регистров и считывание данных иэ первого блока 2 входпх регистров, За время Т(фиг.б) аналогично Описаному осушестнляе гся второй цикл трехстороннего Обмена. Далее работа запоминающего устройства повторяется.Для того, чтобы устройство обработки могло записать или считать одповременно восемь элементов строки или столбца кадра, каждьп из любых восьми последовательно расположенных элементов должен находитьгя н одном из модулей 59 - 66 памяти, Осуществляется это следующим образом, Сигнал с первого адресного входа 11 устройства поступает на входы 43 - 50 выбора кристалла регистров 27 - 34 или 35 - 42, последовательно разрешая запись...

Устройство для отображения векторов на экране матричного индикатора

Номер патента: 1348898

Опубликовано: 30.10.1987

Авторы: Жидков, Нехай, Пригода

МПК: G06F 3/147, G09G 3/28

Метки: векторов, индикатора, матричного, отображения, экране

...16 и 20, а по координате Удешифраторы 17 и 21.Коды на дешифраторы 16, 20, 17и 21 поступают соответственно с вы 15 ходом счетчиков 3 и 4, причем надешифраторы 16 и 21 поступают соответствующие старшие половины разрядов счетчиков 3 и 4.Управление модуляцией осуществля 20 ет триггер 7 управления, сигнал свыхода которого поступает на входыузлов 22 и 23 усилителей, обеспечивающих подачу соответствующих напряжений на выбранные группы шин Х и 125 индикатора 1.МикроЭВМ 14 через блок 15 выдаеткоэффициент угла наклона вектора,равный произведению координат КХили КИ в зависимости от направленияхЗО осей координат, знаки приращений координат Х или лУ значение одного из приращений координат ьХ или(Л признак модуляции и сигнал блокировки импульсов...

Цифровой фильтр

Номер патента: 1348981

Опубликовано: 30.10.1987

Авторы: Каневский, Клименко, Котов

МПК: G06F 17/17, H03H 17/06

...во второй регистр блока 11.1 слагаемых принимается сумма И Х + И Х, + И Х , во второй регистр блока 11,2 слагаемых - сумма И Х + И Х + И Х, во второй регистр блока 11.3 слагаемых - сумма И Х + И Х, + И Х,В восьмом такте исходный отсчет Х з поступает на первые входы умножителей 9.1, 9,2 и 9,3, на вторыевходы которых подается содержимое(И, И и И ) блоков 8,1, 8,2 и 8.35 1 3коэффициентов. На выходах умножителей получаем произведения: И Хь зф И Х и И Х соответственноЭти4 3произведения поступают на первые входы сумматоров 10,. На второй вход сумматора 10.1 коммутатор 2 подает нуль, на второй вход сумматора 10,2 подается содержимое (И Х ) первого5регистра блока 11,1 слагаемых, на второй вход сумматора 10.3 подается сумма И Х + И Х из...

Трехканальное устройство для управления синхронизацией микропроцессорной системы

Номер патента: 1352475

Опубликовано: 15.11.1987

Авторы: Баженов, Болотенко, Карнаух, Тимонькин, Ткаченко, Топорков, Харченко

МПК: G06F 1/00

Метки: микропроцессорной, синхронизацией, системы, трехканальное

...его к установке в нулевоесостояние, в которое триггер 5 устанавливается по тактовому импульсу свыхода 22 блока 8 синхронизации.Одновременно сигнал переполненияс прямого выхода элемента 11 поступает на синхровход триггера 7, который под его действием устанавливается в нулевое состояние (фиг.5), Сигнал с выхода 45 триггера 7 используется в системе для фиксации приема данных.С приходом первого после описанного момента времени импульса с выхода18 блока 8 триггер 7 устанавливается в единичное состояние.Сигнал начала чтения кода команды с входа 31 канала стробируется сигналом с инверсного выхода триггера 6, который устанавливается в нулевое состояние при возбуждении входа 25 канала и выхода 18 блока 8, и поступает на третий вход...

Функциональный преобразователь

Номер патента: 1352476

Опубликовано: 15.11.1987

Авторы: Бульбанюк, Лысенко, Эпштейн, Якименко

МПК: G06F 1/02

Метки: функциональный

...а после считывания Б-го кода а управляющий выход "Конец" Формироателя 13 поступает импульс, прекраающий работу последующих блоков инФормационно-вычислительного комплекса, в состав которого входит функцио-,нальный генератор (также устанавливающии в исходное состояние регистры 5, 6, 17 сдвига). При этом, благодаря нулевому состоянию первого ивторого разрядов двухразрядного регистра 5 сдвига, закрывается прохождение тактовьж 1 импульсов на вход с формирователя 13 адреса.При следующем синхроимпульсе (тп = 5 - 2) работа функционального преобразователя аналогична описанной, но Б= Б и шаг аргумента дА = ш = 2, т.е. на выход мультиплексора 12 по каждому 1-му тактовому импульсу считывается соответствующий код С1 т.е. Со, С, С С 1, С, С, С ...

Устройство для отображения информации на экране электронно лучевой трубки

Номер патента: 1352477

Опубликовано: 15.11.1987

Авторы: Гаврилов, Зиновьев, Товба

МПК: G06F 3/153, G09G 1/28

Метки: информации, лучевой, отображения, трубки, экране, электронно

...таймер 40 генератора 39, который программируется микропроцессором 43.на заданную частоту передачи,Устройство работает в двух режимах". алфавитно-цифровом и графическом.В алфавитно-цифровом режиме микропроцессор 43 передает, данные от блока 38 и блока 37 (приемопередатчику).В графическом режиме микропроцессор 2477 843 выполняет функции, связанные сотображением графической информациипутем заполнения блоков памяти 57-60,которые доступны только во времягоризонтального и вертикального обратного хода луча и каждого нечетного цикла во время прямого хода луча,В каждом четном цикле прямого ходалуча осуществляется чтение данныхиз блоков 57-60 со сдвигом для последовательного вывода через блок 56памяти таблицы цветности, блок 28элементов ИЛИ на ЭЛТ...

Устройство для сравнения чисел

Номер патента: 1352478

Опубликовано: 15.11.1987

МПК: G06F 7/04

...на выход 13 устройства.Если А = В, то на выходах всех элементов И 1 и 2, элементов ИЛИ 3, 4, 5 - логический нуль, а логическая единица - на выходе 11 устройства,2478 2Формула изобретенияУстройство для сравнения чисел,содержащее первую группу из п элементов И, где и - разрядность сравнисваемых чисел, и первый элемент ИЛИ, причем вход прямого значения х-го разряда, где = 1 п, первого числа устройства и вход инверсного значения ь-го разряда второго числа устройства соединены соответственно с первым и вторым входами -го элемента И первой группы, выход которого соединен с -м входом первого элемента ИЛИ, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, оно содержит вторую группу элементов И, два элемента ИЛИ и элемент НЕ,...

Устройство для ввода информации

Номер патента: 1352479

Опубликовано: 15.11.1987

Авторы: Бобыльков, Глонти, Кривего

Метки: ввода, информации

...разряды, то в регистр 9 данных младший разряд размещается в левую секцию, затем более старшую и т.д.Младший разряд фиксируется в регистре 9 синхроимпульсом, поступающим с младшего выхода распределителя 4, затем следующий и т.д, старшийсинхроимпульс Фиксирует старший разРяд6Последний (старший) синхроимпульсслужит также синхросигналом для считывания данных с устройства.Синхроимпульсы формируются распределителем 4 путем подачи на его10 вход синхронизации синхроимпульсовс выхода элемента И 3, разрешаемогомикрокомандой У и стробируемого серией импульсов от генератора 6 импульсов,15 Таким образом, по переднему фронту основной серии импульсов генератора 6 в регистре адреса Фиксируетсяадрес ячейки блока памяти, содержащей соответствующую...

Логический элемент матричного умножителя

Номер патента: 1352480

Опубликовано: 15.11.1987

Автор: Алюшин

МПК: G06F 7/50

Метки: логический, матричного, умножителя, элемент

...и-транзистора 37, исток которого соединен с истоком тринадцатого-транзистора 36 и1352480 10 стоком шестнадцатого й - транзистора 39Устройство работает следующим образом.На шины 11,2, 40-43 поступают нулевой - второй разряды первого операнда, на шины 3,14, 44-47 поступают нулевой - второй разряды второго операнда.На выходной шине 5 формируется результат логической операции в соответствии с таблицей истинности. Формула изобретения Логический элемент матричного умножителя, содержащий шесть р-транзисторов, четыре п-транзистора, прямые и инверсные шины нулевого разряда первого и второго операндов, инверсную шину результата, шину питания, общую шину, затвор первого ртранзистора соединен с прямой шиной нулевого разряда первого...

Четырехзначный умножитель

Номер патента: 1352481

Опубликовано: 15.11.1987

Автор: Бобров

МПК: G06F 7/52

Метки: умножитель, четырехзначный

...О, 1, 2 в виде амплитуд тока всоответствии с амплитудами тока навыходе 17,Полное описание работы схемы четырехзначного умножителя сведено втабл,2,Работа умножителя поясняется напримере; где множимое равно трем, амножитель - двум (пятый справа столбец табл,2),И входов 1, 2 и 3 умножителя вытекают токи весом 2, 1 и 2 соответственно, а из входов 4 и 5 - весом 2и 3 соответственно. Следовательно,в базы детекторов Д 6, Д 7, Д 8 и Д 9втекают токи весом 1, О, О, 0 единиц. Следовательно, входной отражатель О 4 закрыт.Таким образом, из входных вентилей открыт только один детектор Д 6,который отключает на землю токи инжекторов 012 и 013. Поэтому отражатель 015 открыт и отсасывает из инжекторов отражателей 010 и 011 подве единицы тока.Открытые...

Умножитель частоты

Номер патента: 1352482

Опубликовано: 15.11.1987

Авторы: Бутузов, Герасимов, Караваев, Ячейкин

МПК: G06F 7/68

Метки: умножитель, частоты

...которого соединены соответственно с входами первой группы сумматора 13, входы второй группы которого соединены соответственно с шиной .12 введения поправки, разрядные выходы сумматора 13 соединены соответственно с входами вторых групп первого мультиплексора 6 и схемы 11сравнения, выход которой соединен синформационным входом триггера 14, выход которого соединен с вторым входом 55элемента ИЛИ 7 и с управляющим входомвторого мультиплексора 10, выход элемента ИЛИ 7 соединен с входом разрешения записи регистра 8, выход втогде И - поправка при увеличении пеириода входной импульснойпоследовательности, вносимая в коэффициент деленияделителя 9 частоты,При отсутствии сигнала на выходе схемы 11 сравнения на выходе сумматора 13...

Устройство для умножения чисел в модулярной системе счисления

Номер патента: 1352483

Опубликовано: 15.11.1987

Авторы: Коляда, Ревинский, Селянинов, Чернявский

МПК: G06F 7/72

Метки: модулярной, системе, счисления, умножения, чисел

...информационный вход первого блока 14 мультиплексоров поступает в первый блок 19 вычисления интервального индекса числа Где в течение Очередных Т так О тов, считая текущий, в соответствии с формулой (3) будет вычислен машинный интервальный индекс 1(В) числа В, модулярньй код (,",л,) подается также на третий адресный вход блока 15 памяти, на второй и первый входы разрешения выдачи которого с второго и первоГО выходов 631 оеа 8 поступают11 3.М соответственно сигнаы д,= Ои = "1", В результате 1.а первом и (150 +1)-ом выходах блока 5 памяти сформируются соответственно наборы вычеК) в согокупности передаются на трет.й вход блока 3 вычисленияинтервального идакса произведения,на второй вход которого подается модулярный код числа с выхода...

Программируемый контроллер

Номер патента: 1352484

Опубликовано: 15.11.1987

МПК: G06F 9/00

Метки: контроллер, программируемый

...может инициализироваться по положительному фронту импульсов с генератора 5,а запуск одновибраторов группы 6 -по отрицательному фронту. Перед началом работы устройства через вход 7 начальной установки на четвертый стробирующий вход дешифратора 3, запрещающий включение его выходов, подается импульс, длительность которого превышает:максимально возможное время, необходимое для вычисления кода микрооперации. В таблице представлено назначение полей регистра 2 микрокоманд,з 135Количество А информационных каналов мультиплексора 4, разрядность Ввходом блока памяти и длина С микрокоманды"(см. таблицу) связаны соотношениемА=М+И;С=Тор, АБ,В = С+1,где М - разрядность входа 8 устройства;1 - разрядность выхода 9 устройства;Б - максимальная входимость...

Микропрограммный автомат

Номер патента: 1352485

Опубликовано: 15.11.1987

Авторы: Вислович, Куклин, Яковлев

Метки: автомат, микропрограммный

...регистра сдвига в предыдущем цикле работы автомата и хранящийся в регистре блока синхронизации, сравнивается с актуальным вектором. В случае, если хотя бы один из актуальных сигналов изменился по сравнению с предыдущим циклом, то генератор импульсов группы, поставленный в соответствие этому сигналу, запускается.Время Т блокировки определяется импульсом того из запустившихся генераторов импульсов группы, который имеет максимальную длительность, В случае, если актуальный вектор входных сигналов совпадает с вектором входных сигналов предыдущего цикла, то ни один из генераторов импульсов группы не запускаетсяТогда время Т блокировки определяется длительностью импульса, выдаваемого первым генератором импульсов. Генератор синхроимпульсов...