Устройство для формирования сигналов прерывания при отладке программ

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1348841

Авторы: Богданова, Будовский, Бурковский, Гольдберг

Текст

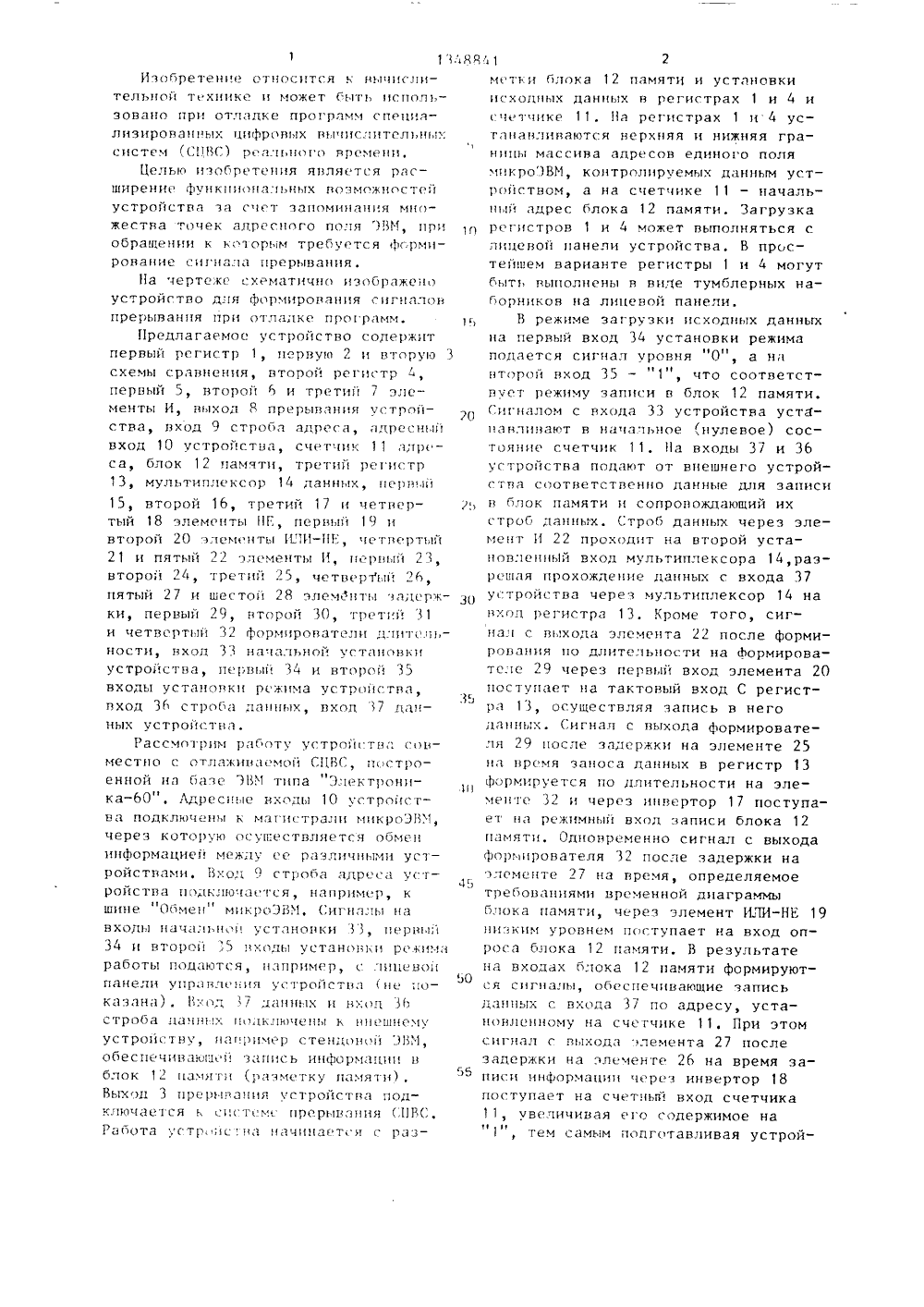

СОЮЗ СОВЕТСКИСОЦИА ЛИСТ ИЧЕСК)4 С 06 Р 11 НИЯОБР ОПИСАН ТЕПЬСТВ ил. ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТ АВТОРСКОМУ С(56) Авторское свидетельство СССР У 962945, кл. С 06 Р 11/28, 1980.Авторское свидетельство СССР У 1185343, кл. С 60 Р 11/28, 1984, (54) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ СИГНАЛОВ ПРЕРЫВАНИЯ ПРИ ОТЛАПКЕ ПРОГРАММ(57) Изобретение относится к цифро вой вычислительной технике и предназначено для использования при от ладке программ специализированных вычислительных систем реального времени. Цель изобретения - расширение функциональных возможностейустройства. Цель достигается тем,что в устройство, содержащее первый1, второй 4 регистры, счетчик 11 адреса, первую 2 и вторую 3 схемы сравнения, первый 5, второй 6 и третий 7элементы И, введены блок 12 памяти,четвертый регистр 13, мультиплексорданных 14, первый 15, второй 16,третий 17 и четвертый 18 элементыНЕ, первый 19 и второй 20 элементыИЛИ-НЕ, четвертый 21 и пятый 22 элементы И, первый 23, второй 24, третий 25, четвертый 26, пятый 27 ивестой 28 элементы задержки, а также первый 29, второй 30, третий 31и четвертый 32 формирователи длительности с соответствующими связями.Изобретение отцосится к вычислительной технике и может быть использовацо при отлдпке программ спцидлизировацццх цифровых вьцисс 1 тел цгх систем (СЦВС) рсд.ьцого врсмци,Целью изоГретеция являстс.я рдс - ширени фуцкциоцд:ьццх позможностс й устройства зд счет запоминания множества точек адресного по:я ЭГ 1, при обращеции к которьм требуется формировацие сигнала црерьвдия.На черте,ке схсматичцо изображеноустройство д:я формирования гигцд:он 1 и прерывания при отладке программ, 1)Предлагаемое устройство содержитпервый регистр 1, первую 2 и вторую 3схемы с.равнения, второй регистрпервый 5, второй 6 и третий 7 элементы И, выход 8 прерывания устройства, вход 9 стробд адрсд, адресныйвход 10 устройства, счетчик 11 ддрс -са, блок 12 памяти, третий регистр13, мультиплексор 14 панццх, перльй15, второй 16, третий 17 и четвертый 18 элемсцты НЕ, перинй 19 ивторой 20 элем цты ПИ-НЕ, четвертый21 и пятый 22 элементы И, церни 23,второй 24, третий 25, четвсртый 26,пятый 27 и шестой 28 элемент 1 ддс ржки, первый 29, второй 30, трст.и 1и четверт 1 й 32 формирователи д:итс льности, вход 33 ндчдьной установкиустройстсза, первый 34 и второи 35входы устацс)вки режима устроиствд,5вход 36 строГд ддцццх, вхоп 7 пдц -ных устрой:тнд,Рассмотрим работу устройтвд совместно с отлд)сисдс мой СЦВС, поп тровенной цд базе Э 1 Г типаЭ.ектроника". Лдресце входы 10 устроиствд подключены к магистрали ь 1 кроЭГ 1,через которую осуп:ествляется обмен1 цформацие 11 между с.е различными устройствами, Вход 9 стробд ддрсд ус.т -,1 5ройства пс)дключдстся, например, кшинеОбме" микроЭБГ 1, Сигцд:ц ндвходы цдчсс).цо установки ., црвый34 и второи 5 входы установки ржимаработы подаются, цдпримр, с .ицево 150панели упр,влс ция устройства (не новка.зднд), Вход 7 ддцццх и нх)п 3)строба паццих ц)1 ьл)чеы ь внешнемуустроистну, цдцримс р стецпонои ЭГ 1,обеспечивдющс й зсцись ицформдци вблок 1 цдм)т (разметку памяти) .) 55Выхс)п 3 11 ре)ы 1)д 1 ия устройстед подкп 10 чдегся к 11 тс.мс прерыгдея СПВС,Работа ус тс:. 1 д цдчицдтя с рдз -мтки блока 12 памяти и установки исхопцых данцых в регистрах 1 и 4 и четчике 11, Нд регистрах 1 и 4 усгдцанливаются верхняя и нижняя грангисы массива адресов единого поля ьикроЭВГ 1, контролируемых данным устрс)йством, а на счетчике 11 - цачальццй адрес блока 12 памяти. Загрузка регистров 1 и 4 может выполняться с лицевой панели устройства. В простейшем варианте регистры 1 и 4 могут быть выполнены в виде тумблерных наСорников на лицевой панели.В режиме загрузки исходных данных ца первый вход 34 установки режима подается сигнал уровня 0 , а нд второй вход 35 - "1", что соответствут режиму записи в блок 12 памяти. Сигналом с входа 33 устройства уста длизают в ндчд.ьцое,нулевое) сосстояцие счетчик 11. На входы 37 и 36 устройства подают от вцешнего устройства соответственно данные для записи в Спок памяти и сопровождающий их строб данных. Строб данных через элемент И 22 проходит на второй устацовлеццьй вход мультиплексора 14,разрс.шдя прохождение данных с входа 37 устройства через мультиплексор 14 на цхоп регистра 13. Кроме того, сигнал с вьхода элемента 22 после формирования по длите.ьцости на формировате:е 29 через первый вход элемента 20 поступает ца тактовый вход С регистра 13, осуществляя запись в него дднц,х, Сигнал с выхода формирователя 29 после задержки на элементе 25 цд врсмя заноса данных в регистр 13 формируется по длительности на элементе 32 и через ицвертор 17 поступает цд режимный вход записи блока 12 памяти, Одновременно сигнал с выхода форзирователя 32 после задержки на элементе 27 нд время, определяемое требовдциями временной диаграммы блока памяти, через элемент ИЛИ-НЕ 19 низким уровнем поступает на вход опроса блока 12 памяти. В результате нд входах б.ока 12 памяти формируютс.я сигналы, обеспечивающие запись пдццых с входа 37 по адресу, установленному на счетчике 11. При этом сигнал с выхода )лемента 27 после задержки на племен ге 26 на время записи информации через инвертор 18 поступает на счтцый вход счетчика 11, увличивая го содержимое на 1, т ем с амым и о и г о т авлив ая устройствс к записи следующего слова данных. Обращаясь последовательно к ячейкам блока 12, помечаем, например, путем записи "1" адреса единого поля ЭВМ, при обращении к которым необходимо осуществить прерывание отлаживаемой программы, При этом, если адресный массив блока 12 меньше полного массива адресов микроЭВМ, то адрес памяти в адресном поле ЭВМ определяется регистрами 1 и 4, задающими положение массива блока 12 памяти в адресном поле ЭВМ, и составлением счетчика 11 регистра, в котором фиксируется некоторая младшая часть адреса, сформированного в магистрали ЭВМ.После заноса исходных данных и разметки блока 12 на входе 34 устанавливается потенциал высокого уровя "1", а на входе 35 - низкого уровня 0", что соответствует режиму отладки программ. В результате разрешается прохождение строба адреса с выхода 9 через элемент 21. Формируется потенциал низкого уровня на втором установочном входе мультиплексора 14, запрещающий прохождение в устройство данных с входа 37. Через инвертор 16 на первый установочный вход мультиплексора 14 поступает потенциал высокого уровня, разрешающий прохождение информации с выхода блока 12 на регистр 13. В режиме отладки при выполнении микроЭВМ некоторой программы строб адрес с входа 9 устройства через элемент 21 и инвертор 15 поступает на установочный вход С счетчика 11, занося в него состояние магистрали, т.е. код адреса, с адресного входа 10 устройстваПотенциал низкого уровня с выхода элемента 22 через элементы 29, 25, 32 и 17 поступает сигналом высокого уровня на вход записи блока 12 памяти, Положительный сигнал с выхода элемента 21 задерживается на элементе 23 на время, необходимое для записи в счетчик 11 адреса с входа 10, и после формирования по длительности на формирователе 30 через элемент 19 отрицательным импульсом поступает на вход опроса блока 12 памяти. Сочетание потенциала высокого уровня на режимном входе и низкого уровня на входе опроса соответствует режиму считывания информации для блока 12 на вход муль 45Устройство для формирования сигф налов прерывания при отладке программ, содержащее первый и второй регистры, счетчик адреса, первую и вто,Рую схемы сравнения, первый, второй 50и третий элементы И, причем адресный 55 5 10 1 с О 25 30 35 10 типлексора 14 и далее на вход регисра 13. Сигнал с выхода элемента 21задерживается с помощью элемента 24на время, необходимое для считыванияинформации из блока 12, формируетсяпо длительности на элементе 31 ичерез элемент 30 поступает на установочный вход С регистра 13, фиксируя в нем считанную из памяти информацию. При этом, если иэ памяти считана единичная информация, то напервом входе элемента 7 будет соответствующий логический сигнал. Уровень сигнала на втором входе определяется текущим опросом в магистрали и состоянием регистров 1 и 4. Текущий адрес с входов 10 устройс гвапоступает на первые входы схем 2 и 3сравнения. На выходе схемы 2 формируется положительный потенциал, еслитекущий адрес меньше адреса верхней границы, установленного на регистре 1, а на выходе схемы 3 - еслибольше адреса нижней границы, фиксированного на регистре 4. На выходеэлемента И 5 будет положительный потенциал, если текущий адрес находитсяв зоне, ограниченной содержимым регистров 1 и 4, В этом случае черезэлемент 6 проходит строб адреса свхода 9, задерживается на элементе 28на время считывания информации изблока 12 памяти и поступает на второйвход элемента 7. В результате вырабатывается сигнал прерывания на выходе8 устройства, Если текущий адрес непринадлежит массиву, заданному регистрами 1 и 4, или из блока 12 памятисчитана нулевая информация, то сигналпрерывания на выходе 8 устройства неформируется. Формула изобретения вход устроиства соединен с входамипервых сравниваемых чисел первой ивторой схем сравнения, выходы первого и второго регистров соединены с входами вторых сравниваемых чисел соответственно первой и второй схем сравнения, выходы равенства которых соединены соответственно с первым и1348841 Составитель И, СигаловТехред А.Кравчук Корректор М.Пожо Редактор Е.Копча Заказ 4803/49 Тираж 670 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская наб., д. 4/53Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 вторым входами первого элемента И,выход первого элемента И соединенс первым входом второго элемента И,вход строба адреса устройства соединен с вторым входом второго элемента И, о т л и ч а ю щ е е с ятем, что, с целью расширения функциональных возможностей устройства засчет запоминания множества точек адресного поля ЭВМ, при обращении ккоторым требуется формирование сигнала прерывания, в устройство введены блок памяти, третий регистр,мультиплексор данных, первый, второй, третий и четвертый элементы НЕ,первый и второй элементы ИЛИ-НЕ,четвертый и пятый элементы И, шестьэлементов задержки, четыре формирователя длительности, причем входы строба адреса и первый вход установкирежима устройства соединены соответственно с первым и вторым входамитретьего элемента И, выход которогосоединен через последовательно соединенные первый элемент задержки ипервый формирователь длительности спервым входом первого элемента ИЛИ-НЕ,через последовательно соединейныевторой элемент задержки и второй формирователь длительности - с первымвходом второго элемента ИЛИ-НЕ и через первый элемент НЕ - с тактовымвходом счетчика адреса, адресный иустановочный входы устройства соединены соответственно с информационнымвходом и входом начальной установкисчетчика адреса, выход которого соединен с адресным входом блока памяти, вход строба данных и второй входустановки режима устройства соединены соответственно с первым и вторыми входами четвертого элемента И, выходкоторого соединен с первым управляющим входом и через второй элементНЕ - со вторым управляющим входоммультиплексора данных, выход которогосоединен с информационным входом третьего регистра, выход четвертогоэлемента И через третий формировательдлительности соединен с входом третьего элемента задержки и вторым входом второго элемента ИЛИ-НЕ, выходкоторого соединен с тактовым входомтретьего регистра, выход третьегоэлемента задержки соединен черезчетвертый формирователь длительности с входом третьего элемента НЕ,через четвертый элемент задержки -с вторым входом первого элементаИЛИ-НЕ и через пятый элемент задержки - с входом четвертого элемента НЕ,выход которого соединен со счетнымвходом счетчика адреса, вход данныхустройства соединен с первым информационным входом мультиплексора данных,группа разрядных выходов третьегорегистра соединена с группой информационных входов блока памяти ис группой входов пятого элемента И,выход которого является выходом прерывания устройства, выход второгоэлемента И через шестой элемент задержки соединен со стробирующим входом пятого элемента И, выходы третьего элемента НЕ и первого элементаИЛИ-НЕ соединены соответственно свходами записи и обращения блока памяти, выход которого соединен с вторым информационным входом мультиплексора данных.

СмотретьЗаявка

4073998, 04.06.1986

ПРЕДПРИЯТИЕ ПЯ Г-4152

БУРКОВСКИЙ ИГОРЬ ВЛАДИМИРОВИЧ, БУДОВСКИЙ ЯКОВ МОИСЕЕВИЧ, БОГДАНОВА КИРА ВИКТОРОВНА, ГОЛЬДБЕРГ ИКАР ВЕНИАМИНОВИЧ

МПК / Метки

МПК: G06F 11/28

Метки: отладке, прерывания, программ, сигналов, формирования

Опубликовано: 30.10.1987

Код ссылки

<a href="https://patents.su/4-1348841-ustrojjstvo-dlya-formirovaniya-signalov-preryvaniya-pri-otladke-programm.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для формирования сигналов прерывания при отладке программ</a>

Предыдущий патент: Устройство для отладки программ

Следующий патент: Устройство для сопряжения внешних устройств с накопителем на магнитной ленте

Случайный патент: Способ неразрушающего контроля намагничивающихся материалов