Патенты с меткой «интегральных»

Способ лазерной подгонки пленочных элементов интегральных схем и устройство для его осуществления

Номер патента: 1085425

Опубликовано: 23.01.1985

Авторы: Заика, Кравченко, Лантухов, Попов

МПК: H01C 17/242

Метки: интегральных, лазерной, пленочных, подгонки, схем, элементов

...(при стабильной мощности пучков лазерного излучения, обеспечивающей постоянную ширину реза)и предлагаемым, приводящим к монотонному уменьшению ширины реза в про 40цессе подгонки.Установлено, что при предлагаемомспособе минимальный воспроизводимыйвыжженный диаметр пятна на поверхности резистивной пленки в,3-4 разаменьше начального диаметра,В результате подгонки было установлено, что относительная погрешность подгонки известным способом при диаметре выжженного пятна 50 100 мкм и шаге пятен 50 мкм (502 перекрытие) составила (1-2)Х, при уменьшении шага до 10 мкм - 0,257 при резе переменной ширины (предлагаемым способом) - 0,0252. 55 Таким образом, точность подгонкиповысилась на порядок. 4Для подгонки пленочных элементов обычно используют...

Контактное устройство для контроля интегральных схем

Номер патента: 1137549

Опубликовано: 30.01.1985

Авторы: Гавриков, Кононов, Махаев, Миненков, Чистов, Шпаков

МПК: H01R 13/62, H05K 1/11

Метки: интегральных, контактное, схем

...не позволяет перестраивать устройство на проверку микросхемы другого типоразмера.Целью изобретения является повышение удобства эксплуатации при автоматическом процессе контроля. )Поставленная цель достигается тем, что контактное устройство для контроля интегральных схем, содержащее корпус с основанием и размещенными в корпусе двумя рядами пружинных контактов, между которыми расположен механизм фиксации интегральной схемы с базовым выступом и механизм перемещения контактов, механизм фиксации интегральной схемы выполнен в виде ползуна, установленного в корпусе с возможностью перемешения вдоль продольной оси устройстна, и рычага, один конец которого шарнирно соединен с ползуномр а другой конец подпружинен относительно основания корпуса и...

Устройство для вырубки интегральных схем и укладки их в спутники

Номер патента: 1140857

Опубликовано: 23.02.1985

МПК: B21D 28/14

Метки: вырубки, интегральных, спутники, схем, укладки

...спутниками, механизм подачи заготовок снабжен кареткой, установленной в неподвижной части штампа с возможностью возвратно-поступательного перемещения в направляющих планках, и промежуточным механизмом, установленным с возможностью взаимодействия с кареткой и пуансоном.При этом промежуточный механизм выполнен в виде копира, жестко соединенного с пуансоном, и двуплечего рычага, установленного в неподвижной части на оси с возможностью качения, один конец рычага подпружинен и выполнен с возможностью взаимодействия с кареткой, а другой - с копиром.На фиг. 1 изображено предлагаемое устройство в момент нахождения каретки над зеркалом матрицы (исходное положение), общий вид; на фиг. 2 - положение каретки в момент вырубки; на фиг. 3 - сечение А-А...

Раствор для травления выводов интегральных микросхем

Номер патента: 1142527

Опубликовано: 28.02.1985

Авторы: Голомшток, Левчук, Мартинович, Рухля

МПК: C09K 13/00, C23F 1/00

Метки: выводов, интегральных, микросхем, раствор, травления

...2-5Вода, л До 1в течение 3-4 мин с наложениемультразвука при 40-50 С, промыовают в горячей проточной воде Ф 2,110Удельное объемное сопротивлениепластмассы должно быть высоким(не менее 10 Ом.см согласно тре 4 Ф 527 4бованиям ГОСТ 64332-71) и его снижение недопустимо, поскольку возникает опасность короткого замыкания между выводами ИМС.Адгезию покрытия олово-свинец определяют. по методу термоудара, согласно которому ИМС выдерживают сначала в нагретом до 250-265 С припое ПОСв течение 5 мин, после чего ИМС погружают в холодную (16- 25 С) воду на 5 мин. Послепровеодения 5 циклов термоудара покрытие олово-свинец просматривают в микроскоп МВСпри увеличении 32 раза. Адгезия покрытия олово-свинец к выводам ИМС считается хорошей, если...

Стекло для интегральных схем

Номер патента: 1143702

Опубликовано: 07.03.1985

Авторы: Ермолаева, Кошелев, Петрова

МПК: C03C 3/085

Метки: интегральных, стекло, схем

...проводят в индукционной печи в платинородиевом тигле при 1700 С с выдержкой 10 ч после расплавления шихты. Выработку стекол проводят в виде гранулята путем отливки расплава стекломассы в дистиллированную воду. Лля измерения КТЛР и Г отливают образцы в виде штабиков (50 х 5 х 5 мм).; Гранулят стекла измельчают в яшмовом барабане на планетарной мельнице до удельной поверхности 5000 .см/г.Формирование стекловидных слоев на кремниевых пластинах осуществляют методом ВЧ магнетронного распыления. При распылении используют мишень из порошкового стекла, формирование которой осуществляют путем равномерного нанесения порошка стекла на металлический катод (диаметр 130 мм). ,Толщина слоя стекла составляет 4 мм.Формирование стекловидных пленок...

Устройство для контроля интегральных микросхем памяти

Номер патента: 1144154

Опубликовано: 07.03.1985

Авторы: Бохан, Дербунович, Кимарский, Кузовлев, Либерг, Черняк

МПК: G11C 29/00

Метки: интегральных, микросхем, памяти

...с выходами генераторовимпульсов и одним из выходов пер-.вого блока управления, выход второ- З 0го формирователя управляющих сигналов является первым выходом устройства, первым входом которогоявляется вход одного из генераторовимпульсов, программируемый блок 35питания и датчик температуры, выходы которых являются соответственно вторым и третьим выходами устройства, триггер, выход которогоподключен к входу третьего формирователя управляющих сигналов,пульт управления, соединенный с первым и вторым блоками управления,первый счетчик и группы счетчиков,одни из выходов которых подключены соответственно к управляющимвходам первого и второго формирователей управляющих сигналов, программируемого блока питания и датчикатемпературы и к...

Устройство для автоматического контроля интегральных схем

Номер патента: 1145311

Опубликовано: 15.03.1985

Авторы: Белогуб, Бровко, Еремин

МПК: G01R 31/303

Метки: интегральных, схем

...входной резистор соединен с выходом сумматора и через резистор обратной связи - с выходом второго повторителя, а выход через третий ключ - с первым выводом запоминающего конденсатора, второй вывод которого соединен с общей шиной,М первый вывод запоминающего,конденсатора соединен с входом второго по- . вторителя, выход которого через чет 311 4вертый ключ и суммирующий реэисторсоединен с тРетьим входом компарато.ра, а управляющие входы третьегои четвертого ключей подключены кседьмому и восьмому выходам задатчика кодов и команд,На чертеже представлена блок-схемаустройства.Устройство содержит задатчик 1кодов и команд, источник 2 опорногонапряжения, подключенный к первому.входу программируемого источника 3напряжения, который...

Формирователь сигнала напряжения смещения подложки для интегральных схем

Номер патента: 1149311

Опубликовано: 07.04.1985

Авторы: Лушников, Минков, Однолько, Романов

МПК: G11C 11/40

Метки: интегральных, подложки, сигнала, смещения, схем, формирователь

...подключены соответственно к первой 12, второй 15 и третьей 16 входным шинам, затвор погрузочного транзистора 8 соединен с третьей входной шиной 16, затвор и сток другого порогового ф транзистора 6 соединен с истоком нагрузочного транзистора 8,Формирователь сигнала напряжения смещения подложки работает при подаче последовательности импульсов напряжения одинаковой частоты на входные шины 12, 15, 16 с временными соотношениями, указанными на фиг. 2. Начала фронтов на первой и второй входных шинах 12 и 15 совпадают, фазы противоположны.Импульс на третьей входной шине 16 опережает импульс на первой входной шине 2 на время 1, равное 0,25 - 0,1 от периода следования импульсов.Импульсы должны иметь амплитуду, превышающую по крайней мере в...

Способ зондового контроля интегральных микросхем на пластине

Номер патента: 944486

Опубликовано: 15.04.1985

Авторы: Белявский, Епифанов, Завало, Кононов, Ступень, Филиппович, Ярош

МПК: H05K 1/18

Метки: зондового, интегральных, микросхем, пластине

...положение и на шаг, для каждой микросхемы определяют расстояние между контактными площадками и зонда ми, перемещают пластину на это расстояние и останавливают, затем пере мещают ее в положение контроля.1 электрических параметров микросхемы 1 пластина опускается в исходное положение на величину г : Ее =Л +д 2 + 21 1 Н1 0 й (фиг, 1) и перемещается на один шаг (фиг. 4).В это время для микросхемы 2, контроль которой будет осуществлять" ся второй, с помощью датчика 5 положения определяется величина разновысотности по отношецию к микросхеме 1 аХ . После этого пластина поднимается до соприкосновения зондов с контактными площадками микросхемы 2 на Величину 2 -дя =1,Фд" 17 ц остаС навливает св (фи. 5 1.20 3 94448Дальнейший подъем пластины...

Устройство для программного управления процессом сборки интегральных микросхем

Номер патента: 1151928

Опубликовано: 23.04.1985

МПК: G05B 19/18, G05B 19/425

Метки: интегральных, микросхем, программного, процессом, сборки

...С выхода блока 3 задания команд (фиг. 1) на вход блока 5 программ поступает команда Выбор адреса. С выхода блока 5 программ на вход блока 6 сравнения поступает значение координаты следующей контактной площадки кристалла. На выходе блока 6 сравнения появляется логический сигнал высокого уровня, соответствующий команде Старт, который проходит через компаратор 7 на первый вход блока шагового привода 9. Одновременно с выхода блока 3 задания команд через компаратор 8 на вход блока 9 шагового привода поступает логический сигнал Направление. Блок 9 шагового привода производит совмещение инструмента и следующей контактной площадки кристалла, В это время на вход счетчика 4 поступают импульсы тактового генератора блока 9 шагового...

Способ изготовления мдп интегральных схем

Номер патента: 719398

Опубликовано: 07.05.1985

Авторы: Лепилин, Самыгина, Столичнов, Феофанова, Черняк

МПК: H01L 21/82

Метки: интегральных, мдп, схем

...второй и третьей фотолитографических операциях травления в среднем в два раза ниже, чемна первой, Помимо сказанного, лучшие результаты на первом травлении 10обусловлены возможностью визуального контроля травления по уменьшениюдиаметра пятна, соответствующегоневытравленной области пластины,При исчезновении пятна травление 15прекращают, вынимая пластину изтравителя, Яа следующих операцияхэта возможность отсутствует, таккак на пластине уже имеется рисунокпервого травления.Целью изобретения является снижение трудоемкости изготовленияи увеличение выхода годных интегральных схем.Поставленная цель достигается 25тем, что все окна в проводящем слоеполикристаллического кремния. вскрывают одновременно в одной операциифотолитографического...

Устройство для измерения сопротивлений омических контактов интегральных схем

Номер патента: 1164613

Опубликовано: 30.06.1985

Авторы: Галкина, Кочан, Новосядлый, Пеленский, Саваневский, Собенко

МПК: G01R 17/10

Метки: интегральных, контактов, омических, сопротивлений, схем

...элемент с тремя наборами дискретныхрезисторов, причем два из них обра.зуют первое и седьмое плечи семиплечего моста, а третий - включенпоследовательно с источником питания и регулируемым резистором в диагональ питания семиплечего моста,а зажимы для подключения объектаизмерения соединены соответственнос общим выводом третьего и шестогоплеч моста, другим выводом индика 1тора, первым плечом с седьмымплечом.В качестве индикатора может бытьприменен цифровой вольтметр,На чертеже изображена схемаустройства, Устройство содержитнабор дискретных резисторов 1 первого плеча семиплечего моста, трехплатный уравновешивающий элемент 2,набор дискретных резисторов 3 седьмого плеча, набор дискретных резисторов 4 цепи питания моста, зонды...

Устройство для перемещения и контактирования интегральных схем в климатической камере

Номер патента: 1166199

Опубликовано: 07.07.1985

МПК: H01L 21/66

Метки: интегральных, камере, климатической, контактирования, перемещения, схем

...шарнирно соединенных между собой рычагов 26, На транспортирующем роторе 15 жестко закреплено зубчатое колесо 27, которое находится в зацеплении с шестерней 28, на валу 29 которой жестко установлен мальтийский механизм 30. Поводок 31 последнего жестко установлено на кулачковом валу 21, который своим нижним концом выведен на габариты климатической камеры 1 и посредством карданного вала 7 соединен с однооборотным редуктором 4 (фиг. 1) . Транспортирующий ротор 15 установлен на кулачковом валу 21 с возможностью вращения. Кулачки 22 с толкателями 23 образуют механизм подачи интегральных схем, а мальтийский механизм10 15 20 25 30 35 40 45 50 55 При дальнейшем повороте ведомого вала 21 поводок 31 входит в паз мальтийского механизма 30,...

Устройство для вырубки интегральных схем

Номер патента: 1169767

Опубликовано: 30.07.1985

МПК: B21D 28/14, B21D 43/00, B30B 15/30 ...

Метки: вырубки, интегральных, схем

...фиксации; на фиг6 - то же, вид сверху; на фиг. 7 - то же, вид сбоку; на фиг. 8 - планки для ориен тации интегральных схем в многоместной кассете и механизме подачи; на фиг. 9 - схема фиксации интегральной схемы в кассете; на фиг. 10 - много" местная кассета для выводных рамок; 25 на фиг. 11 - схема работы узла,фиксации многоместной кассеты в момент неправильной установки кассеты, на фиг. 12 - то же, в момент правильной установки кассеты. 30Устройство для вырубки интегральных схем содержит штамп 1, включающий в себя верхнюю плиту 2 с вырубным пуансоном 3 и нижний штамп 4 с матрицей 5 и лотком 6 установки кассет 7 на матрице 5. Лоток 6.подвижен в направлении, параллельномосидавления штампа 1, и связан рычагом 8 с кулачком 9,...

Цифровой измеритель интегральных параметров электрических импульсов

Номер патента: 1170380

Опубликовано: 30.07.1985

Авторы: Андреева, Мусин, Филатов

МПК: G01R 29/02

Метки: измеритель, импульсов, интегральных, параметров, цифровой, электрических

...преобразователя, выходом связанного с первым входом 1 О 15 20 25 30 35 40 вычислительного блока, первый выходкоторого подключен к входу блокаиндикации, а второй выход-к второмувходу аналого"цифрового преобразо вателя и первому входу блока синхронизации, снабжен двумя регулируемыми полосовыми фильтрами сигнальные входы которых подключены к выходам предусилителей, выходы-к сигнальным входам аналоговых запоминяющих блоков, а управляющие входы-к второму выходу интегрального преобразователя импульсов с квадратичной характеристикой и второму входу вычислительного блока, третий выход которого связан с третьим входом коммутатора каналов, причем второй вход блока синхронизации соединен с выходом второго регулируемого полосового фильтра.На...

Цифровой измеритель интегральных параметров электрических импульсов

Номер патента: 1171729

Опубликовано: 07.08.1985

МПК: G01R 29/02

Метки: измеритель, импульсов, интегральных, параметров, цифровой, электрических

...к входувторого нормирующего предусилителя,выход которого связан с первым входом блока синхронизации, вторым входом соединенного с четвертым выходом вычислительного. блока и вторым входом первого АЦП, а выходом - с управляющими входами первого и второ. го аналоговых запоминающих блЬков, сигнальные входы которых подключены к выходам первого и второго нормирующих предусилителей,а выходы к входам .коммутатора каналов, выход которого связан с первым входом первого АЦП, выходом соединенного с первым входом вычислительного блока, выод которого подключен к входу. блока индикации, снабжен дополнительным интегральным преобразователем импульсов с линейной характеристикой, конденсатором, активным нормирующим фильтром нижних частот, третьим...

Устройство для контроля интегральных схем

Номер патента: 1171795

Опубликовано: 07.08.1985

Автор: Гаврилов

МПК: G01R 31/28, G06F 11/30

Метки: интегральных, схем

...через элемент И 14 сгенератора 4 тактовых импульсов на 4 Осчетчик 13. 795 4В режиме функциональных испытаний блок 34 ключей управляется признаком входа, подаваемым на инвертор 41. Запрет входа соответствует единице на входе инвертора 41, т.е. "нулям" на входах элементов И 35 и 36. Разрешение входных воздействий осуществляется подачей нуля на инвертор 41 запрещая прохождение строба на соответствующий канал многоканального компаратора 3.При этом на элементы И 35 и 36 поступает разрешение единицей с инвертора 41 через элемент ИЛИ 37. Ключи 39 и 40 находятся в этом случае в противоположных состояниях. Ключ 39 открыт единицей с элемента И 35, а ключ 40 эакрьгг нулем с элемента И 36, так как инвертор 38 инвертирует единицу с выхода элемента И...

Способ настройки интегральных тензометрических мостов

Номер патента: 1174739

Опубликовано: 23.08.1985

Авторы: Белозубов, Жучков, Соснин, Тихоненков

МПК: G01B 7/16

Метки: интегральных, мостов, настройки, тензометрических

...температурной погрешности в широком диапазоне температур.На фиг. 1 представлен интегральный тензометрический мост с термочувствительным резистором и напыпенной технологической перемычкой, общий вид; на фиг. 2 - схема включения моста при снятии величины температурного дрейфа.Способ осуществляется следующим образом.При изготовлении тензометрического моста 1, включающего в себя четыре тензорезистора 2"5, в одно из плеч, например, последовательно с тензореэисторами 4 и 5, вводят термочувствительный резистор 6. Выводы тензорезисторов 2-5 образованы соответственно контактными площадками 7-10, а выводы термочувствительного резистора 6 - контактньви площадками 11 и 12. Сопротивление термочувствительного резистора б выбирают таким, чтобы оно...

Устройство для контроля больших интегральных схем памяти

Номер патента: 1179375

Опубликовано: 15.09.1985

Авторы: Данилин, Моисеев, Попель, Простаков, Тамонин

МПК: G01R 31/3181, G06F 11/26

Метки: больших, интегральных, памяти, схем

...максимальные значения, которых могут достигать адреса Х и У, в регистры 32 и 33.После команд загрузки в программе следуют управляющие команды, соответствующие поля которых поступают на управляющие входы мультиплексоров 29, 30, 31 и тем самым коммутируют необходимые информационные входы вышеназванных мультиплексоров на вхО- ды соответствующих регистров, информация в которые записывается по тактовомч импульсу.В регистр 28 информация записывается непосредственно из памяти 27, Таким образом, регистр 48 и регистр 46 могут переписывать в себя информацию из соответствующих регистров установки или увеличивать свое содержимое на единицу или сохранять неизменную информацию. В регистр 48 информация записывается из регистра 34 или...

Способ изготовления инжекционных логических интегральных схем

Номер патента: 708862

Опубликовано: 23.09.1985

Авторы: Глебов, Грицаенко, Егоров, Тарасов

МПК: H01L 21/8222

Метки: инжекционных, интегральных, логических, схем

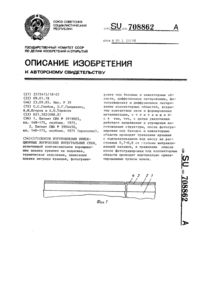

...0,2-0,3 мкм. Фотолигографией вскрывают окно, через которое травят в кремнии канавку 5 (фиг. 2) на глубину 0,3-0,4 мкм с одновременным подтравливанием под маску. При ориентации подложки в плоскости (100) или (111) подтравливание происходит на расстояние 0,7-0,8 от глубины канавки, т.е. на 0,2-0,3 мкм. В канавку проводят диффузию бора с разгонкой в окислительной атмосфере. В результате формируют базовую 6 (фиг, 3) и инжекторную 7 области на глубину 1,0-1,2 мкм, покрытие окислом 8 толщиной 0,3-0,35 мкм, Затем фотогравировкой вскрывают в окисле 8 окно 9 (фиг. 4), причем в качестве маски используют фоторезист, а травят вертикально ориентированным пучком ионов без бокового подтравливанияокисла,Фоторезист является маской с одной (двух) сторон...

Многоканальное устройство для функционального контроля интегральных схем

Номер патента: 1180819

Опубликовано: 23.09.1985

Автор: Морозов

МПК: G01R 31/3177

Метки: интегральных, многоканальное, схем, функционального

...19 начинает сдвиг единичного уровня в направлении от младшихразрядов сдвигового регистра к старшему, срабатывая по заднему фронту 20тактовых импульсов генератора 4. Придостижении старшего разряда единичным уровнем.и с приходом следующеготактового импульсоа генератора 4 врезультате срабатывания элемента И 2025импульс с выхода последнего, соединенного с выходом преобразователя 5кода во временной интервал, поступает на вход следующего преобразователя 6 кода во временной интервал 30и вход режима работы сдвигового регистра 19. При этом по заднему фронту тактового импульса происходитзапись информации, поступающей навходы сдвигового регистра 19 свыходов дешифратора 18, в результате чего устанавливается в единичное состояние, соответствующее...

Устройство для контроля интегральных схем

Номер патента: 1182520

Опубликовано: 30.09.1985

МПК: G01R 31/28, G06F 11/22

Метки: интегральных, схем

...дляформирования сигнала готовности устройства к связи с ЭВМ.Блок 5 порогового сравнения предназначен для измерения и преобразования контролируемого параметра в удобную для сравнения с граничными значе-ниями форму с последующим сравнениемс граничными значениями и передачи в 35ЭВМ результата сравнения.Коммутатор 6 предназначен для коммутации контактов контролируемой мик росхемы, 9 таким образом, что входные контакты подключаются к генерато. 40ру 7 испытательных воздействий, авыходные контакты подключаются к входам блока 5 порогового сравнения.Генератор 7 испытательных воздействий предназначен для подачи стимулирующих сигналов на входы контролируемой микросхемы 9,Блок 8 задержки предназначен дляформирования сигналов...

Аналого-цифровой преобразователь интегральных характеристик электрических величин с мультипликативной автокоррекцией

Номер патента: 1185604

Опубликовано: 15.10.1985

МПК: H03M 1/06

Метки: автокоррекцией, аналого-цифровой, величин, интегральных, мультипликативной, характеристик, электрических

...через инвертор 33 к входу сдвигового регистра 3", выходу генератора 35, а третьи входы соединены с выходами сдвигового регистра 32. Выход элемента ИЛИ 34 соединен с первым входом счетчика 37 двоичного умножителя 36 коррекции. Второй вход счетчика 37 подключен к выходу дешифратора 24, Выходы счетчика 37 соединены с первыми входами элементов И 38, вторые входы которых подключены к выходам вычитающего счетчика 40, а выходы - к входам элемента ИЛИ 39, третий вход цифрового интегратора 43 соединен с выходом элемента 4."., четвертый вход - с выходом элемента 39, а выход генератора 35 соединен с третьим входом блока 44, четвертые входы которого соединены с первыми выходами цифрового интегратора 43, второй выход которого соединен с пятым входом...

Формировтель напряжения смещения подложки для интегральных схем

Номер патента: 1185396

Опубликовано: 15.10.1985

Авторы: Бочков, Кузнецова, Однолько

МПК: G11C 11/40, G11C 7/00

Метки: интегральных, подложки, смещения, схем, формировтель

...смещенияподложки содержит входной транзистор 1, управляющий транзистор 2,нагруэочный транзистор 3, выходной 15, транзистор 4 и ключевые транзисторы 5 и 6, конденсатор 7, дополнительный конденсатор 8, информационныйвход (шину) 9, управляющий вход (шину) 10, общую шину 11, шину 12 питания, выходную шину 13,Формирователь работает следующимобразом.В исходном состоянии на шине 10 -высокий потенциал, а на шине 9 - ниэ кий. Напряжение на истоке транзистора 2 равно Ц напряжение на истоке транзистора 3 Нт 1 пороговое напряжение транзистора 4). Конденсатор 7 заряжен до напряжения 30Ноак (Нвк 3 Лт), На затворе транзистора 3 - отрицательное напряжение,но не ниже Ч -Ч , транзистор 3 закрыт.Затем на шину 9 подают низкийпотенциал, а на шину 10 -...

Устройство контроля больших интегральных схем

Номер патента: 1193608

Опубликовано: 23.11.1985

Авторы: Добровинская, Пункевич

МПК: G01R 31/3177

Метки: больших, интегральных, схем

...триггера 19, второй вход ключа 25. соединен с выходом генератора 24 тока, а выход - с соответствующей клеммой, для подключения вьгвода объекта контроля 7.Поскольку современные БИС имеют двунаправленные выводы, число каналов блока контроля равно числу выводов контролируемой БИС,Устройство контроля БИС работает в двух режимах: контроль наличия контактирования на всех выводах и собственно контроль схемы.Современная технология изготовления БИС обеспечивает наличие полупроводникового перехода между любым из выводов БИС и общей шиной, смещенного в обратном направлении.Наличие этого перехода классифицируется устройством как наличие контактирования, а обрыв или объединение собщей шиной классифицируется какотсутствие контакта по...

Способ изготовления больших интегральных схем на мдп транзисторах

Номер патента: 670019

Опубликовано: 30.11.1985

Авторы: Булгаков, Выгловский, Лебедев, Сонов

МПК: H01L 21/82

Метки: больших, интегральных, мдп, схем, транзисторах

...6 методомфотолитографии. Слой реэиста 6 покрывает активные области и служит маской при последующей ионной имплантации бором. Ионную имплантацию проводят при энергии ионов бора 100 кэВпри дозе 2 мкКул/см. При этом нанеактивных областях поверхности кремния образуется область 7 с повышенной концентрацией бора, который предотвращает образование инверсионных 9 2областей между диффузионными шинамии увеличивает пороговое напряжениепаразитных транзисторов. Затем снимают окисел 5 с нитрида кремния 2 надобластями 7. Травление окисла происходит в буферном травителе в течение 2-2,5 мин, Далее снимают фоторезист в серно-перекисной смеси истравливается нитрид кремния 1 надобластями 7. Травление происходитв ортофосфорной кислоте при температуре 140 фС...

Устройство для автоматического контроля больших интегральных схем

Номер патента: 1205083

Опубликовано: 15.01.1986

Авторы: Ворожеев, Зыбенков, Панов

МПК: G01R 31/3177

Метки: больших, интегральных, схем

...40, второй вход - с 7-м, третий - с б-м и т.д, Вторые входы коммутаторов 39 и 40 соединены с второй группой выходов регистра 42, а выхоцы раздельно подключены к входам схемы 41 совпадения, выход которой соединен,с первым входом цифрового комизменения или с изменением полярности сигналов в зависимости от команд, приходящих с блока 1 управления.Коммутаторы 39 и 40 представляют собой 8-канальные селекторы-мультиплексоры, предназначенные для передачи сигналов с выходов линии 38 калиброванных задержек на входы схемы 41совпадения по сигналам управления,поступающим из блока 1 через регистр42. Узлы многоканального компенсатора 10 выполнены на микросхемах серии1500, имеющих задержку порядка 1 нсна один вентиль,импульса, поступающего с выхода...

Способ изготовления инжекционных интегральных схем

Номер патента: 986236

Опубликовано: 23.01.1986

Авторы: Волынчикова, Красницкий, Савотин

МПК: H01L 21/82

Метки: инжекционных, интегральных, схем

...диф,фузии сквозь диэлектрическую илии ную маску создают сначала пф -области эмиттерного контакта 3 и эмиттерных охранных колец,4, а затем в об;ф. ластях базы 5, инжектора 6 и резистора 7 формируют л -слой (см. Фиг. 1).Далее методом имплантации или диффузии, используя диэлектрическую, резистивную или комбинированную маску, формируют р -пассивную базу 8,-инжектор 9 и р -охранные кольца к резисторам, 10 (см, фиг. 2). После этого в маске, закрывающей поверхность элементов, одновременно лито- графически создают контактные окна к коллекторным и базовым областям и резисторные окна, в которые методом имплантации или диффузии вводят примесь О -типа проводимости низкой концентрации и формируют л -области ,коллекторов 11 и л -резисторов 12....

Устройство для контроля интегральных схем

Номер патента: 1208555

Опубликовано: 30.01.1986

Авторы: Гаврилов, Кушуль, Школа

МПК: G01R 31/303, G06F 11/30

Метки: интегральных, схем

...с выходами второго и четвертого ключевых элементов. Устройство содержит блок 1 индикации блок 2 питающих напряжений, блок 3 опорных напряжений, измерительный блок 4, первый 5 и второй 6 комапараторы, реле 7 с обмоткой 7.1 и контактами 7,2, первый 8 и второй 9 генераторы тока, первый коммутационный блок 1 О, второй 11, четвертый 12, пятый 13 и третий 14 клю. чевые элементы, например реле, второй коммутационный блок 15, блок 161208управления, второй вход 17, счетчик 18 адреса, первый одновибратор,19, первый элемент 20 И, генератор21 тактовых импульсов, блок 22 памя.ти, блок 23 анализа брака, элемент24 НЕ, второй элемент 25 И, первый26 и второй 27 триггеры элемент28 ИЛИ-НЕ, второй одновибратор 29,.первые ключевые элементы...

Устройство для формирования интегральных характеристик модулярного кода

Номер патента: 1216777

Опубликовано: 07.03.1986

Авторы: Коляда, Кравцов, Ревинский

МПК: G06F 5/02

Метки: интегральных, кода, модулярного, формирования, характеристик

...К, то- -. - "аф величина а Кс третьего выхода блока 14 будет передана в (К+1) й 1 О счетчик блока 20 через информационный его вход, если,1 К, и в третий регистр блока 19 при )=К, величина Г 1.с четвертого выхода блока 14 передается в регистр 15, а также во второй регистр блока 19, если 1=К, Отметим, что величины ч и а, полуючаемые соответственно на третьем и четвертом выходах блока 14 хранения констант в (Т+К)-м такте работы уст ройства (1=К), являются соответственно второй и третьей цифрами полиадического представления числа А,л Лт,е, а=7 а =аз.л25;Признак 8с первого выхода блока 14 подается на единичный триггер 8 и вход установки в "0" регистра 7, после чего в него записываются содержимое соответствующих рзрядов счетчика 6, а...