G06F 7/38 — способы и устройства для выполнения математических операций только над машинными числами, например в двоичном, троичном, десятичном представлении

Устройство для сдвига информации

Номер патента: 1305661

Опубликовано: 23.04.1987

Авторы: Запольский, Костинский, Орлова, Подгорнов, Шугаев

МПК: G06F 7/38

Метки: информации, сдвига

...модификациясодержимого первого счетчика 3. Элемент ИЛИ 27 через элемент И 37 иэлементы ИЛИ 38 и 39 для первогосдвигового регистра 1 задает режимсдвига влево, а для второго сдвигового регистра 2 - режим занесения.Через элемент И 30 и элемент ИЛИ26 по очередному синхроимпульсу формируется строб первого сдвиговогорегистра 1 и через элемент 34 задержки и элемент ИЛИ 29 - строб второго сдвигового регистра 2. По этимстробам осуществляется в первомрегистре сдвиг на "4" разряда влево,а во втором регистре - перезапоминание сдвинутой информации. Одновременно модифицируется на "-1" содержимоевторого счетчика 4,Следующие три синхроимпульса осуществляют оставшиеся сдвиги влево на четыре. разряда, по окончании последнего из них в первом и втором...

Арифметическое устройство

Номер патента: 1305662

Опубликовано: 23.04.1987

Автор: Козлов

МПК: G06F 7/38

Метки: арифметическое

...= 2п+1) сумматоров 14 подключены соответственно к первой и второйгруппам выходов преобразователя 8.Устройство функционирует под действием управляющих сигналов (не показаны), В качестве операндов используются двоичные числа с фиксированнойзапятой в дополнительном коде.При выполнении операций сложенияи умножения работа устройства не отличается от известного устройства.Перед началом сложения в регистры1 и 6 записываются слагаемые. Еслизнаковые разряды регистров 1 и 6 совпадают, триггер 13 устанавливается внулевое, иначе - в единичное состояниеСодержание триггера 13 инвертируется,если при сложении возникает переносиз старшего разряда сумматора 7.При этом знаковый разряд регистра брезультата и содержимое триггера .13не совпадают, что...

Устройство для нормализации чисел

Номер патента: 1307454

Опубликовано: 30.04.1987

Авторы: Глотов, Саримахмудова, Шахматов

МПК: G06F 7/38

Метки: нормализации, чисел

...группу 13 элементов ИЛИ, группу 14 элементов НЕ 14, первую группу15 элементов И, четвертый элементИ 16, вторую 17 и третью 8 группыэлементов И.Устройство для нормализации чиселработает следующим образом.Ненормализованное число в обратном коде с двумя знаковыми разрядамис входа 2 поступает на узел 3 анализа и одновременно на вход сдвигателя6, порядок числа поступает также свхода 2 на первый вход сумматора-вычитателя 5. Число представленное сплавающей запятой, имеет основание 35"16". Поэтому нормализация осуществляется потетрадно. На элементах И 8,9, 12 и 16 узла 3 анализа осуществляется анализ знаковых разрядов. Если число положительное, то устанавливается потенциал на выходе элемента И 8, если число отрицательное, топотенциал...

Управляемый арифметический модуль

Номер патента: 1309017

Опубликовано: 07.05.1987

Автор: Дьяченко

МПК: G06F 7/38

Метки: арифметический, модуль, управляемый

...настройки,подаваемых на управляющие входы 14- 4519 модуля. Результат операции записывается в триггер 10 при подаче навход 24 синхросигнала Т.В таблице представлены реализуемыемодулем операции и соответствующие 50коды настроек, при этом принято, чтокод содержимого триггера перед нача-.лом операции соответствует операндуВ, а код А - входному операнду. Управляемый арифметический модуль,содержащий первый и второй коммута 17 2торы, триггер, элементы И и НЕ, причем 1.-й (д= 1,4) управляющий вход модуля соединен с 1-м информационным( входом первого коммутатора, первый управляющий вход которого соединен с прямым выходом триггера и выходом результата модуля, синхровход мо- . дуля соединен с синхровходом триггера, нулевой вход которого...

Устройство для нормализации двоичных чисел

Номер патента: 1310805

Опубликовано: 15.05.1987

МПК: G06F 7/38

Метки: двоичных, нормализации, чисел

...7 Р ГР 7 Р РР 7 Р ГР 7 Г ГР 7 Р ГР 7 Г РГ Элемент 53 памяти имеет следующую кодировку: Значе;ниевходов 01 2 3 4 5 6 7 8 9 А В С 0 Е Р 00 РГ РР ГР РР РР РГ РР РР ГГ ГР РГ РР РР ГР ГГ ГР 01 РЕ РЕ РЕ РК РЕ ГЕ ГЕ РЕ РГ, РР РР РР РР РР ГГ РР 02 РС РС РС ГС ГЮ ГЬ ГЬ ГЬ РЕ РЕ РЕ РЕ ГР ГР РГ ГР 03 Р 8 Р 8 Р 9 Р 9 РА РА РВ РВ РС РС ГП РЬ РЕ РЕ ГР РГ 04 РО Г 1 Г 2 ГЗ Р 4 Р 5 Рб Р 7 Р 8 Г 9 ГА РВ РС ГЬ РЕ РР 05 ЕО Е 2 Е 4 Еб Е 8 ЕА ЕС ЕЕ РО Р 2 Р 4 Рб Р 8 РА РС, РЕ 06 СО С 4 С 8 СС ЬО Ь 4 Р 8 ЬС ЕО Е 4 Е 8 ЕС РО Р 4 Р 8 РС 07 80 . 88 90 98 АО А 8 ВО В 8 СО С 8 ЬО Ь 8 ЕО Е 8 РО Р 8 08 00 10 20 30 40 50 60 70 80 90 АО ВО СО ЬО ЕО РО 09 00 20 40 60 80 АО СО ЕО 00 20 40 60 80 АО СО ЕО ОА 00 40 80 СО 00 40 80 СО 00 ОВ 00 80 00 80 00 80 00 80 00 40 80...

Устройство для сдвига информации

Номер патента: 1310806

Опубликовано: 15.05.1987

Авторы: Василевский, Галайда, Григорьев, Козелл

МПК: G06F 7/38

Метки: информации, сдвига

...Ю 1 И 16 Примечание Вход Вход 20. Разряды Содержимое Номер гакта первый 19 21 четтретий второй счетчика 4 вертый 1 х х 1 Сдвиг Ь 8ХранениеСдвиг Ь 16 7 110 х 0 хх 1 х 1 Перекр. код. х х 0 1 Хранение информации х х П р и м е ч а н и е. Ь 1, Ь 2Ь 16разрядов;х - безразличн ое состояние. Устройство для сдвига информации, 35 содержащее рабочий регистр, выходнойрегистр, группу мультиплексоров, счетчик, дешифратор, первый элемент ИЛИ, первый элемент НЕ и шесть элементов И, причем разряды информаци онного входа устройства соединены спервыми информационными входами соответствующих мультиплексоров группы, выходы которых соединены с соответствующими разрядами информационного 45 входа рабочего регистра, разряды выхода которого соединены с соответ"...

Устройство для определения среднего арифметического значения

Номер патента: 1310840

Опубликовано: 15.05.1987

Авторы: Корнейчук, Марковский, Широчин

МПК: G06F 7/38

Метки: арифметического, значения, среднего

...задержки через элемент И 20 поступает на счетчик 23,13108 1 О 1 1 1 1 О 1 где происходит вычитание единицы из содержимого счетчика 23. В дальнейшем на каждый (3-1)-й вход Ц=2,3п) вычитателя 17 поступает сигнал с 3-го выхода регистра 5, а на (3-1)-й вход узла вычитателя 17 - сигнал с выхода регистра 4.Описанная последовательность операции повторяется до тех пор, пока содержимое счетчика 23 не станет 10 равно нулю. При этом в регистре сдвига 4 будет сформировано среднее арифметическое с точностью до М разрядов, причем старший разряд среднего будет располагаться справа. 15П р и м е р. Пусть вычисляется среднее арифметическое четырех 4-разрядных чисел, записанных в ячейках блока 12 в виде 1 О20 1О О1 0 Пусть далее М = 6. Тогда работа 25...

Устройство для вычисления среднего арифметического

Номер патента: 1312613

Опубликовано: 23.05.1987

Авторы: Прянишников, Чапайкин

МПК: G06F 7/38

Метки: арифметического, вычисления, среднего

...сумматорами, и результатсложения, который ограничивается дчительностью импульса усреднения, в первом случае равен М=ХМ, (2)1 Оапри М -- сопя выражение (2) принимаетвид где и число тактовых импульсов на интервале Т.Второй интервал времени Т, начинаетсясразу по окончании импульса усреднения.В этом случае высокий уровень на входе Г коммутатора 20 снимается, а на его входе20 устанавливается, что позволяет подключитьинверсные выходы регистра 11 на входы В сумматора 8, на С-входе которого установлен высокий уровень, что переводит сумматор 8 в режим вычитания в дополнительном 25В синхронизаторе 13 на входы элементов 16 и 15 поступят сигналы для элемента 16 Разрешение, а для элемента 15 - Запрет. На тактовые С-входы регистров 7 и 9...

Вычислительное устройство

Номер патента: 1319022

Опубликовано: 23.06.1987

Авторы: Золотовский, Коробков, Ширванян

МПК: G06F 7/38

Метки: вычислительное

...например, сдвиг на "25" разрядов вправо и считывая информацию, начиная с 30 "32" разряда по "63", получим исходное число, сдвинутое на "7" разрядов влево. Эту операцию выполняеткоммутатор 1 по сигналу с входа 14.Если первые восемь разрядов равнынулю, то на прямом выходе схемы 2сравнения формируется логическаяединица, на инверсном - логическийноль. На схеме 3 сравнения анализируется следующая группа из восьми ,10 разрядов. Если она не нулевая, тона выходе схемы сравнения с нулемформируется логический ноль. В результате формируются сигналы, запре.щающие считывание из блоков 11 и12, и на элементе И 5 формируетсясигнал, разрешающий считывание изблока 10.Параметр сдвига формируется аналогично описанному за тем исключением, что...

Устройство для сдвига операндов

Номер патента: 1330626

Опубликовано: 15.08.1987

Авторы: Заблоцкий, Самусев, Спасский, Шпаков

МПК: G06F 7/38

...нуле вой сигнал на выходе при равенстве нулю значения входа 4 и единичный сигнал - в противном случае.Соединение разрядов информационного входа 5 устройства с информационными входами модулей 1 сдвига выполняется по следующему правилу,В каждом -м модуле сдвига разряды 3-й группы информационного входа модуля 1 сдвига соединяют с раэряда 20 ми 1-группы разрядов информационного входа 5 устройства с сохранением порядка расположения разрядов в группах, гдеесли 25(3-1), если 11; 1 0 1В 3ккода с входа 5 на выход 6 устройства. При этом на выходе преобразователя Э и входах 9 модулей сдвига формируется нулевой код, так как дополнительный код от нулевого кода также является нулевым кодом, При установке на входе 7 кодов ЦП, ЛП, ЦЛ значение...

Устройство для вычисления среднего значения

Номер патента: 1334161

Опубликовано: 30.08.1987

Автор: Нисневич

МПК: G06F 17/18, G06F 7/38

Метки: вычисления, значения, среднего

...поступленияпоследнего информационного слова навход устройства. Счетчик 7 подсчитывает число переходов 5 объема выборки Кт в модуле предыдущей ступени через К,= К ,поступающих по входу 11. Сигналы переполнения счетчика 7 модуля даннойступени синхронизируют работу модуля следующей ступени. Содержимоесчетчика 7 суммируется с объемомвыборки К , обеспечиваемой модулемпредыдущей ступени на сумматоре 4,с выхода которого объем выборки п 1,обеспечиваемый модулем данной сту -пени, поступает на вход 10 модулян делительный вход делителя 8,. Навыходе делителя 8 получаем значение.Е Х, - Х - К,ют , которое суммируетП 1ся на сумматоре 3 с Х1 с ,поступаютщим с прямого выхода регистра 6.Очередное значение Хт записываетсяв регистр 6 по сигналам,...

Арифметическое устройство

Номер патента: 1335979

Опубликовано: 07.09.1987

Авторы: Генкин, Голубев, Кириллов, Пешков, Скворцов, Терентьев

МПК: G06F 7/38

Метки: арифметическое

...и обеспечивает запись в счетчик 15 циклов, который обеспечивает счет количества кусков реализаций. После заполнения счетчик 15 циклов выдает на выход 10 сигнал о готовности устройства.Блок 5 управления обеспечивает блокирование синхронного накопления с момента поступления сигнала блокировки на вход 8 до момента снятия сигнала 8, но не раньше момента записи в следующую ячейку, считая с ячейки, в которую последней произошла запись к моменту поступления сигнала 8.При отсутствии сигнала блокировки на входе 8 триггер 20 находится в нулевом состоянии, Элементы ЗАПРЕТ 13 и 14 разрешают прохождение сигналов записи и в регистр 15. Сигналы от компаратора 19 блокируются в элементе 17.При поступлении сигнала блокировки, который на практике может...

Вычислительное устройство

Номер патента: 1336022

Опубликовано: 07.09.1987

Авторы: Борисенко, Возыкин, Калкин, Сапрунов

МПК: G06F 7/38

Метки: вычислительное

...В третьем такте по управляющим сигналам (входы 5 и 20) открываются вторые входы мультиплексоров 2 - 5 и результаты выполненной в каждом сумматореоперации с выходов регистров 10 и 11 поступают на входы сумматоров 6 и 7.Начиная с третьего такта, сумматоры 6и 7 работают в режиме компаратора в соответствии с кодом микрокоманды вычитания (таблица), поступающим на вход 19, иформируют сигналы признаков сравнения К,которые поступают с вторых выходов сумматоров 6 и 7 на вход элемента 13, выходкоторого подключен к выходу 17, при этомсостояние регистров 10 и 11 не изменяется. В случае сравнения результатов операции в обоих сумматорах элемент 13 выдаетсигнал разрешения, в соответствии с которым в четвертом такте производится зались результатов...

Устройство для округления суммы и разности двоичнокодированных чисел с плавающей запятой

Номер патента: 1339549

Опубликовано: 23.09.1987

МПК: G06F 7/38

Метки: двоичнокодированных, запятой, округления, плавающей, разности, суммы, чисел

...разряде 7 сдвинутого на один рязряд вправо кода знача - щую цифру: "1" в первом случае и "О" - во втором. Таким образом, после первого выхода за разрядную сетку регистра 1 значащей цифры в младшем разряде 7 этого регистра при всех последующих сдвигах кода вплоть до момента окончания денормализации будет находиться значащая цифра. Этим обеспечивается указанная выше коррекция денормализованного числа,35 3 1339Далее происходит нормализация результата сложения или вычитания. Мантисса и знак результата находятся соответственно в регистре 2 и тригге 5ре 4,Если результат требуется нормализовать вправо, то на вход управлениясдвигом вправо регистра 2 по входу6 поступает сигнал "1", в результатечего происходит сдвиг кода, находящегося в...

Устройство для округления суммы и разности двоичнокодированных чисел с плавающей запятой

Номер патента: 1339550

Опубликовано: 23.09.1987

МПК: G06F 7/38

Метки: двоичнокодированных, запятой, округления, плавающей, разности, суммы, чисел

...осуществляемая устройством, приводит к тому,что погрешнось округления можетиметь различные знаки независимо отзнаков слагаемых и выполняемой опе О рации. Действительно, пусть, например, порядки слагаемых одинаковые,так что денормализации не происходит, и, следовательно, денормализованное слагаемое не корректируется.45 В этом случае погрешность округленияскладывается из погрешности норма-.лизации результата, связанной с отбрасыванием значащей цифры, выдвинутой за разрядную сетку регистра при 50 нормализации вправо, и усечениемрезультата на дополнительный разряд,а также погрешности, связанной сзасилкой значащей цифры в младшийразряд нормализованного и усеченногорезультата. Так как появление цифры"0" или "1" в младшем разряде результата...

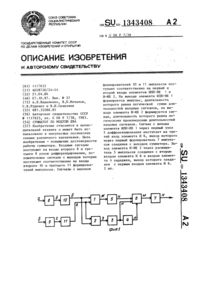

Сумматор по модулю два

Номер патента: 1343408

Опубликовано: 07.10.1987

Авторы: Барыленко, Мочалов, Руденко, Селезнев

МПК: G06F 7/38

...модулю два содержитэлементы ИЛИ-НЕ 1 и И-НЕ 2, расширитель 3 импульсов, элемент 4 задержки,первый узел 5 дифференцирования, элемент И 6, первый формирователь 7 импульсов, второй 8 и третий 9 узлыдифференцирования, второй 10 и третий11 формирователи импульсов,Сумматор по модулю два работаетследующим образом.Входные последовательности импульсов поступают на второй 8 и третий 9узлы дифференцирования, дифференциру-:ются и своими передними фронтами запускают формирователи 10 и 11 импульсов. С выходов формирователей 10 и 11импульсов последовательности импульсов поступают на элемент ИЛИ-НЕ 1.Длительность сигнала, поступающегос выхода элемента ИЛИ-НЕ 1 на входпервого узла 5 дифференцирования,равна суммарной длительности информационных сигналов...

Устройство для нормализации чисел

Номер патента: 1345189

Опубликовано: 15.10.1987

Авторы: Костинский, Подгорнов, Шугаев

МПК: G06F 7/38

Метки: нормализации, чисел

...на один разряд влево. Этот процесс будет продолжаться до появления "1" в старшем разряде любого из сдвигающих регистров 6-9, при этом на выходе анализатора 15 устанавливается низкий потенциал. Низкий потенциал устанавливается на выходе элемента ИЛИ 4. Счетчики 10 и 16 и сдвигающие регистры переводятся в режим "Хранение до появления высокого потенциала на шине 3,Если число записывается в счетчик 10 и сдвигающие регистры 6-9 при наличии высокого потенциала на шине 1, то по заднему фронту синхросигнала на шине 11 устанавливается триг. гер 12, так как в этом время на выходе элемента И 2 высокий потенциал. После снятия высокого потенциала с шины 3 высоким потенциалом на выходе триггера 12 сохраняется высокий потенциал на выходе элемента...

Шифратор кода нормализации

Номер патента: 1345351

Опубликовано: 15.10.1987

Авторы: Заблоцкий, Самусев, Спасский, Яскульдович

МПК: G06F 7/38, H03M 7/00

Метки: кода, нормализации, шифратор

...блокировка всех ячеек в блоке 2, находящихся правее той ячейки,на выходах которой установлена часть входного кода с границей нулей всего входного кода. т.е. открытыми (не заблокированными) являются все соседние ячейки слева в блоке 2, на входах которых установлены сигналы групп разрядов, все разряды которых нулевые, и ближайшая соседняя слева (выделенная) ячейка 12, на входах которой установлены сигналы той группы разрядов, только на части которой установлены нулевые значения (если такая группа имеется), В результате на выходах выделенной ячейки 12 и на соответствующих выходах бло 50 Алгоритм работы ячейки 6 или 12 основан на том,что с помощью элементов 15 осуществляется дешифрации кода, установленного на первых входах таким образом, что...

Арифметическое устройство для выполнения операций над несколькими числами

Номер патента: 1348822

Опубликовано: 30.10.1987

Авторы: Дорожкин, Жабин, Миргородская

МПК: G06F 7/38

Метки: арифметическое, выполнения, несколькими, операций, числами

...из которых выполняется не более И операций, В первом цикле вычислений на входные шины операндов 1010 поступает первая группа,йф 1включающая 3+1 операндов, представленных последовательным кодом. В последующих циклах на входные шины операндов 10 -10 1 поступают группы изу К 1операндов (в последнем цикле числооперандов может быть меньше И).Число И выбрано таким, что к моменту появления первого разряда промежуточного результата на выходахрешающего блока И решающий блок 1оказывается свободньгм,В каждом цикле вычислений послевыполнения 1+1 очередных тактовсигналу блока 2 осуществляется сдвиг"1" в регистре 8 на один разрядвправо и в результате этого на управляющий вход блока 1 с номером 3 поступает единичный сигнал с выхода3-го разряда...

Устройство для округления суммы и разности двоично кодированных чисел с плавающей запятой

Номер патента: 1361542

Опубликовано: 23.12.1987

МПК: G06F 7/38

Метки: двоично, запятой, кодированных, округления, плавающей, разности, суммы, чисел

...Если в младшей тетраде регистра 1 до сдвига кода находятся нули, то на входе 3 младшего разряда после сдвига кода на одну тетраду вправо действует сигнал 0, не меняющий состояние этого разряда. Если в одном из разрядов младшей тетрады регистра 1 до сдвига кода находится хотя бы одна "1", то младший разряд 5 после сдвига кода окажется в состоянии "1", Таким образом, после первого выдвижения за разрядную сетку регистра 1 цифры "1" в младшем разряде 5 этого регистра при всех последующих сдвигах вплоть до момента прекращения денормализации всегда. будет находиться цифра "1". Этим обеспечивается указанная выше коррекция денормализованного числа.Далее происходит нормализация результата выполнения операции. Мантисса ненормализованного...

Устройство для округления суммы и разности двоично кодированных чисел с плавающей запятой

Номер патента: 1361543

Опубликовано: 23.12.1987

МПК: G06F 7/38

Метки: двоично, запятой, кодированных, округления, плавающей, разности, суммы, чисел

...должен быть поставленсоответствующий элемент задержки).Если в дополнительной тетраде 6регистра 1 до сдвига кода находятсянули, то на входе младшего разряда 8после сдвига кода на одну тетраду30 вправо действует сигнал "0", не меняющий состояние этого разряда. Еслиже в одном из разрядов тетрады 6 имеется "1", то в младшем разряде 8 после сдвига кода будет установлена "1 ".Таким образом, после первого выдвижения за разрядную сетку регистра 1 цифры "1" в младшем разряде 8дополнительной тетрады 6 при всехпоследующих сигналах вплоть до момен 40 та окончания денормализации всегдабудет находиться "1". Этим обеспечивается указанная выше коррекций, денормалйзованного числа,Далее происходит нормализация ре 45 эультата выполнения операции сложения...

Арифметическое устройство

Номер патента: 1363186

Опубликовано: 30.12.1987

МПК: G06F 7/38

Метки: арифметическое

...22 управления подается код функции обратной величины. На выходе блока 11 постоянной,памяти устанавливается значение 1/х;.50В следующем такте работы устройства производится анализ величины- 1 кф 11 (ки 1ш 2 на нуль. Величина ш 2через шинный коммутатор 8 записывается в регистр 6 иношине 20 поступает на вход арифметико-логическогоблока 1, который производит операцию сравнения на нуль. В случае по-:,ложительного результата анализа,т,е, т 2 "Ч = О, первый этап операции деления на этом заканчивается.Значение 1/х; на выходе блока 11 постоянной памяти будет искомым дляфункции обратной величины. Это значение через шинный коммутатор 8 записывается в регистр 7 и по шине 21 по"ступает на вход умножителя 2. Одновременно делимое через шинный...

Ассоциативное арифметическое устройство

Номер патента: 1363187

Опубликовано: 30.12.1987

Авторы: Афанасьев, Жигач, Кисленко, Кокаев

МПК: G06F 7/38

Метки: арифметическое, ассоциативное

...14 синхронизации, навход адреса ПЗБ 2 с выхода ПДУ 8 подается второй разрядный срез слагаемых, т,е. адрес 0111111,По указанному адресу из ПЗБ 2считывается слово 011. На входеПДУ 9 формируется слово 0011000,а на его выходе - 0000011, котороепо приходу импульса по входу 17 син 4хронизации поступает на признаковые20 После поступления каждого тактового импульса с входа 14 синхронизации соответствующие значения операндов будут поступать на входы элементов И 5, на которых будут сформированы разрядные срезы, состояние входы АЗБ 1, На выходе АЗБ 1 формируется слово 0010, правый разрядкоторого."1" является вторым разрядом искомой суммы,В течении третьего импульса, поданного на вход 14 синхронизации,на вход адреса ПЗБ 2 с выхода ПДУ 8подается...

Операционное устройство

Номер патента: 1367012

Опубликовано: 15.01.1988

Авторы: Белецкий, Карась, Кузнецова, Кулик, Павлусенко, Семенов, Шуфчук

МПК: G06F 7/38

Метки: операционное

...Р -Р, равен "0" (число 1 ОР-Р положительное), то на выходах1 и 2 блока 16 управления формируютсясоответственно "0" и "1", приводя ксдвигу М .,Если знак Р -Рр равен "1"число Р-Рр отрицательное), то на 15выходах 1 и 2 блока 6 управленияформируются соответственно "1" и "0",приводя к сдвигу М. Сдвиг М ц или Мосуществляется вправо на число разрядов, равное модулю значения Р-Рр. В 20АЛУ 6 Формируется соответственно сумма или разность мантисс М и Мпоступающих с выходов сдвигателей 4и 5Результат с выхода АЛУ 6 черезкоммутатор 9 поступает на входы шифратора 10 числа нулей и нормализаторНа выходе шифратора О формируется код, равный числу последовательных нулей, начиная со старшего разряда входного слова, 30Этот код поступает на второй...

Устройство для сдвига операндов

Номер патента: 1368873

Опубликовано: 23.01.1988

МПК: G06F 7/38

...логическом сдвиге вправо уст 15 ройстро Функционирует так же, как ипри циклическом сдвиге вправо с темотличием, что в модулях сдвига рассматриваемого случая, номера которыхт.И , осуществляется блокировка выхода первого и второго мультиплексоров15 и 16, а при д И - выхода тольковторого мультиплексора 16, так какна выходе элемента И-ИЛИ 14 формируется логическая "1".25 В результате на выходе 6 устройства формируется логически сдвинутыйвправо код,При логическом сдвиге влево устройство функционирует так же, как иЗп при циклическом сдвиге влево,с темотличием, что в модулях 1 сдвига,Яномера которых д (- - М) прн шО иК а на выход мультиплексора 16 передаются сигналы б-й группы разрядов информационного входа, где1-(М+1, если дМ+1= и--...

Устройство для сдвига операндов

Номер патента: 1368874

Опубликовано: 23.01.1988

Авторы: Заблоцкий, Самусев, Спасский, Шпаков

МПК: G06F 7/38

..." 1".Для обеспечения работоспособности устройства вход 5 устройства необходимо соответствующим образом подключить к информационному входу каждого модуля 1 сдвига. Правило указанного подключения заключается в следующем, В каждом 1.-м модуле сдвига разряды 3-й группы разрядов информационного входа модуля сдвига соединяют с разрядами 1-й группы разрядов информационного входа устройства с сохранением порядка расположения разряда в группах разрядов, где Устройство работает следующим образом.Исходное состояние устройства может быть произвольным. Для осущест вления сдвига операнда код его устанавливается на входе 25 устройства. На входе 4 устройства устанавливается код величины сдвига. На входе 7 устройства устанавливается код типа сдвига...

Устройство для вычисления функции табличным методом

Номер патента: 1383337

Опубликовано: 23.03.1988

Авторы: Демин, Евстигнеев, Кошарновский, Кузьмина, Маркин

МПК: G06F 7/38, G06F 7/544

Метки: вычисления, методом, табличным, функции

...поступает байт константы "1" вида 00000001,В последующие два такта по сигналам с девятого 30 и десятого 31 выходов блока 20 управления в умножителях 16-18 вычисляется величина В.1. В результате работы блока 3 ".умматоров величина Ах + В 1 сформирована на выходах 45-47 блока 3 сумматоров,на выходе 44 блока 3 сумматора имеется нуль.Далее по сигналу с одиннадцатого выхода 51 блока 20 управления содержимое сумматоров 38, 41, 42 и 43 блока 3 суммирования заносится в регистры 5-8 регистра 4 функций, а содержимое регистров 48 и 49 смещается вправо на один байт. В результате на 5=0, .6=Б(, 7=Б , 48=Б, 49=8,50=Б 1Содержимое регистров 6-8 и 48 необходимо сместить на два байта вправо так, чтобы в регистре 50 находился четверый байт величины...

Устройство для вычисления функций

Номер патента: 1388848

Опубликовано: 15.04.1988

Автор: Плющ

МПК: G06F 7/38

Метки: вычисления, функций

...регистр2.1 числа, а значение величины рв регистр 2.2 числа, величины - Я 1 "в регистр 2.3 числа, а значение величины Я, в регистр 2.4 числа. Навтором такте работы устройства первый блок 9,1 формирования итерационных коэффициентов вычислит значениевеличины, равноеЬ; = 3+1-к=1+1-0,5=1,5.Аналогично второй блок формирова"ния итерационных коэффициентов 9.2вычислит значение а.а=х(Е)=0,51 =0,5,На выходах первого и второго сумматоров 4. 1 и 4.2 образуются значениявеличинр=Ь р+азра=1,5 1+0,5 1=2,=Ь Я+а Я,=1,5 0,5+0,5 1=1,25,По окончании переходных процессовв сумматорах 4.1 и 4.2 синхроимпульсом, выработанным схемой 5 синхронизации, значения р изапишутся врегистры 2. 1 и 2.3 чисел, а значения, р и Я - в регистры 2.2 и 2,4 чисел,этим же...

Устройство для нормализации чисел

Номер патента: 1388849

Опубликовано: 15.04.1988

Авторы: Костинский, Подгорнов, Шугаев

МПК: G06F 7/38

Метки: нормализации, чисел

...с входа 3) будут низкие потенциалы и счетчик 1 О и сдвигающие регистры 6-9 находятся в режиме ХранениеЕсли принятое число не нормализовано (с "0" в старших разрядах сдвигающих регистров 6-9) и нет высокого потенциала на входе 1 (триггер 12 не устанавливается), на выхо- де элемента ИЛИ-НЕ 15 будет высокий потенциал, После снятия высокого потенциала, , на выходе элемента ИЛИ 5 - низкий потенциал. При этих условиях счетчик 1 О находится в режиме "-1", а сдвигающие регистры 6-9 находятся в режиме Сдвиг влево" и по заднему фронту каждого синхросигнала на входе 11 из значения счетчика 10 вычитается "1", а в каждом из сдвигающих регистров 6-9 информация сдвигается на один разряд влево. Вместе с этим на элементе ИЛИ-НЕ...

Арифметическое устройство

Номер патента: 1392558

Опубликовано: 30.04.1988

Авторы: Белан, Кожемяко, Тимченко

МПК: G06F 7/38

Метки: арифметическое

...нулк). Бцчит 3(и( нроисхолитна нрдяжен(и дсо слига 11 а уира(1 якпим вх.и 47 .13(н;3 1( начяти присут 1 СХ ( 1, 1( И И. ( Кс(Я (. Л) Н И 33, КТОР(я ПО,с 3 Ц)2558 ется с выхола с(,ьчого ,их(31,3 11,111 2(15 о вречя с,ниа внр,во н;3 хо.(сх 1 и41 Ст;рпНХ рс)цряЛОВ О 6 ИХ р( ИС 1 рцН4 Но.счж н Ы 3(Т 11 р. ко ч О)31111111 131113,1с,КОТОР 11(. .Сс,3 с НЫ (Х. с(О.1 НХ ) В СИ.1 КОХ5 ОИ На нй с( И (5. (,ОтС(3 ("СНи Н(3 цц ХОн яо .,1 ч( н( 11,111 ) Ох,и3;к,+( ц длани 1 й 1;36,иии В чоч н, ко.ь= 1, тс 1 ктои 13 их,1(ь и с х и 31 3(р спрвцй ихИ 1 1 1, н(рвци ч н1 О 11,111 5, олиннала 1 ый г х(н 11 2, ити а.(г чнт 11,(И 25 н;3 счегнци сх.четчиксд), которы, (1 к чр,ь. Ихнолсч иты н(и т.1 с( к и х 0 6 р с 1 .с ( ) х 1,в1 (.Г1 и к (. 1 , ) р . ц х . 3...