Сумматор по модулю два

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

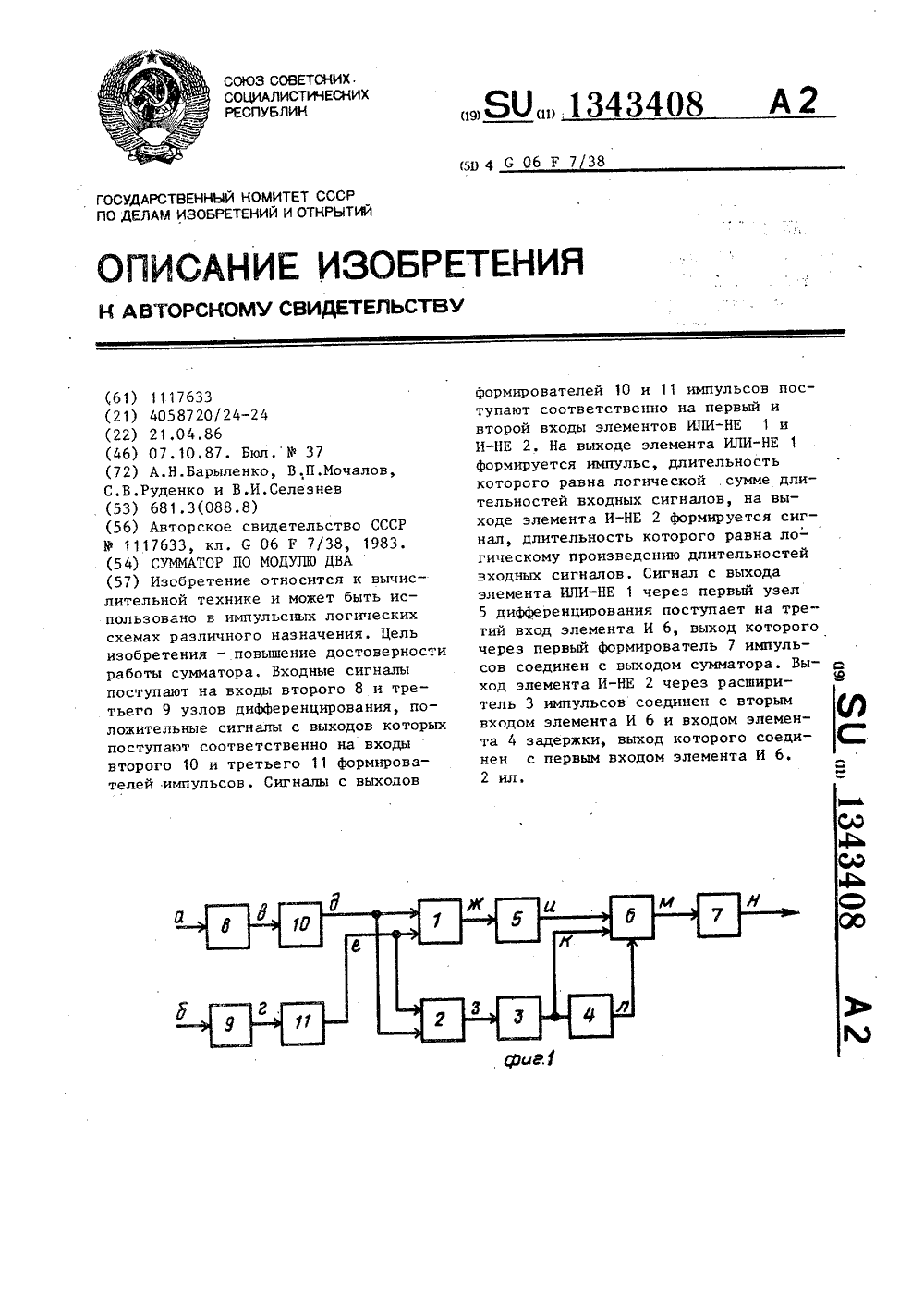

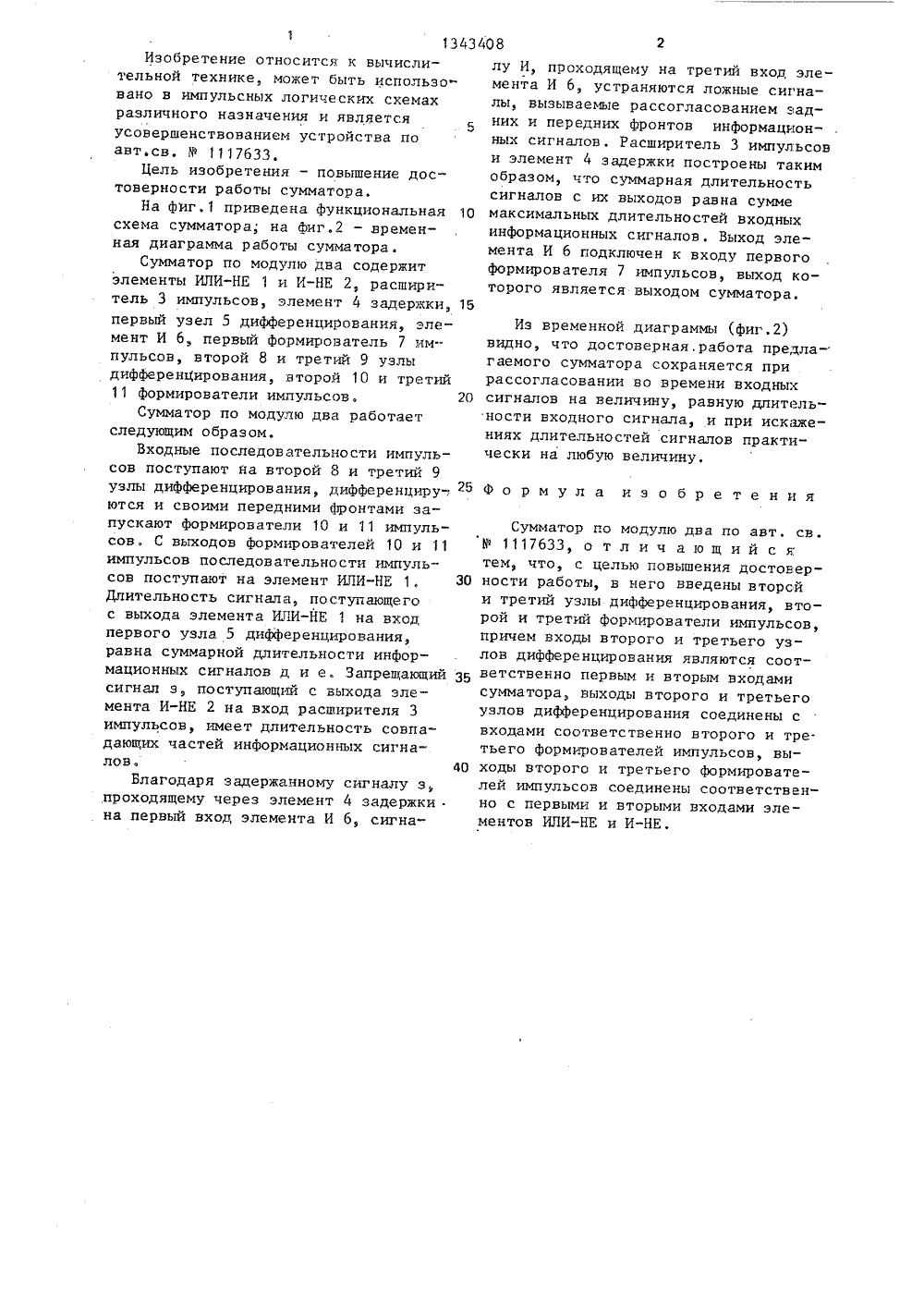

СЭОЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСНИХ РЕСПУБЛ 50 4 С 06 Г 7 3 И.В.Р (53) выи и Е 1 Вы- Ф Входом та 4 з ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИИ ОЙИСАНИЕ ИЗОБ ТОРСКОМУ СВИДЕТЕЛЬСТВ 1176334058720/24-2421,04.8607.10,87. Бюл. " 37А.Н.Барыленко, В.П,Мочалов, С уденко и В.И.Селезнев681.3(088.8)(56) Авторское свидетельство СССР У 1117633, кл. С 06 Р 7/38, 1983. (54) СУММАТОР ПО МОДУЛЮ ДВА(57) Изобретение относится к вычислительной технике и может быть использовано в импульсных логических схемах различного назначения, Цель изобретения - повышение достовернос работы сумматора. Входные сигналы поступают на входы второго 8 и третьего 9 узлов дифференцирования, по ложительные сигналы с выходов котор поступают соответственно на входы второго 10 и третьего 11 формирователей импульсов . Сигналы с выходов1343408 формирователей 10 и 11 импульсов пос тупают соответственно на пер второй входы элементов ИЛИ-Н и И-НЕ 2. На выходе элемента ИЛИ-НЕ 1 формируется импульс, длительность которого равна логической .сумме дли тельностей входных сигналов, на выходе элемента И-НЕ 2 формируется сиг нал, длительность которого равна логическому произведению длительностей входных сигналов. Сигнал с выхода элемента ИЛИ-НЕ 1 через первый узел 5 дифференцирования поступает на тре тий вход элемента И 6, выход которог через первый формирователь 7 импульсов соединен с выходом сумматора. ход элемента И-НЕ 2 через расширитель 3 импульсов соединен с вторымэлемента И 6 и входом элеменадержки, выход которого соединен с первым входом элемента И 6.Изобретение относится к вычислительной технике, может быть использовано в импульсных логических схемахразличного назначения и являетсяусовершенствованием устройства поавт.св. Ф 1117633.Цель изобретения - повышение достоверности работы сумматора.На фиг.1 приведена функциональнаясхема сумматора; на фиг.2 - временная диаграмма работы сумматора.Сумматор по модулю два содержитэлементы ИЛИ-НЕ 1 и И-НЕ 2, расширитель 3 импульсов, элемент 4 задержки,первый узел 5 дифференцирования, элемент И 6, первый формирователь 7 импульсов, второй 8 и третий 9 узлыдифференцирования, второй 10 и третий11 формирователи импульсов,Сумматор по модулю два работаетследующим образом.Входные последовательности импульсов поступают на второй 8 и третий 9узлы дифференцирования, дифференциру-:ются и своими передними фронтами запускают формирователи 10 и 11 импульсов. С выходов формирователей 10 и 11импульсов последовательности импульсов поступают на элемент ИЛИ-НЕ 1.Длительность сигнала, поступающегос выхода элемента ИЛИ-НЕ 1 на входпервого узла 5 дифференцирования,равна суммарной длительности информационных сигналов д и е. Запрещающийсигнал з, поступающий с выхода элемента И-НЕ 2 на вход расширителя 3импульсов, имеет длительность совпадающих частей информационных сигналов.Благодаря задержанному сигналу з,проходящему через элемент 4 задержкина первый вход элемента И 6, сигналу И, проходящему на третий вход элемента И 6, устраняются ложные сигналы, вызываемые рассогласованием задних и передних фронтов информационных сигналов. Расширитель 3 импульсови элемент 4 задержки построены такимобразом, что суммарная длительностьсигналов с их выходов равна сумме10 максимальных длительностей входныхинформационных сигналов. Выход элемента И 6 подключен к входу первогоформирователя 7 импульсов, выход которого является выходом сумматора,15Из временной диаграммы (фиг,2)видно, что достоверная. работа предлагаемого сумматора сохраняется прирассогласовании во времени входных20 сигналов на величину, равную длительности входного сигнала, и при искажениях длительностей сигналов практически на любую величину,25 формулаиз обретенияСумматор по модулю два по авт, св.91117633, отлич ающийся тем, что, с целью повышения достовер ности работы, в него введены вторсйи третий узлы дифференцирования, второй и третий формирователи импульсов, причем входы второго и третьего узлов дифференцирования являются соотЗ 5 ветственно первым и вторым входамисумматора, выходы второго и третьего узлов дифференцирования соединены свходами соответственно второго и третьего формирователей импульсов, вы ходы второго и третьего формирователей импульсов соединены соответственно с первыми и вторыми входами элементов ИЛИ-НЕ и И-НЕ.1343408 Составитель В,ГречневТехред Л.Сердюкова Редактор П.Гереши Корректор М. Максимишинец Заказ 4824/49 Тираж 672ВНИИПИ Государственного комитета СССРпо делам изобретений и открытий113035, Москва, Ж, Раушская наб д. 4/5 Подписное Производственно-полиграфическое предприятие, г. Ужгород, улПроектная, 4

СмотретьЗаявка

4058720, 21.04.1986

СТАВРОПОЛЬСКОЕ ВЫСШЕЕ ВОЕННОЕ ИНЖЕНЕРНОЕ УЧИЛИЩЕ СВЯЗИ ИМ. 60-ЛЕТИЯ ВЕЛИКОГО ОКТЯБРЯ

БАРЫЛЕНКО АЛЕКСАНДР НИКОЛАЕВИЧ, МОЧАЛОВ ВАЛЕРИЙ ПЕТРОВИЧ, РУДЕНКО СЕРГЕЙ ВИКТОРОВИЧ, СЕЛЕЗНЕВ ВЛАДИМИР ИВАНОВИЧ

МПК / Метки

МПК: G06F 7/38

Опубликовано: 07.10.1987

Код ссылки

<a href="https://patents.su/3-1343408-summator-po-modulyu-dva.html" target="_blank" rel="follow" title="База патентов СССР">Сумматор по модулю два</a>

Предыдущий патент: Сравнивающее устройство для цифровых следящих систем

Следующий патент: Устройство для суммирования двоичных чисел

Случайный патент: Антифрикционная прессованная древесина