Устройство для вычисления функции табличным методом

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1383337

Авторы: Демин, Евстигнеев, Кошарновский, Кузьмина, Маркин

Текст

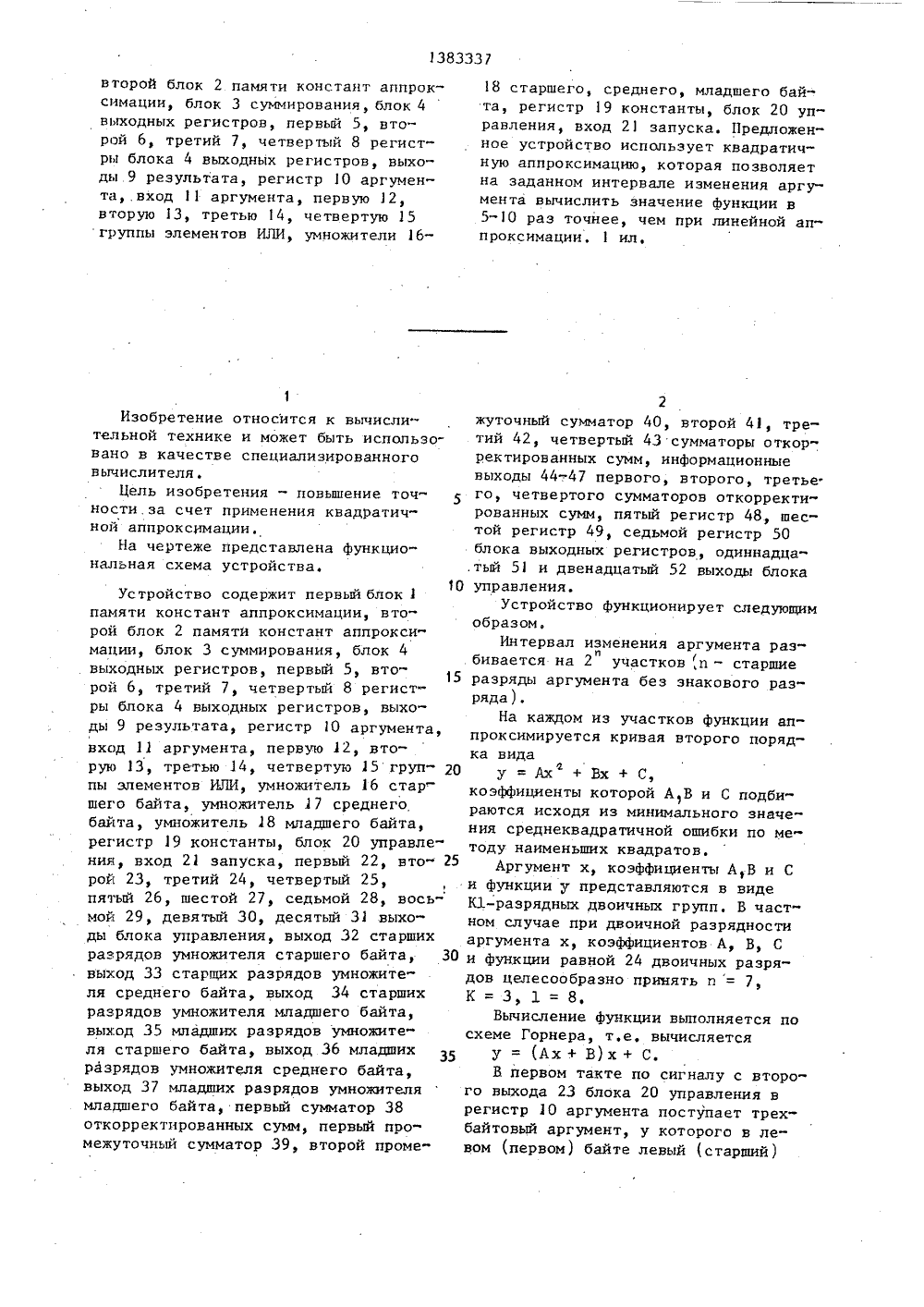

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИК 383337 06 Р 7/38, 7/544 ГОСУДАРСТВЕННЫЙ ПО ДЕЛАМ ИЗОБРЕТ МИТЕТ СССРИЙ И ОТНРЫТИЙ Е ИЗОБРЕТ ОПИСА К АВТОРСК с У СВИДЕТЕЛЬСТВУ(56) Авторское свидетельство СССРУ 826324, кл. С 06 Р 1/02, 1979 .Смолов В.Б. Функциональные преоразователи информации, -Л,; Энергоиздат, 1981, с.144, рис.4 4 а.(54) УСТРОЙСТВО ДЛЯ ВЫЧИСПЕНИЯ ФУНКЦИЙ ТАБЛИЧНЫМ МЕТОДОМ(57) Изобретение относится к вычислительной технике и может быть использовано в виде автономного специализированного вычислителя или вкачестве функционального расширителяв составе больших ЭВМ. Целью изобретения является повышение точности засчет применения квадратичной аппроксимации. Устройство содержит первыйблок 1 памяти констант аппроксимации383337 второй блок 2 памяти констант аппроксимации, блок 3 суммирования, блок 4выходных регистров, первый 5, второй 6, третий 7, четвертый 8 регистры блока 4 выходных регистров, выходы 9 результата, регистр 10 аргумента, вход 11 аргумента, первую 12,вторую 13, третью 14, четвертую 15группы элементов ИЛИ, умножители 16 Изобретение относится к вычислительной технике и может быть использо вано в качестве специализированного вычислителя.Цель изобретения - повышение точности.за счет применения квадратичной аппрокснмации,На чертеже представлена функциональная схема устройства. 10Устройство содержит первый блок 1памяти констант аппроксимации, второй блок 2 памяти констант аппроксимации, блок 3 суммирования, блок 4выходных регистров, первый 5, второй 6, третий 7, четвертый 8 регистры блока 4 выходных регистров, выходы 9 результата, регистр О аргумента,вход 1) аргумента, первую 12, вторую 13, третью 14, четвертую 15 группы элементов ИЛИ, умножитель 16 старшего байта, умножитель 17 среднегобайта, умножитель 18 младшего байта,регистр 19 константы, блок 20 управления, вход 21 запуска, первый 22, второй 23, третий 24, четвертый 25,пятый 26, шестой 27, седьмой 28, восьмой 29, девятый 30, десятый 3 выходы блока управления, выход 32 старшихразрядов умножителя старшего байта, 30выход 33 старщих разрядов умножителя среднего байта, выход 34 старшихразрядов умножителя младшего байта,выход 35 младших разрядов умножителя старшего байта, выход 36 младшихразрядов умножителя среднего байта,выход 37 младших разрядов умножителямладшего байта, первый сумматор 38откорректированных сумм, первый промежуточный сумматор 39, второй проме 18 старшего, среднего, младшего байта, регистр 19 константы, блок 20 управления, вход 21 запуска. Предложенное устройство использует квадратичную аппроксимацию, которая позволяетна заданном интервале изменения аргумента вычислить значение функции в5-10 раз точнее, чем при линейной аппроксимации, 1 ил. 2жуточный сумматор 40, второй 41, третий 42, четвертый 43 сумматоры откорректированных сумм, информационныевыходы 44-47 первого, второго, третье.го, четвертого сумматоров откорректированных сумм, пятый регистр 48, шестой регистр 49, седьмой регистр 50блока выходных регистров, одиннадца,тый 51 и двенадцатый 52 выходы блокауправления.Устройство функционирует следующимобразомИнтервал изменения аргумента разибивается на 2 участков ,и - старшиеразряды аргумента без знакового разряда ) еНа каждом из участков функции аппроксимируется кривая второго порядка видау = Ах + Вх + С,коэффициенты которой АВ и С подбираются исходя из минимального значения среднеквадратичной ошибки по методу наименьших квадратов.Аргумент х, коэффициенты А,В и Си функции у представляются в видеК 3.-разрядных двоичных групп. В частном случае при двоичной разрядностиаргумента х, коэффициентов А, В, Си функции равной 24 двоичных разрядов целесообразно принять и = 7,К=З, 1=8,Вычисление функции выполняется посхеме Горнера, т.е, вычисляетсяУ = (Ах+ В) х+ С.В первом такте по сигналу с второго выхода 23 блока 20 управления врегистр 10 аргумента поступает трехбайтовый аргумент, у которого в левом (первом) байте левый (старший)двоичный разряд знаковой, а по сигналу с одиннадцатого выхода 51 блока 20 управления обнуляются регистры с первого по седьмой 5-8,48-50 блока выходных регистров.Во втором такте из первого блока 1 памяти констант аппроксимации по адресу, задаваемому и старшими разря.дами х, с помощью сигнала с первого 10 выхода 22 блока 20 управления извлекается третий (младший) байт константы А (а) и через четвертую группу элементов ИЛИ поступает на входы вторых сомножителей умножителей 16-18, 15 на входы первых сомножителей которых по сигналу с третьего 24 выхода блока 20 управления с регистра 10 аргумента на первую, вторую и третью группы элементов ИЛИ поступают бай ты аргумента х: на умножитель 16 старшего байта (байт х,), на умножитель 17 среднего байта (байт х), на умножитель 18 младшего байта (байт х ). 25В третьем такте по сигналу с девя" того 30 выхода блока 20 управления операнды а и х вводятся в соответствующие умножители 16-18 старшего, среднего и младшего байта. 30В четвертом такте по сигналу . с десятого 31 выхода блока 20 управления результаты умножения х.,а, хаи х а с выхода умножителей 16-18 старшего, среднего и младшего байта поступают .на промежуточных суммато" ров 39 и 40 и сумматоров 38, 41-43 промежуточных сумм, т.е, выполняется и начинается процесс вычисления величины х а по правилу 40+(сБ + а;Б ) + (сБ + а,Б ) Величины с, и а, появляются на выходах умножителя 16 старшего байта, величины с и а - на выходах умно жителя 17 среднего байта, величины с и а - на выходах умножителя 18 младшего байта.50В пятом такте по сигналу с одиннадцатого 51 выхода блока 20 управле,ния содержимое сумматоров 38,41-43 заносится соответственно в регистры 5-8 блока 4 выходных регистров. 55 На этом заканчивается цикл умножения аргумента х на младший байт а коэффициента А. Далее производится умножение аргумента х на средний байт а коэффициента А и на старший байт а коэффициента А. Это выполняется в тактах,на чиная с второго,в котором из первого блока 1 памяти по адресу задаваемому и старшими разрядами х с помощьюсигналов с четвертого 25,а затем с пятого 26 выходов блока 20 управления, извлекается второй (а ) и первый (Ь,) байты константы А.После того как закончились три цикла умножения аргумента х на А в регистрах .6-8, 48-50 находятся шесть байтов этого произведения.Далее по сигналу с шестого выхода 27 блока 20 управления по адресу, заданному старшими разрядами аргумента х, с второго блока 2 памяти констант через аппроксимации первую, вторую и третью группы элементов ИЛИна умножители 16-18 поступают байты коэффициента В: на умножитель 16 старшего байта Ь на умножитель 17 среднего байта Ь , на умножитель 18 младшего байта Ь , Одновременно по2сигналу восьмого выхода 29 блока 20управления с регистра 19 константычерез четвертую группу элементов ИЛИна входы вторых сомножителей умножителей 16-18 поступает байт константы "1" вида 00000001,В последующие два такта по сигналам с девятого 30 и десятого 31 выходов блока 20 управления в умножителях 16-18 вычисляется величина В.1. В результате работы блока 3 ".умматоров величина Ах + В 1 сформирована на выходах 45-47 блока 3 сумматоров,на выходе 44 блока 3 сумматора имеется нуль.Далее по сигналу с одиннадцатого выхода 51 блока 20 управления содержимое сумматоров 38, 41, 42 и 43 блока 3 суммирования заносится в регистры 5-8 регистра 4 функций, а содержимое регистров 48 и 49 смещается вправо на один байт. В результате на 5=0, .6=Б(, 7=Б , 48=Б, 49=8,50=Б 1Содержимое регистров 6-8 и 48 необходимо сместить на два байта вправо так, чтобы в регистре 50 находился четверый байт величины Ах+В.Такой сдвиг в устройстве выполняется двумя циклами умножения х на "0".Это умножение выполняется по сигналу восьмого выхода 29 блока 20 управления, при котором с регистра 19 константы на входы вторых сомножителейумножителей 16-18 подается байт константы "0" вида 00000000, в то времякак на входы первых сомножителей умножителей 16-18 поступает х.По сигналам с девятого 30 и десятого 31 выходов блока 20 управления вумножителях 16-18 умножается Х на "0" 10На их выходах появляются нули, которые суммируясь на сумматорах 41-43откорректированных сумм с содержимымпервого 5 второго 6 и третьего 7 регистров по сигналу с одиннадцатого 15выхода 51 блока 20 управления позволяет сдвинуть их содержимое на одинбайт вправо, повторив такое умножение дважды содержимое регистров блока 4 выходных регистров на два байта 20вправо. Поскольку в эти два цикла сдвенадцатого выхода 52 блока 20 управления сигнал не подается, то содержимое регистра 50 на выход не выдается. 25В следующие четыре цикла при наличии двенадцатого сигнала 52 производится умножение аргумента х на четыре байта величины Ах+В.1, т,е. вы-.числение (Ах+В,1):Х. Послекаждого 30цикла умножения.(Ах+В1); Х (т=1-4)в порядке (Ах+В.1)Х (Ах+В.1)Х (Ах+, +В.1)Х, содержимое регистров блока 4выходных регистров сдвигается на одинбайт вправо, в результате чего вподрегистрах 5-8, 48 и 50 находитсясемь старших байтов проведения(Ах+В 1)Х прибавляется величина С,1, 40Этот цикл выполняется аналогичноциклу Ах+В.1.В результате в первом регистреимеется нуль, а с второго по седьмой(6-8,48 и 50) соответствующие байтыфункции у. Поскольку аргумент х икоэффициенты А,В и С трехбайтовые,то и результат может быть толькотрехбайтовым, потому что в байтахпятого 48, шестого 49 и седьмого 50регистров имеются неточные цифры.Поэтому вычисленное значение функцииу снимается с второго 6, третьего 7,четвертого 8 регистров блока 4,55Формула изобретенияУстройство для вычисления функ" ций табличным методом, содержащее.первый и второй блоки памяти констант аппроксимации, блок суммирования, блок умножения и блок управления, причем первый, второй и третий выходы блока управления соединены с входами старших разрядов адреса первого блока памяти констант аппроксимации, о тл и ч а ю щ е е с я тем, что, с целью повышения точности за счет применения квадратичной аппроксимации, в него дополнительно введены регистр аргумента, блок выходных регистров, регистр константы, четыре группы элементов ИЛИ, причем блок умножения содержит умножитель старшего байта аргумента, умножитель среднего байта аргумента, умножитель младшего байта аргумента, а блоксуммирования содержит два промежуточных сумматора и четыре сумматора откорректированных сумм, причем вход аргумента устройства соединен с информационными входами регистра аргумента, выходы старшего байта которого соединены с входами младших разрядов адреса первого блока памяти . констант аппроксимации и с входами старших разрядов адреса второго блока памяти констант аппроксимации,выходы старшего, среднего и младшегобайтов регистра аргумента соединеныс первыми входами элементов ИЛИ соот"ветственно первой, второй и третьей групп вторые входы которых соединены соответственно с выходами старшего, среднего и младшего байтов второго блока памяти констант аппроксимации, выходы элементов ИЛИ первой, второй и третьей .групп соединены с входами первых сомножителей соответственно умножителей старшего, среднего и младшего байтов блока умножения,чвходы вторых сомножителеи которых соединены с выходом элементов ИЛИ четвертой группы, первые и вторые входы которой соединены с выходом первого блока памяти констант аппроксимации и выходом регистра константысоответственно, выходы старших разрядов умножителей старшего, среднего имладшего байтов соединены с входами первых слагаемых соответственно первого сумматора откорректированныхсумм, первого промежуточного сумматора и второго промежуточного суммато. ра, выходы младших разрядов умножителей старшего и среднего байтов соединены с входами вторых слагаемых соот383337 Составитель С, КуликовТехред Л.Олийнык Корректор О.Кравцова Редактор Н.Бобкова Заказ 297/47 Тираж 704 ПодписноеВНИИПИ Государственного комитета СССРпо делам изобретений и открытий3035, Москва, Ж"35, Раушская наб., д.4/5 Производственно"полиграфическое предприятие, г.Ужгород, ул.Проектная,4 ветственно первого и второго промежуточных сумматоров, выходы которыхсоединены с входами первых слагаемых соответственно второго и третьего сумматоров откорректированных сумм,вход первого слагаемого четвертогосумматора откорректированных суммсоединен с выходами младших разрядовумножителя младшего байта, выход пере 10носа второго промежуточного сумматора соединен с входом переноса первого промежуточного сумматора, выходпереноса которого соединен с входомпереноса первого сумматора откорректированных сумм, вход второго слагаемого которого соединен с выходом переноса второго сумматора откорректированных сумм, вход переноса которого соединен с выходом переноса третье.20го сумматора откорректированных сумм,вход переноса которого соединен свыходом переноса четвертого сумматора откорректированных сумм, выходысумматоров откорректированных сумм с 25первого по четвертый соединены с информационными входами соответственнорегистров с первого по четвертыйблока выходных регистров, выходы регистров с первого по третий блок выходных регистров соединены с входами вторых слагаемых соответственновторого, третьего и четвертого сумматоров откорректированных сумм, выходы регистров с четвертого по шестой 35блока выходных регистров соединены с информационными входами регистров соответственно с пятого по седьмойблока выходных регистров, выходыседьмого регистра блока выходных регистров соединены с третьими входамиэлементов ИЛИ четвертой группы, выходы регистров с второго по четвертый блока выходных регистров являются выходами вычисляемой функции устройства, вход запуска которого соединен с одноименным входом блока управления, четвертый и пятый выходы которого соответственно соединены с входами стробирования занесения и выборкиаргумента, регистра аргумента, шестой и седьмой выходы блока управления соединены соответственно с входами младших разрядов адреса второгоблока памяти констант аппроксимации,восьмой выход блока управления соединен с входом стробирования сборкирегистра константа, девятый и десятый выходы блока управления соединены с входами соответственно стробирования умножения и разрешения выборки умножителей старшего, среднего,младшего байтов, одиннадцатый выходблока управления соединен с синхронизирующими входами регистров с первого по седьмой блока выходных регистров, двенадцатый выход блока управления соединен с входом стробированиявыборки седьмого регистра блока выходных регистров.

СмотретьЗаявка

4074114, 15.05.1986

ПРЕДПРИЯТИЕ ПЯ А-7638

МАРКИН АЛЕКСАНДР ВАСИЛЬЕВИЧ, ЕВСТИГНЕЕВ ВЛАДИМИР ГАВРИЛОВИЧ, КОШАРНОВСКИЙ АЛЕКСАНДР НИКОЛАЕВИЧ, КУЗЬМИНА ГАЛИНА ФЕДОРОВНА, ДЕМИН ВЛАДИМИР ВЛАДИМИРОВИЧ

МПК / Метки

МПК: G06F 7/38, G06F 7/544

Метки: вычисления, методом, табличным, функции

Опубликовано: 23.03.1988

Код ссылки

<a href="https://patents.su/5-1383337-ustrojjstvo-dlya-vychisleniya-funkcii-tablichnym-metodom.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления функции табличным методом</a>

Предыдущий патент: Устройство для упорядочения массива чисел

Следующий патент: Параллельное устройство для умножения в конечных полях

Случайный патент: Установка для выгрузки незатаренной рыбы из емкостей