Патенты с меткой «умножения»

Устройство для контроля умножения по модулю три

Номер патента: 1348836

Опубликовано: 30.10.1987

Авторы: Воронцова, Моисеев, Потоцкий

МПК: G06F 11/10

...на второй регистр 2. На первый регистр 1 осуществляется запись контрольного кода первой группы разрядов множителя, сформированного на первом узел 9 свертки по мо- Фдулю три. Результат умножения контрольных кодов множимого и множителя поступает с узла 15 умножения по модулю три на третий сумматор 19 по модулю три, где осуществляется его сложение с содержимым пятого регистра 5 (в первом такте его значение равно нулю). Контрольный код результата умножения первого такта записывается на четвертый регистр 4.В начале второго такта на узлах 11, 13 свертки по модулю три форми 40 руются контрольные коды поразрядных сумм и переносов первого промежуточного произведения блока 7 умножения, Далее на узле 14 осуществляется инвертирование по...

Устройство для умножения чисел в модулярной системе счисления

Номер патента: 1352483

Опубликовано: 15.11.1987

Авторы: Коляда, Ревинский, Селянинов, Чернявский

МПК: G06F 7/72

Метки: модулярной, системе, счисления, умножения, чисел

...информационный вход первого блока 14 мультиплексоров поступает в первый блок 19 вычисления интервального индекса числа Где в течение Очередных Т так О тов, считая текущий, в соответствии с формулой (3) будет вычислен машинный интервальный индекс 1(В) числа В, модулярньй код (,",л,) подается также на третий адресный вход блока 15 памяти, на второй и первый входы разрешения выдачи которого с второго и первоГО выходов 631 оеа 8 поступают11 3.М соответственно сигнаы д,= Ои = "1", В результате 1.а первом и (150 +1)-ом выходах блока 5 памяти сформируются соответственно наборы вычеК) в согокупности передаются на трет.й вход блока 3 вычисленияинтервального идакса произведения,на второй вход которого подается модулярный код числа с выхода...

Цифровой умножитель частоты с переменным коэффициентом умножения

Номер патента: 1354386

Опубликовано: 23.11.1987

Авторы: Капишников, Кункулис, Назарчук

МПК: H03B 19/00

Метки: коэффициентом, переменным, умножения, умножитель, цифровой, частоты

...пор, пока делитель 5не подсчитает число импульсов, равноеего коэффициенту деления, а затемразрывает цепь импульсной обратнойсвязи, так как на его выходе появляется уровень логического нуля, которым закрывается элемент И 6, На выходе цифрового умножителя с переменным коэффициентом умножения импульсыравномерно расположены в периодевходного сигнала. Значение входнойчастоты определяется путем записиколичества импульсов с выхода кварцевого генератора 1 в регистр 7 запериод входного сигнала, Полученныйдвоичный код переписывается при последующем входном импульсе в регистр8, где хранится в течение следующегопериода входной частоты, а затем 35405055 поступает на дешифратор 9, В дешифраторе 9 по двоичному коду регистра 8 и коэффициенту деления 5...

Устройство для контроля умножения по модулю три

Номер патента: 1361556

Опубликовано: 23.12.1987

Автор: Варакин

МПК: G06F 11/08

...контрольного кодагруппы 5, результат на выходе шестиразрядного сумматора 6 будет иметьследуюттее значение 1010100 35Свертка результата шестиразрядного сумматора 6 равна для данного случая значению 00 тна выходе узлаIсвертки по модулю три).На сумматоре 8 по модулю три код 4000 суммируется со значением СВИ=01,н результате на выходе Формируетсякод 01, который и является контрольным кодом устройства,В устройстве умножения по аналогичньм управляющим сигналам НС; СФормируются частичные произведениян дополнительном коде.О О О О О О О О0 О О О О О О О 50+110000001111111 1,10111101Свертка результата умножения с учетом переноса из старшего разряда результата имеет значение 01, т.е. совпадает с результатом устройства для контроля...

Устройство для умножения чисел в модулярной системе счисления

Номер патента: 1368878

Опубликовано: 23.01.1988

Авторы: Амербаев, Коляда, Селянинов, Чернявский

МПК: G06F 7/72

Метки: модулярной, системе, счисления, умножения, чисел

...случае11 ервый элемент 15 задержки осуществляет задержку на (Т+Те +5) тактов. 8878 2вается константа У, =/Х,/ ше/тп;,Х У; 50,1 ш;-1 1=11-1,Блок 18 вычисления интервальногоиндекса числа служит для определенияпо входному модулярному коду (М,от,Е) ЧИСЛа А, ГдЕ М; =/А/а МаШИНного интервального индекса числа поформулее- /М е, от, /тп1 (А) = +,1 ) передается на вход блока19 суммирования вычетов, которые втечение очередных Т тактов, считаятекущий, вычисляют соответственновеличины 1(С) и 1 (формулы (1)и (3),На (Т+Т+5)-м такте работы величины 1(С) с выхода блока 18 вычисления интервального индекса числа ил(С) с выхода блока 17 суммирования вычетов поступают на входы схемы 21 сравнения с константой, 15На (Т+Т +6)-м такте работы величины 1(С) с...

Устройство для умножения

Номер патента: 1368882

Опубликовано: 23.01.1988

Автор: Шостак

МПК: G06F 7/52

Метки: умножения

...2суммирования. Сумматор содержит элементы И 78-81, элементы ИЛИ 82-84,элемент НЕ 85 и элемент 86 сложенияпо модулю два. Схема этого сумматора35известна и описывается следующими логическими выражениями: Функция генерации переноса,Функция транзита пере носа,сумма, перенос и дублирующий перенос соответственнофразрядные слагаемые 50 сумматора. С помощью элемента И 3 и первого блока 4 свертки по модулю два на выходе последнего Формируется значение предсказываемой четности результата устройства в соответствии с соотношением;Р, = Р Р 1 дРЯРОЮ Рсд,четкости соответственномножимого Х и множителяу1Р , Рь - четности соответственнопервого А и второго Вслагаемых,Р - четность дублирующих песреносов блока 2 суммирования,Р - предсказываемая...

Устройство для умножения -разрядных чисел

Номер патента: 1374217

Опубликовано: 15.02.1988

МПК: G06F 7/52

Метки: разрядных, умножения, чисел

...прием в накапливающий сумматор 3 с его разрядных входов инверсного значения информации, а также запись единицы в первый разряд буферного регистра 26, На этом первый такт работы устройства заканчивается, 40Во втором такте одновременно с выполнением суммирования в накапливаю-. щем сумматоре 3 и формированием в нем промежуточного результата, равного 0,0000010011, выполняются следующие действия. На выходах суммы комбинаци-онного сумматора 27 формируется значение 8=8 Б 8,=010+001+001=100, в результате чего на выходе третьего элемента И 23 третьей группы 22 образуется сигнал " 1". Этот сигнал выполняет следующие действия: во-первых, через третий элемент И 19 первой группы 18 и первый элемент ИЛИ 24 настраивает коммутаторы 5 группы 4 на...

Устройство для умножения напряжений

Номер патента: 1374253

Опубликовано: 15.02.1988

Автор: Гантимуров

МПК: G06G 7/16

Метки: напряжений, умножения

...вход 5 первого сигнала-сомножителя, вход 6 сигнала-сомножителя, выход 7, первый ивторой масштабные резисторы 8 и 9,операционный усилитель 10, интегрирующий конденсатор 11,Э-триггер 12, 20шину 13 нулевого потенциала, третий,четвертый, пятый и шестой масштабные резисторы 14-17, дополнительныйоперационный усилитель 18, дополнительный интегрирующий конденсатор 19, 25зарядный резистор 20 и накопительныйконденсатор 21.Устройство для умножения напряжений работает следующим образом.На вход 5 подается первый сигналсомножитель в виде напряжения, навход 6 - второй сигнал сомножительв виде тока. Первый сигнал сомножитель в первом широтно-импульсноммодуляторе 1 преобразуется в скважность импульсов, которые подаются напервый вход элемента 3...

Устройство для умножения и деления

Номер патента: 1376082

Опубликовано: 23.02.1988

Авторы: Заблоцкий, Самусев, Спасский, Шостак

МПК: G06F 7/52

Метки: деления, умножения

...такт (до корректирующего такта).Сумматор 5 предназначен для округления кода старших разрядов делителя путем прибавления к нему логической единицы, подаваемой через вход 16. При этом на выходе сумматора 5 может сформироваться код, имеющий количество разрядов на единицу большее, чем входной код. Это происходит в том случае, если во всех разрядах входного кода установлена логическая единица.- В этом случае на разрядах выхода 13 Формируется нулевой код, а на выходе 14 - логическая единица.Узел 6 деления предназначендля деления, например, %+1)-х разрядного двоичного числа, код которого установлен на входе 25 узла на %+3)-х разрядное двоичное число, код которого установлен на входе 13 узла, при условии, что оно не равно нулю, В случае, если...

Параллельное устройство для умножения в конечных полях

Номер патента: 1383338

Опубликовано: 23.03.1988

Авторы: Георгиева, Додунеков, Зиновьев, Зяблов, Манев, Попов, Савельев, Стойнов

МПК: G06F 7/49

Метки: конечных, параллельное, полях, умножения

...на примитивный элемент.Устройство работает по следующему алгоритму.Множимое и множитель обозначаютсяв -1-1А(х)аха;х и В(х)ах Ь;х (1)-О ах 0где Р - характеристика;и - степень расширения поля.Тогда произведение имеет вид А(х)В(х)= х )а;х ВСх =(г)а х В(х РПроизведение хВ(х) может быть представлено в виде, Ь,х (3) 1=0В регистрах 1 записаны произведе" ния базисных элементов на примитивный элемент, т.е, элементы ХР " (=0,1и), выходы которых соединены с 3-й группой входов блоков 2 умножения, куда подается величина)+Х . Содержимое регистров меняется при смене представления элементов поля. Компоненты элементов поля, поступающие на первую группу входов блока 2 умножения, умножаются на элементах И 6 на Х " , в результате чего получают члены...

Устройство для умножения по модулю м=2 -1

Номер патента: 1383339

Опубликовано: 23.03.1988

Автор: Вариченко

МПК: G06F 7/49

Метки: модулю, умножения

...для 2, = Е 7 можно записать соответствие: 0 О, 1- 1,2 2,3-е"3, 4- -3, 5 -2, 6 -1. В двоичной системе счисления эти числа можно представить трехразрядными двоич ными числами: -001 = 11 0 =. 6; -010 =101 = 5; -011 = 100 = 4, значит ум" ножение можно проводить по следующему выражению:а Ъ (тао 1 М) = (а Ь) (тос М), (1) с помощью блока 6 и корректируются блоком 7, на выходах 17, 17 17 которого формируются разряды сло. ва суммы частичных произведений. С этих выходов прямое значение слова суммы частичных произведений поступает на первые входы коммутатора 8, Кроме того, слово суммы частичных произведений инвертируется с помощью элементов НЕ 10 10 , , 10и подается на вторые входы коммутатора 8. Управляется последний с помощью того же...

Устройство для цифро-частотного умножения

Номер патента: 1383348

Опубликовано: 23.03.1988

Авторы: Дудыкевич, Опотяк, Отенко, Пархуць, Пастор

МПК: G06F 7/68

Метки: умножения, цифро-частотного

...узле 4 .вычитания импульсных последовательностей (фиг.2) инверсныйвход элемента И 22 и вход элемента 21задержки являются соответственно входами 5 и 6, выход элемента И 22 является выходом 7, прямой вход элемента И 22 подключен к выходу элемента21 задержки,В коммутаторе 8 (фиг.2) информамационный вход 9 подключен к первомувходу элемента И 24, второй вход которого подключен к выходу элементаНЕ 23, вход которого подключен к управляющему входу 11 и первому входуэлемента И 25, вход которого подключен к информационному входу 10, выход элемента И 25 подключен к первому входу элемента ИЛИ 26, второй входкоторого подключен к выходу элемента И 24, выход элемента ИЛИ 26 является выходом 12.В делителе 13 частоты на два(фиг.4)...

Устройство для контроля по модулю умножения комплексных чисел

Номер патента: 1386997

Опубликовано: 07.04.1988

Авторы: Дрозд, Карпенко, Лацин, Минченко, Полин

МПК: G06F 11/08

Метки: комплексных, модулю, умножения, чисел

...результатом второго узла 20 умножения по модулю гп.Узлы 4, 5, 2, 13, 16 и 24 формируют поправку, необходимую при отбрасывания младших разрядов из результата четвертого узла 17 вычитания по модулю п 1 с помощью пятого узла 17 вычитания по модулю гп.11 ри этом формируется сумма остатков по модулю действительной и мнимой частей мантиссы результата умножения. Третий узел 23 сложения по модулю гп суммирует остатки порядков множимого и множителя, образуя остаток порядка результата умножения.Проверочный контрольный код результа та умножения формируется пятым узлом 25 сложения по модулю е. Этот код сравнивается первым узлом 28 сравнения с кодом свертки результата умножения, поступающего на вход 30 устройства. При но- сравнении кодов появляется...

Устройство для умножения комплексных чисел

Номер патента: 1388851

Опубликовано: 15.04.1988

Авторы: Ваврук, Мельник, Цмоць, Яцимирский

МПК: G06F 7/49

Метки: комплексных, умножения, чисел

...операции на сумматоре-.вычитателе 30,По каждому тактовому импульсу производится запись информации в регистры 25, 28, 31 и 32, в триггеры 7, 10,26 и 27, сдвиг информации на одинразряд вправо в регистрах 5,6,8 и 9,а также уменьшение содержимого счетчика 1 на единицу,иПосле ( -- +1)-го тактового импульса2на выходе счетчика 1 получаем лог."1",которая блокирует поступление тактовых импульсов через элемент ИЛИ-НЕ 2и процесс умножения на этом заканчивается, Результат комплексного умножения получается на выходах 43 (действительная часть) и 44 (мнимаячасть).Время умножения комплексных чиселв устройстве равно:формула изобретенияУстройство для умножения комплексных чисел, содержащее шесть входных регистров, четыре промежуточных регистра, первый...

Устройство для умножения

Номер патента: 1388852

Опубликовано: 15.04.1988

Авторы: Биушкин, Валов, Герасимов

МПК: G06F 7/52

Метки: умножения

...множимого 11 и множителя 12 они через блок 8 деления минимальной и максимальной величины поступят на информационные входы 50 разностных узлов 9 и 10 управления, При этом на первом выходе 44 блока 8 выделения минимальной и максимальной величины будет множимое Х, если его значение больше или равно значению множителя У (Х Ъ У). В противном случае значение множимого Х будет присутствовать на втором выходе 45, а значение множителя У -на первом выходе 44 блока 8 выделения минимальной и максимальной величины. Таким образом, разностныйузел 9 управления будет всегда отрабатывать большее или равное иэ двухзначений Х, У, а узел 10 - соответственно меньшое из них. Этим, вопервых, повышается быстродействиеустройства эа счет сокращения числашагов...

Устройство для умножения частоты на коэффициент

Номер патента: 1388860

Опубликовано: 15.04.1988

Авторы: Плиш, Сергейчук, Ходырев

МПК: G06F 7/68

Метки: коэффициент, умножения, частоты

...На счетныйвход делителя 3 поступают импульсы свыхода генератора 6. Последовательнос делителем 3 включен делитель 2, Импульсы низкого уровня с выхода делителя 2 поступают на вход сложения счетчика 5 и через элемент ИЛИ 4 на входы обнуления делителей 1,2 и 3, Период формирования импульсов на выходе делителя 2 равен Т = Т Квыл 2 ф где Т . - период импульсов на выходеемделителя 3 и выходе 8 устройства; К - коэффициент деления делителя 2, Поскольку сигнал с выхода элемента ИЛИ 4 поступает на входы сброса всех делителей одновременно, то начало периодов импульсов на выходах делите" лей 1 и 2 совпадает во времени. Если оказывается, что Т,Т , то первым во времени появляется импульс на выходе делителя 2. Этот импульс увеличивает содержимое...

Устройство для умножения на коэффициенты

Номер патента: 1397901

Опубликовано: 23.05.1988

Авторы: Волков, Рощинский, Титов, Титова

МПК: G06F 7/49

Метки: коэффициенты, умножения

...регистре 2 и первом коммутаторе 8.По мере выхода из регистра 5 множимого младших разрядов множимого, в регистр 5 множимого на освободившееся место вновь с выхода первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 13 записывается значение множимого или число, ему инверсное, что определяется состоянием регистра 11 знака множимого.Причем в связи с тем, что в начале каждого цикла умножения третий сдвиговый регистр 4 обнуляется, между старшим разрядом множимого, первоначально записанного в регистр 5 мно" жимого, и младшим разрядом вновь записываемого множимого формируется В (ВО) нулей (единиц), В результате после К тактов вычисления в регистре 5 множимого формируется число, состоящее из В нулей и К - В младших разрядов множимого, или число, инверсное...

Параллельно-последовательное устройство для умножения в конечных полях

Номер патента: 1399725

Опубликовано: 30.05.1988

Авторы: Георгиева, Додунеков, Зиновьев, Зяблов, Манев, Попов, Савельев, Стойнов

МПК: G06F 7/49

Метки: конечных, параллельно-последовательное, полях, умножения

...которых соединены соответственно с выходами блока Формирования частичных произведений, выходы и сумматоров соединены состветственно с инФормационными входами регистра произведения, разрядные выходы которого соединены с вторыми входами п сумматоров блока суммирования с циклическим сдвигом на один разряд в сторону младших разрядов и являются выходом устройства. 1. Параллельно-последовательное 40 устройство для умножения в конечных полях, содержащее блок формирования частичных произведений и блок суммирования, о т л и ч а ю щ е е с я тем, что, с целью упрощения устрой ства, в него введены регистр сдвига множителя, регистр сдвига множимого, блок умножения на примитивный элемент и регистр произведения, причем информационные входы первой...

Устройство для умножения

Номер патента: 1399728

Опубликовано: 30.05.1988

Авторы: Васылив, Дудыкевич, Максимович, Токарчук

МПК: G06F 7/52

Метки: умножения

...Результат преобразования И фиксиР руется в счетчике 4, При с, = 1 им" пульсы с выхода двоичного умножителя 2 через коммутатор 7 поступают на входы ш-го разряда счетчика 4, состояние которого определяет значениемразряда И с весом 2 . Таким образом при с , = 1 И=Ез., 2(8)35 Из уравнений (3)- (8) следует, что в диапазоне (1) устройство работает аналогично известному устройству. При этом вес в результате преобразования младшего задействованного 40й в работе разряда счетчика 4 равен 2Рассмотрим работу устройства в общем виде. Пусть(9) фактический результат преобразования зафиксированный всчетчике 4;Е , - фактическое число импульсов, прошедших на выходдвоичного умножителя 2,При произвольно выбранном значении Я в работе устройства принимает...

Устройство для умножения

Номер патента: 1399729

Опубликовано: 30.05.1988

Авторы: Батюков, Заблоцкий, Самусев, Спасский, Шостак

МПК: G06F 7/52

Метки: умножения

...коммутатор 5 второй группы с выходов (г)-го буферного регистра 3 второй группы. Фактически во втором такте работы устройства с помощью блоков 1, -1, и коммутаторов 4 4 -4, 5, -5 осуществляются формирование значения второго частичного . произведения и-разрядного множимого К разрядов второй со стороны младших разрядов группы разрядов и-разрядного множителя и прибавлениеего к эна 50 чению первого частичного произведения, образованному в первом такте и сдвинутому на К разрядов вправо (в сторону младших разрядов).После выполнения ш-го такта в буферных регистрах 2,-2 , 3,-3 запоминаются в двухрядном коде и старших разрядов 2 п-разрядного произведения и-разрядных сомножителей, и младшихразрядов которого по К разрядов вкаждом также уже выведены...

Устройство для умножения

Номер патента: 1401454

Опубликовано: 07.06.1988

Автор: Макаров

МПК: G06F 7/52

Метки: умножения

...элементов О И 16 и 17, а работа элементов И 14 и 15 запрещается, если Ь 7 О, то схема 9 сравнения выдает сигнал "Больше",при том содержимое счетчика 2 увеличивается на единицу, а к содержимому сумма тора 10 прибавляется код счетчика 1. Если Ь ( О, то схема 9 сравнения выдает сигнал "Меньше", а из содержимого счетчика 2 и сумматора 10 вычитается соответственно единица и код счетчика Таким образом, в нечетных подтактах работы сравниваются коды счетчи 544ка 1 и регистра 3, к содержимому сумматора прибавляется или отнимаетсякод счетчика 2, а в четных подтактахсравнивают коды счетчика 2 и регистра 4, т.е, происходит попеременныйанализ кода множителя и множимого,при этом коды в счетчиках 1 и 2 изменяются в таком направлении,...

Устройство для умножения комплексных чисел

Номер патента: 1401455

Опубликовано: 07.06.1988

Авторы: Крыкина, Мартазова, Филашов, Цилькер

МПК: G06F 7/52

Метки: комплексных, умножения, чисел

...по (1), Для того, чтобы можно было выполнять сложение аргументов векторов, в блоках.3 и 4 аргументы кодируются в виде иразрядных чисел, соответствующих расположению вектора на окружности в27 В и д могут принимать значения отОдо 2 - 1.На первом выходе блока 3 имеем величину А, равную модулю вектора а, навтором выходе блока 3 имеем величинуравную аргументу вектора а, напервом выходе блока 4 имеем величинуВ, равную модулю вектора Ь, на второмвыходе блока 4 имеем величину О, рав"ную аргументу вектора Ь. Блоки 3 и 4выполнены на микросхеме ПЗУ 556 РТ 7 и1/4 части микросхемы 133 ЛП 5. Аргументы и Ввекторов а и Ь поступают напервый и второй входы сумматора 6, навыходе которого образуется сумма+ Ор равная аргументу вектора а х Ь,которая...

Устройство для выполнения операций умножения и деления

Номер патента: 1403061

Опубликовано: 15.06.1988

Авторы: Кондрашев, Курахтанов, Румянцев

МПК: G06F 7/52

Метки: выполнения, деления, операций, умножения

...поступает с выхода 70 блока 3 на входФОях) ц,е с;Осетеи) элемента ИСКЛ Ю 11 АЮШЕЕ ИЛИ 22 для сравнения со знаком делителя. После сравнения ца вьходе 77 элемента ИСКЛОс)УЮЩЕЕ ИЛИ 22 появляется значение очерелного разряда частного. В старием молулс это значение вылается на выход 49 устройства.После вычисления очередного частичного остатка содержимое блока 3 сдвигаеся н) единичному знацению сигнала на выходе 68 блока 5 влево на один разряд в каждом модуле. При этом сигнал с выхода блока 3 выдается на выход 4 устройства, соединенного с входом 34 нулевого разряда сосслнего более старшего модуля, и заполняет освободившийся при сдвиге младший разряд в блоке 3 суммирования.В младшем модуле на вход 34 блока 3 поступает сигнал с выхода 29...

Устройство для умножения десятичных чисел

Номер патента: 1410023

Опубликовано: 15.07.1988

Авторы: Гигаури, Кожемяко, Мартынюк, Натрошвили, Чхаидзе

МПК: G06F 7/52

Метки: десятичных, умножения, чисел

...сигнала с выхода элемента И 23 на К-вход КБ-триггера 21 во время считывания информации из соответствующего сумматора 2 блока 1. Возможен случай, когда одновременно в двух или более ячейках 20 блока 5 по явились сигналы нулевого содержимого, например, в первой и во второй ячейках 20, В этом случае появление единичного сигнала на выходе элемента И 23 первой ячейки 20 совпадает с блокировкой, которая через элементы И-ИЛИ 28 запрещает срабатывание элементов И 23 всех следующих ячеек 20. Таким образом, считьвание в каждом такте работы устройства выполняется только из одного соответствующего сумматора 2 блока 1, Одновременно с этим во второй ячейке 20 отсутствует единичный сигнал, как на выходе элемента И 23, вызывающий считывание из...

Устройство для умножения

Номер патента: 1410024

Опубликовано: 15.07.1988

Авторы: Гребенников, Иванова, Калугин

МПК: G06F 7/52

Метки: умножения

...равна нулю, прибавление 25 н производится, затем производится д иг суммы частичных произведений с н ин разряд и сдвиг этом если сумма о в а одПрито ос атся модифициерации последля всех циствл ныи дви ро тель о ыполняютс зрядов множи о. Если множ полученный р ф еля, начиная тель положидше те 1 ьныи,ст вляетте ь отри оизведение. Ес тельный, то дл ий из результат и множиполучения вычитаетизвед ,множи В исх 2 мн с е.ном со.тоянии в регистрахмножителя хранятсястр 3 произведений жимого и, ре т со н. В завис младшего р 4 выполня алости от .зряда мн т операц на выход о че жителя с либо п ма 1 о реда ибо сло 4 множимог жен С приходом тактового вход 5 устройства получ передается с выхода сум регистр 3 произведений. мпульса ная топ мма наПри этом...

Устройство для умножения частоты следования импульсов

Номер патента: 1410027

Опубликовано: 15.07.1988

МПК: G06F 7/68

Метки: импульсов, следования, умножения, частоты

...передаваться содержимое блока 4 памяти. После того как сработают все дешифраторы 1 Е, -11 , что соответствует выходу на линейный участок характеристики преобразования, на выходе старшего разряда счетчика 13 будет сформирован сигнал, который установит триггер 14 в единичное состояние. В этомслучае сигналом с прямого выхода триггера 14 в блоке 5 параллельного переноса будет открыта группа элементов И 15, - 15, а группа элементов И 16 - 16 будет закрыта, При этом в регЕестр ) будет переписываться содержимо счетчика 2. После каждого обнуле)пен е)ее)ерс)ЕвеЕого счетчика 7 ОЕРГ;1 нЕ 1 1111,.Ел 1 Остуа 1)цЕЕЙ ЕЯ1410027 его вычитаюший вход с выхода генератора 9 тактовых импульсов, устанавливает все его выходные разряды в единицу, Сигнал с 2 -го...

Устройство для умножения

Номер патента: 1411733

Опубликовано: 23.07.1988

МПК: G06F 7/49

Метки: умножения

...занесение в первом такте старшего разряда множимого А наинформационные входы триггеров 6 и 7всех модулей поступают текущие значения положительных и отрицательныхразрядов множимого, Далее, проходяпо цепи, состоящей из последовательно включенных элементов 5 потактнойзадержки всех модулей, единичный импульс разрешает поочередное занесе"ние разрядов множимого в триггеры 6и 7 модулей соответствующих разрядов.На тактирующие входы триггеров 8и 9 модулей 4 старшего разряда управляющий сигнал йоступает во втором такте (с выхода элемента 5 задержки модуля). На информационныевходы триггеров 8 и 9 модулей всехразрядов последовательный код множителя В поступает задержанным наодин такт элементами 1 и 2 задержки, Таким образом, первый...

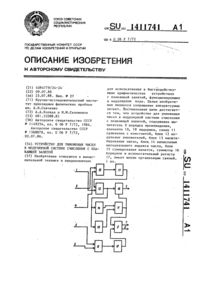

Устройство для умножения чисел в модулярной системе счисления с плавающей запятой

Номер патента: 1411741

Опубликовано: 23.07.1988

МПК: G06F 7/72

Метки: запятой, модулярной, плавающей, системе, счисления, умножения, чисел

...являющегося оценкойдроби А В Я/М, выходит за пределыинтервала-р - 1, р - 1, то число35С 1 Р, В этом случае дробь С /М, гдеС - оценка дроби А В/М, являетсянормализованной и, следовательно,представляет собой мантиссу результата, в противном случае в качествемантиссы результата принимается дробьС/М. При этом в первом случае порядок результата определяется соотношением 4(С) = 1(а) + 4(В), а во втором - соотношением (С) = 1(а) +45+ 4 (В) - 1,Устройство работает следующим образом.На первом такте работы модулярныекоды (с 1,с(,) числителя А мантиссы М(а) и (1"1,) числителя В мантиссы М(В) с входов 3 и 4 поступаютсоответственно на первый и второйвходы блока 12 модульных умножителей,который получает модулярный код(ъ ъ) произведения С = А"В,...

Последовательно-параллельное устройство для умножения чисел

Номер патента: 1413625

Опубликовано: 30.07.1988

Авторы: Масленников, Шарипов

МПК: G06F 7/52

Метки: последовательно-параллельное, умножения, чисел

...вход которого соединен с входом 7, а выход соединен с входом регистра 3, Старший (знаковый) выходрегистра 6 соединен с первым входомэлемента И 10, второй вход которогосоединен с входом 13, а выход - свходом переноса сумматора 11, Выходы 50элементов И 5 соединены с соответствующими входами параллельного счетчика9, выходы которого соединены .со входами накапливающего сумматора 11,выход младшего разряда которого является выходом 12 результата устройства.Устройство работае-ледующим образом,Перед выполнением операции умножения производится обнуление регистра 3 и накапливающего сумматора 11, а в регистр б загружается множитель. При выполнении операции на вход регистра 3 в первые щтактов работы поступает последовательный код множимого, а...

Устройство для умножения

Номер патента: 1418706

Опубликовано: 23.08.1988

Авторы: Веревкин, Галабурда, Ильин, Лачугин, Могилко

МПК: G06F 7/52

Метки: умножения

...31 для управления сдвигом регистров 23 и сумматоров 24, в результате чего сдвигается на один разряд .вправо содержимое регистров 23 и сумматоров 24, открываются элементы И 41 по первому входу, закрываются элементы И 42, на входы 30 узлов 25 блоков 1 и 2 поступает значение следующего разряда соответственно первого и второго сомножителей. Пусть теперь это значение равно нулю для перного и второго сомножителя. Тогда открывают"87064 5 10 15 20 3 141 ся элементы И 40 и закрываются элементы И 41 по второму входу. Третий импульс с входа 29 поступает на входы 27 и 28 блоков 1 и 2, через открытые элементы И 29 и 40 и элементы ИЛИ 44 поступает на счетные входы счетчиков 45 и на выходы 31 для управления сдвигом регистров 23 и сумматоров 24, В...