Устройство для умножения десятичных чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1410023

Авторы: Гигаури, Кожемяко, Мартынюк, Натрошвили, Чхаидзе

Текст

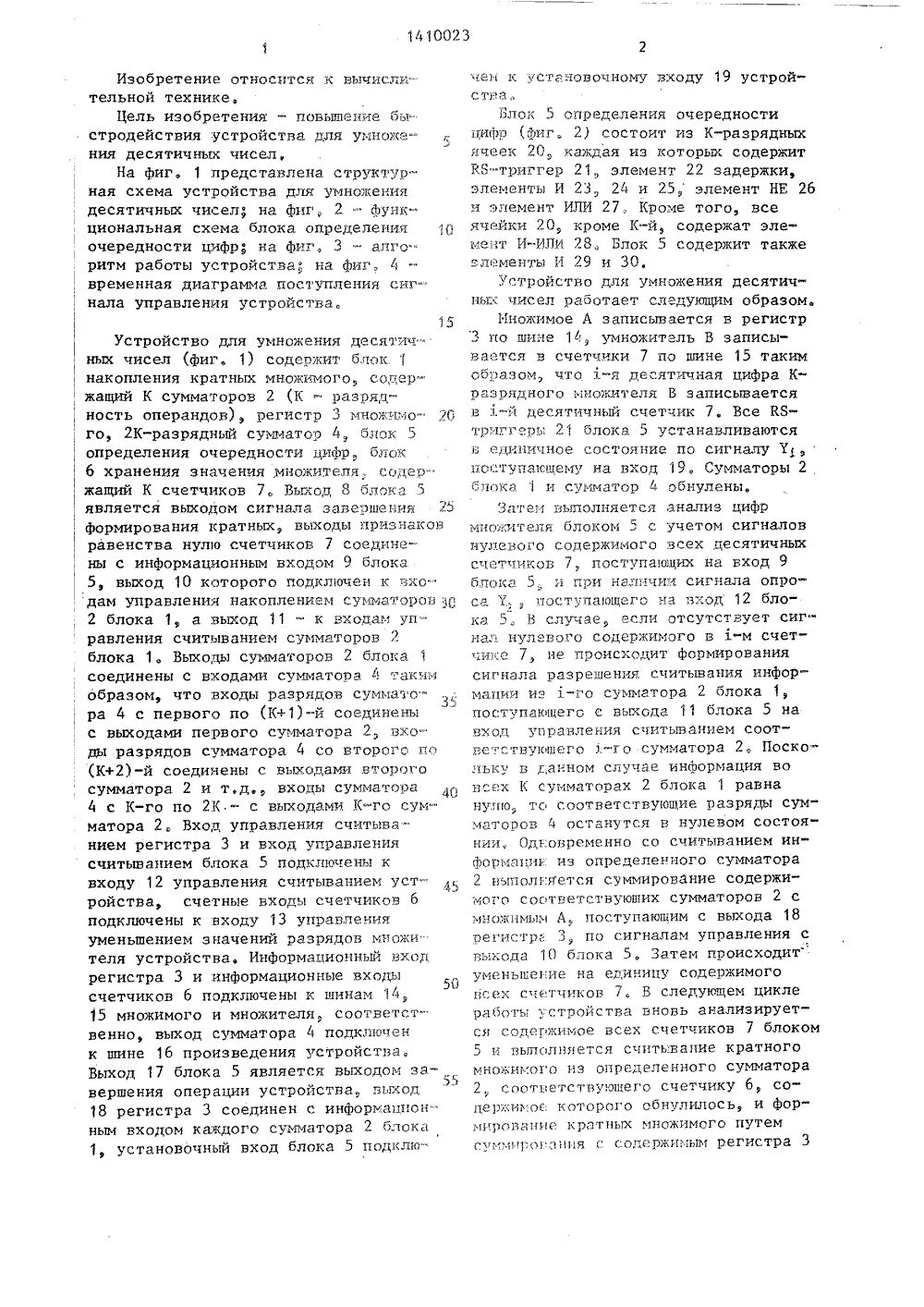

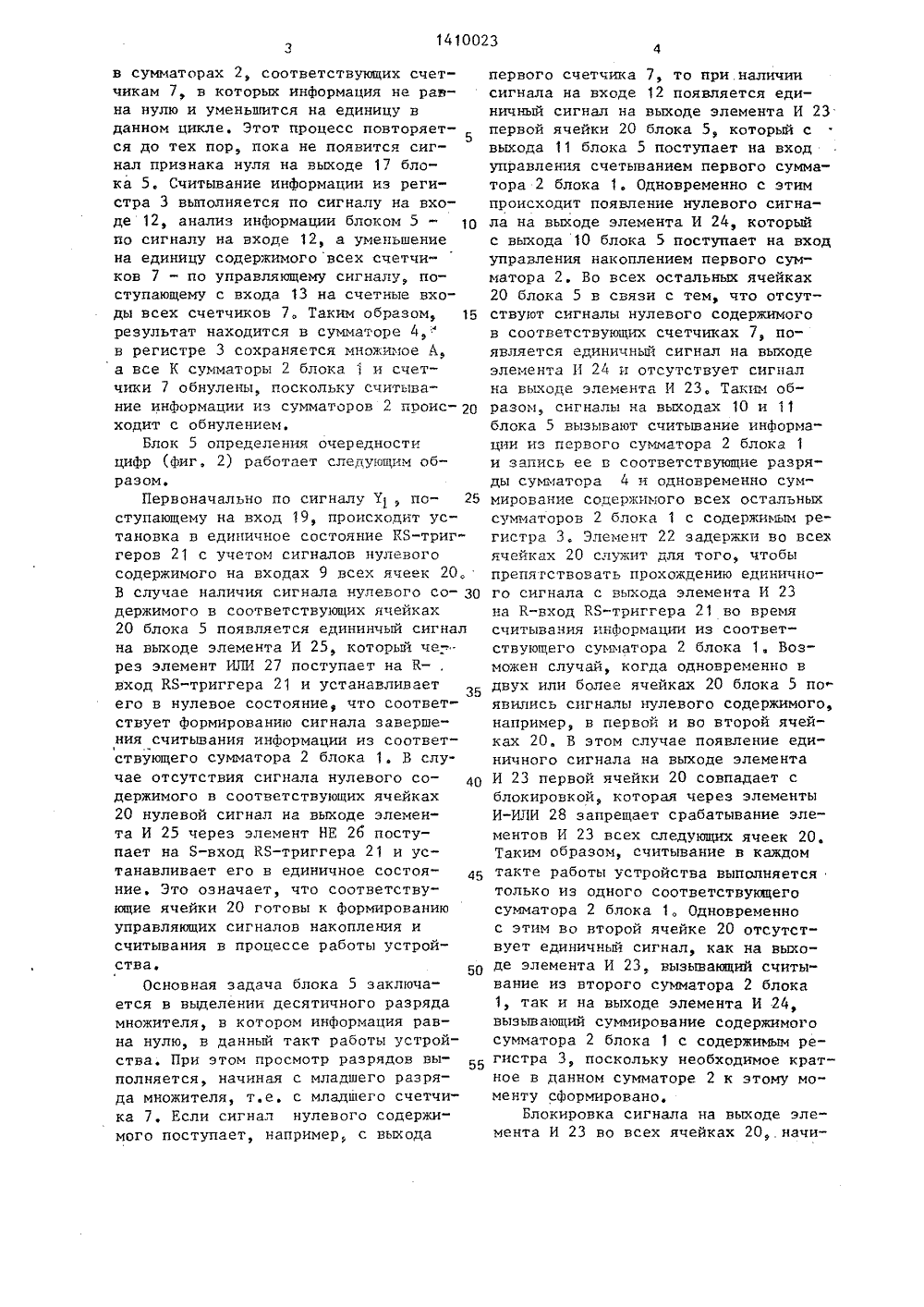

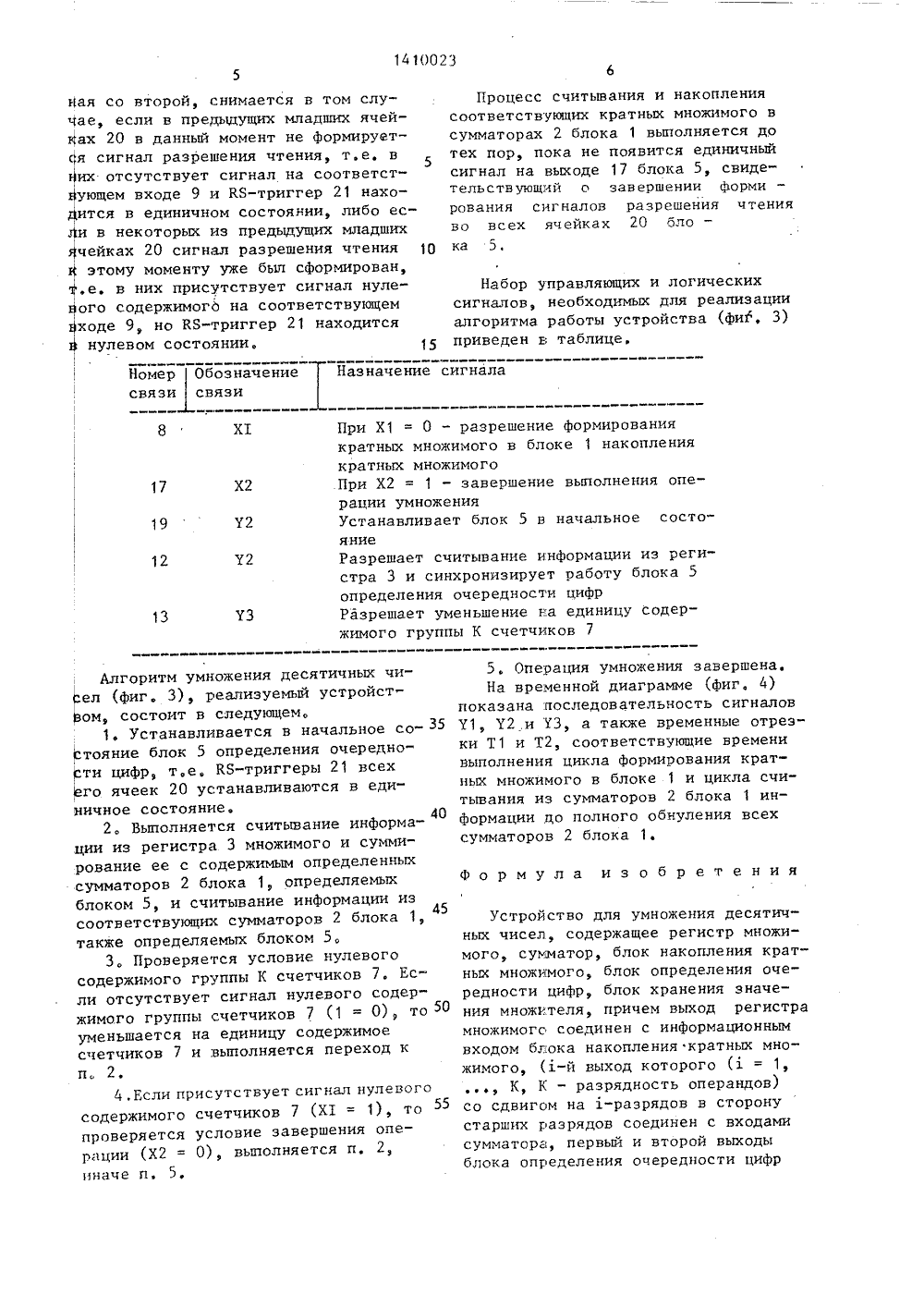

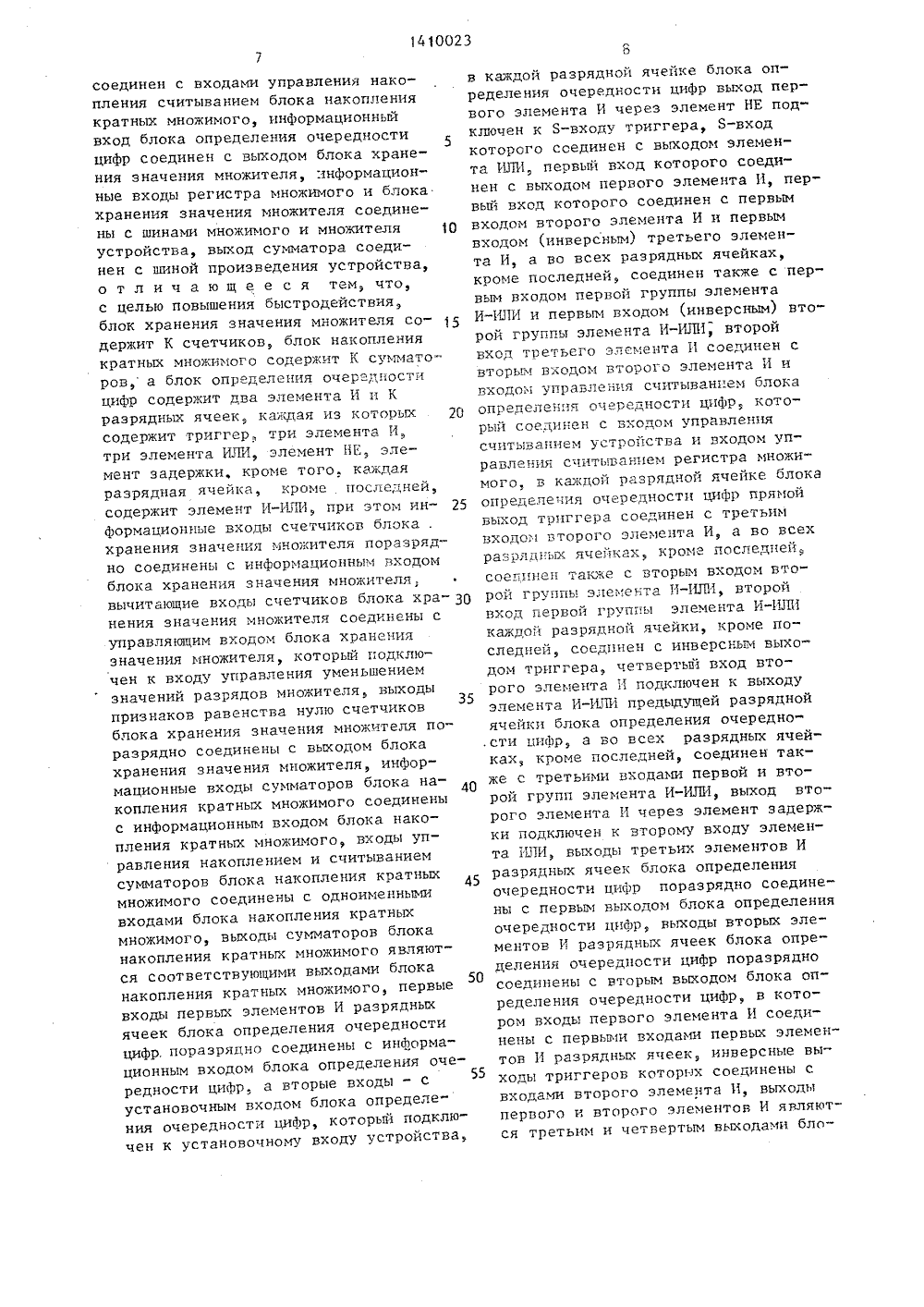

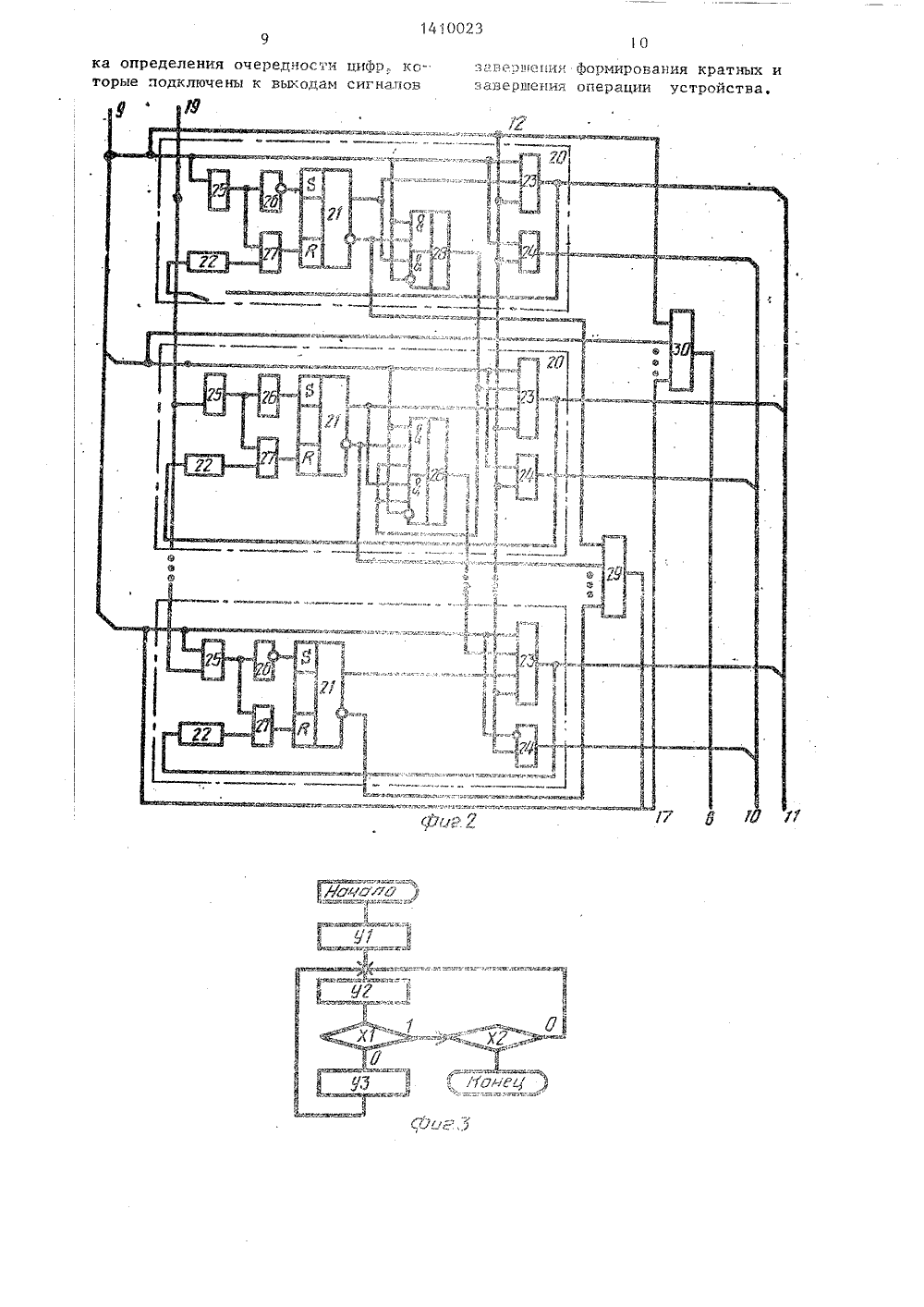

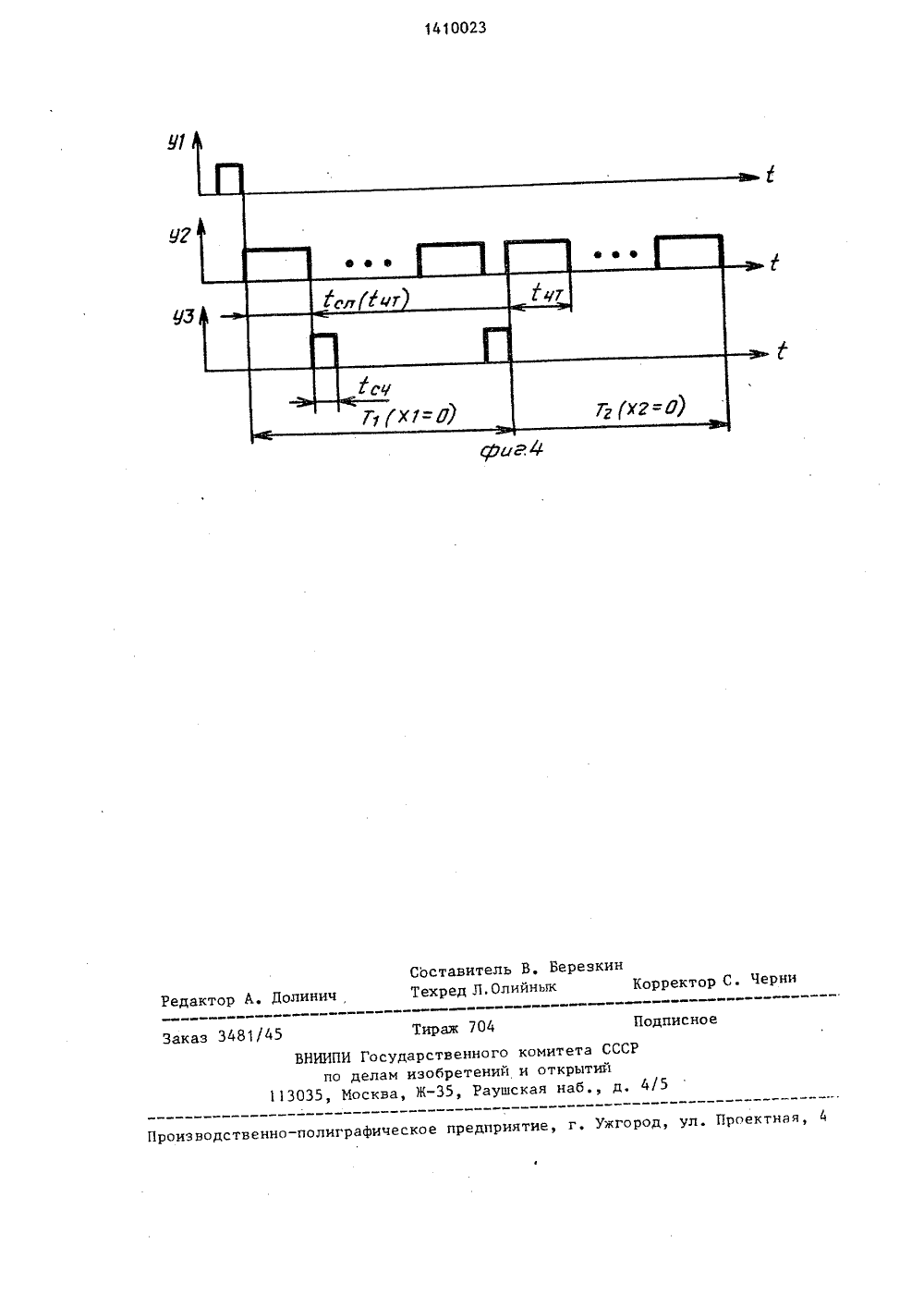

(53) 6 рошвили,реализавычитания ектронных Приборо- -65.СССР 1974. В.П, и др,умножения ел на опто Изв. вузов 1976, с. видетельст С 06 Р 7/5по" рованияаторах 2 множимого,ных путем ния и счиатных мноеделения ОЖЕНИЯ ДЕСЯОСУДАРСТ 8 ЕННЫЙ НОМИТЕТ СССР О ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТ(57) Изобретение относится к областвычислительной техники, Целью изобретения является повышение быстродействия устройства для умножения дсятичных чисел, Использование в устройстве К сумматоров 2 в блоке 1 накопления кратных множимого, 2 К-разрядного сумматора 4, блока 5 определения очередности циФр и К. счетчикав блоке 6 контроля значения множителя позволяет считывать в сумматорсоответствующие кратные множимогобез их сдвига по мере Формиследних в определенных суммблока 1 накопления кратныхПроцессом Формирования кратих параллельного накапливатыванием соответствунзцих кржимого управляет блок 5. опрочередности циФр, 4 ил, 1 табл,Изобретение относится к вычислительной технике,Цель изобретения - повышение быстродействия устройства для умноже=ния десятичных чисел,На фиг, 1 представлена структ-рная схема устройства для умножениядесятичных чисел; на Фиг, 2 - функ=циональная схема блока определенияочередности цифр; на фиг, 3 - алгс"ритм работы устройства;, на Фиг,временная диаграмма поступления сиг=.нала управления устройства. Устройство для умножения десятич-:ных чисел (Фиг, 1) содержит блокнакопления кратных множимого, ссцер=жащий К сумматоров 2 (К - разрядность операндов), регистр 3 множимого, 2 К-разрядный сумматор 4, блок 5определения очередности цчфр, блок6 хранения значения, множителя, содер-.жащий К счетчиков 7, Вьгхсд 8 блока 5является выходом сигнала завершения ,5формирования кратных, выходы признаковравенства нулю счетчиков 7 соединены с информационным входом 9 блока5, выход 10 которого подключен к входам управления накоплением сумматоров:.,02 блока 1, а:выход 11 - к вхспам уп-"равления считыванием сумматоров 2блока 1. Выходы сумматоров 2 блокасоединены с входами сумматора 4 такимобразом, что:входы разрядов суммато=ра 4 с первого по (К+1)-и соединеньс выходами первого сумматора 2, входы разрядов сумматора 4 со второго пс(К+2)-й соединены с выходами второгосумматора 2 и т,д., входы сумматора4 с К-го по 2 К - с выходами К-гс сумматора 2. Вход управления считыванием регистра 3 и вход управлениясчитыванием блока 5 подключены квходу 12 управления считыванием устчройства, счетные входы счетчиков 6подключены к входу 13 управленияуменьшением значений разрядов множителя устройства. ИнФормационный входрегистра 3 и информационные входы50счетчиков 6 подключены к шинам 14,15 множимого и множителя,венно, выход сумматора 4 подключенк шине 16 произведения устройстваВыход 17 блока 5 является выходом за 55вершения операции устройства, выход18 регистра 3 соединен с информапнон-.ным входом каждого сумматора 2 блока1, установочный вход блока 5 псдключен к установочному входу 19 устройствадБлок 5 определения очередностицифр (Фиг. 2) состоит из К-разрядныхячеек 20. каждая из которых содержитКЯ-.триггер 21 элемент 22 задержки,элементы И 23 24 и 25, элемент НЕ 26и элемент ИЛИ 27., Кроме того, всеячейки 20, кроме К-й, содержат элеме:,т И-.ИЛИ 28, Блок 5 содержит такжеэлементы И 29 и 30,Устройство цля умножения десятичных чисел раоотает следующим образом.11 нсжимсе А записывается в регистр3 по шине 14, умножитель В записывается в счетчики 7 пс шине 15 такимсб;,азом, что 1.-я десятичная цифра Кразрядного множителя В записываетсяв:1 й десятичный счетчик 7. Все КБтригг .ры 21 блока 5 устанавливаютсяв единичное состояние пс сигналу 1 рпоступающему на вход 19. Сумматоры 2б.выса 1 и сумматор 4 сбнулены,Затем выполняется анализ цифрмножителя блоком 5 с учетом сигналовнулевого содержимого всех,десятичныхсчетчиков 7, поступающих на вход 9блока 5 и при наличии сигнала опроса Т, - поступаюшего на вход 12 блока 5., 8 случае если отсутствует сигна.: нулевсгс содержимого в -м счетчике 7, не происходит Формированиясигнала разрешения считывания информации из 1-го сумматора 2 блока 1,поступающего с выхода 11 блока 5 навход управления считыванием соответствующего .-гс сумматора 2, Поско"льку в,г,анном случае информация вов=ех К сумматорах 2 блока 1 равнанулю, тс соответствующие разряды сумматоров 4 останутся в нулевом состоянии Одновременно со считыванием инФсрмяци из определенного сумматора2 выпольяется суммирование содержимого ссстветствуюших сумматоров 2 смнсжпмым А., поступаюшим с выхода 18регистр; 3 по сигналам управления свыходя 10 блока 5, Зятем происходитуменьшение на единицу содержимоговсех счетчиков 7. Б следующем циклеработы устройства вновь анализируется содержимое всех счетчиков 7 блоком5 и выполняется считьвание кратногомножимсгс из определенногс сумматора2 состветствуюшегс счетчику 6, соцержю се которого сбнулилось, и формирование кратных мнсжимсгс путемсук.1 и 1;с 1 явня с содержимым регистра 3в сумматорах 2, соответствующих счетчикам 7, в которых информация не равна нулю и уменьшится на единицу вданном цикле, Этот процесс повторяется до тех пор, пока не появится сигнал признака нуля на выходе 17 блока 5, Считывание информации из регистра 3 выполняется по сигналу на входе 12, анализ информации блоком 5 - 10но сигналу на входе 12, а уменьшениена единицу содержимого всех счетчиков 7 - по управляющему сигналу, поступающему с входа 13 на счетные входы всех счетчиков 7, Таким образом, 15результат находится в сумматоре 4,"в регистре 3 сохраняется множимое А,а все К сумматоры 2 блока 1 и счетчики 7 обнулены, поскольку считывание информации из сумматоров 2 происходит с обнулением.Блок 5 определения очередностицифр (фиг. 2) работает следующим образом,Первоначально по сигналу У, поступающему на вход 19, происхоцит установка в единичное состояние КБ-триггеров 21 с учетом сигналов нулевогосодержимого на входах 9 всех ячеек 20,В случае наличия сигнала нулевого со- Зодержимого в соответствующих ячейках20 блока 5 появляется едининчый сигнална выходе элемента И 25, который че. - .рез элемент ИЛИ 27 поступает на К- .вход КБ-триггера 21 и устанавливаетего в нулевое состояние, что соответствует формированию сигнала завершения считывания информации из соответствующего сумматора 2 блока 1, В случае отсутствия сигнала нулевого со Одержимого в соответствующих ячейках20 нулевой сигнал на выходе элемента И 25 через элемент НЕ 2 б поступает на Б-вход КБ-триггера 2 1 и устанавливает его в единичное состояние. Это означает, что соответствующие ячейки 20 готовы к формированиюуправляющих сигналов накопления исчитывания в процессе работы устройства.50Основная задача блока 5 заключается в выделении десятичного разрядамножителя, в котором информация равна нулю, в данный такт работы устройства, При этом просмотр разрядов выполняется, начиная с младшего разряда множителя, т.е. с младшего счетчика 7, Если сигнал нулевого содержимого поступает, например, с выхода первого счетчика 7, то нри.наличии сигнала на входе 12 появляется единичный сигнал на выходе элемента И 23 первой ячейки 20 блока 5, который с выхода 11 блока 5 поступает на вход управления счетыванием первого сумматора 2 блока 1. Одновременно с этим происходит появление нулевого сигнала на выходе элемента И 24, который с выхода 10 блока 5 поступает на вход управления накоплением первого сумматора 2. Во всех остальных ячейках 20 блока 5 в связи с тем, что отсутствуют сигналы нулевого содержимого в соответствующих счетчиках 7, появляется единичный сигнал на выходе элемента И 24 и отсутствует сигнал на выходе элемента И 23, Таким образом, сигналы на выходах 10 и 11 блока 5 вызывают считьвание информации из первого сумматора 2 блока и запись ее в соответствующие разряды сумматора 4 и одновременно суммирование содержимого всех остальных сумматоров 2 блока 1 с содержиьм регистра 3, Элемент 22 задержки во всех ячейках 20 служит для того, чтобы препятствовать прохождению единичного сигнала с выхода элемента И 23 на К-вход КБ-триггера 21 во время считывания информации из соответствующего сумматора 2 блока 1. Возможен случай, когда одновременно в двух или более ячейках 20 блока 5 по явились сигналы нулевого содержимого, например, в первой и во второй ячейках 20, В этом случае появление единичного сигнала на выходе элемента И 23 первой ячейки 20 совпадает с блокировкой, которая через элементы И-ИЛИ 28 запрещает срабатывание элементов И 23 всех следующих ячеек 20. Таким образом, считьвание в каждом такте работы устройства выполняется только из одного соответствующего сумматора 2 блока 1, Одновременно с этим во второй ячейке 20 отсутствует единичный сигнал, как на выходе элемента И 23, вызывающий считывание из второго сумматора 2 блока 1, так и на выходе элемента И 24, вызьвающий суммирование содержимого сумматора 2 блока 1 с содержимым ре" гистра 3, поскольку необходимое кратное в данном сумматоре 2 к этому моменту сформировано.Блокировка сигнала на выходе элемента И 23 во всех ячейках 20,. начи1410023 сигнала При Х 1 = 0 - разрешение формирования кратных множимого в блоке 1 накопления кратных множимогоПри Х 2 = 1 - завершение выполнения операции умноженияУстанавливает блок 5 в начальное состоХ 1 Х 2 У 2 19 яниеРазрешает считывание информации из регистра 3 и синхронизирует работу блока 5 определения очередности цифрРазрешает уменьшение на единицу содержимого группы К счетчиков 7 УЗ 13 йемая со второй, снимается в том случае, если в предыдущих младших ячейках 20 в данный момент не формируется сигнал разрешения чтения, т,е. в их отсутствует сигнал на соответствующем входе 9 л КБ-триггер 21 нахоится в единичном состоянии, либо ести в некоторых лз предыдущих младших ячейках 20 сигнал разрешения чтения 10этому моменту уже был сформирован, .е. в них присутствует сигнал нулеого содержимого на соответствующем ходе 9, но КБ-триггер 21 находитсянулевом состоянии,15 Номер Обозначение Назначениесвязи связи Алгоритм умножения десятичных чисел (фиг, 3), реализуемый устройстом, состоит в следующем,1. Устанавливается в начальное состояние блок 5 определения очередности цифр, т.е. КБ-триггеры 21 всехго ячеек 20 устанавливаются в единичное состояние.2. Выполняется считывание информации из регистра 3 множимого и суммирование ее с содержимым определенныхсумматоров 2 блока 1, определяемыхблоком 5 и считывание информации изФ45соответствующих сумматоров 2 блока 1,также определяемых блоком 5.3. Проверяется условие нулевогосодержимого группы К счетчиков 7, Если отсутствует сигнал нулевого содержимого группы счетчиков 7 (1 = О), то50меньшается на единицу содержимоесчетчиков 7 и выполняется переход кп. 2,4.Если присутствует сигнал нулевогосодержимого счетчиков 7 (Х 1 = 1), то55проверяется условие завершения операции (Х 2 = О), выполняется и, 2,иначе п. 5,Процесс считывания и накопления соответствующих кратных множимого в сумматорах 2 блока 1 выполняется до тех пор, пока не появится единичный сигнал на выходе 17 блока 5, свидетельствующлй о завершении форми рования сигналов разрешения чтения во всех ячейках 20 блока 5 Набор управляющих и логическихсигналов, необходимых для реализацииалгоритма работы устройства (фиг, 3)приведен в таблице. 5. Операция умножения завершена.На временной диаграмме (Фиг. 4) показана последовательность сигналов У 1, У 2 и УЗ, а также временные отрезки Т 1 и Т 2, соответствующие времени выполнения цикла Формирования кратных множимого в блоке 1 и цикла считывания из сумматоров 2 блока 1 инФормации цо полного обнуления всех сумматоров 2 блока 1. Формула изобретения Устройство для умножения десятичных чисел, содержащее регистр множимого, сумматор, блок накопления кратных множимого, блок определения очередности цифр, блок хранения значения множителя, причем выход регистра множимогс соединен с информационным входом блока накопления кратных множимого, (-й выход которого ( = 1,К, К - разрядность операндов) со сдвигом на -разрядов в сторону старших разрядов соединен с входами сумматора, первык и второй выходы блока определения очередности цифрсоединен с входами управления накопления считыванием блока накопления кратных мнажимого, информационный вход блока определения очередности5 цифр соединен с выходом блока хранения значения множителя, информационные входы регистра множимого и блока хранения значения множителя соединены с шинами мнохсимого и множителя 10 устройства, выход сумматора соединен с шиной произведения устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, блок хранения значения множителя содержит К счетчиков, блок накопления кратных множимога содержит К суммато- ров, а блок определения очередности цифр содержит два элемента И и К разрядных ячеек, каждая из которых 20 содержит триггер., три элемента И, три элемента ИЛИ, элемент НЕ, элемент задержки, кроме того. каждая разрядная ячейка, кроме последней, содержит элемент И-ИЛИ, при этом ин формационные входы счетчиков блока . хранения значения множителя поразрядно соединены с информационным входом блока хранения значения множителя вычитающие входы счетчиков блока хра- З 0 нения значения множителя соединены с управляющим входом блока хранения значения множителя, который подключен к входу управления уменьшением значений разрядов множителя, выходы признаков равенства нулю счетчиков35 блока хранения значения множителя поразрядно соединены с выходом блока хранения значения множителя, информационные входы сумматоров блока на копления кратных множимого соединены с информационным входом блока накопления кратных множимого, входы управления накоплением и считыванием сумматоров блока накопления кратных множимого соединены с одноименными входами блока накопления кратных множимого, выходы сумматоров блока накопления кратных множимого являются соответствующими выходами блока накопления кратных множимого, первые50 входы первых элементов И разрядных ячеек блока определения очередности цифр, поразрядно соединены с информационным входом блока определения очередности цифр, а вторые входы - с55 установочным входом блока определе" ния очередности цифр, который подключен к установочному входу устройства,в каждой разрядкой ячейке блока определения очередности цифр выход первого элемента И через элемент НЕ подключен к Б-входу триггера, Я-вход которого соединен с выходом элемента ИЛИ, первый вход которого соединен с выходом первого элемента И, первый вход которого соединен с первым входом второго элемента И и первым входом (инверсным) третьего элемента И, а во всех разрядных ячейках, кроме последней, соединен также с первым входом первой группы элемента И-ИЛИ и первым входом (инверсным) второй группы элемента И-ИЛИ, второй вход третьего элемента И соединен с вторым входом второго элемента И и входам управления считыванием блока определения очередности цифр, который соединен с входом управления считыванием устройства и входом управления считыганцем регистра множимого, в каждой разрядной ячейке блока определения очередности цифр прямой выход триггера соединен с третьим входам второго элемента И, а во всех разрядных ячейках кроме последнейсоепцнен также с вторым входом второй группы элемента И-ИЛИ, втароц вход первой группы элемента И-ИЛИ каждой разрядной ячейки, кроме последней, соединен с инверсным выходом триггера, четвертый вход второго элемента И подключен к выходу элемента И-ИЛИ предыдущей разрядной ячейки блока определения очередно,сти цифр, а ва всех разрядных ячейках, кроме последней, соединен также с третьими входами первой и второй групп элемента И-ИЛИ, выход второго элемента И через элемент задержки подключен к второму входу элемента ИЛИ, выходы третьих элементов И разрядных ячеек блока определения очередности цифр поразрядно соединены с первым выходом блока определения очередности цифр, выходы вторых элементов И разрядных ячеек блока определения очередности цифр поразрядно соединены с вторым выходом блока определения очередности цифр, в катором входы первого элемента И соединены с первыми входами первых элементов И разрядных ячеек, инверсные выходы триггеров которых соединены с входами второго элемента И, выходы первого и второго элементов И являются третьим и четвертым вьходами бло 1 А 0023ка определения очередности цифр. которые подключены к высо,цам сигныов:зазрвепн Формирования кратнъос ивавершеиия операции устройства,1410023 У 7 оставитель В, Березкинехред Л Олийнык ректор С, Чер Долинич дакт аз 3481/45 одписн та ССС роизводственно-полиграфическое предприятие, г. Ужгород, ул. Проектная,ВНИИПИ Государственного ко по делам изобретений и113035, Москва, Ж, Раушска крытиинаб, д, 4/5

СмотретьЗаявка

4126359, 24.06.1986

ГРУЗИНСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. В. И. ЛЕНИНА

КОЖЕМЯКО ВЛАДИМИР ПРОКОФЬЕВИЧ, НАТРОШВИЛИ ОТАР ГЕОРГИЕВИЧ, ЧХАИДЗЕ НИКОЛАЙ ЗАВАРОВИЧ, МАРТЫНЮК ТАТЬЯНА БОРИСОВНА, ГИГАУРИ ВЛАДИМИР ГЕНРИЕВИЧ

МПК / Метки

МПК: G06F 7/52

Метки: десятичных, умножения, чисел

Опубликовано: 15.07.1988

Код ссылки

<a href="https://patents.su/7-1410023-ustrojjstvo-dlya-umnozheniya-desyatichnykh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для умножения десятичных чисел</a>

Предыдущий патент: Одноразрядный сумматор

Следующий патент: Устройство для умножения

Случайный патент: Солнцезащитное ограждение