Устройство для умножения -разрядных чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

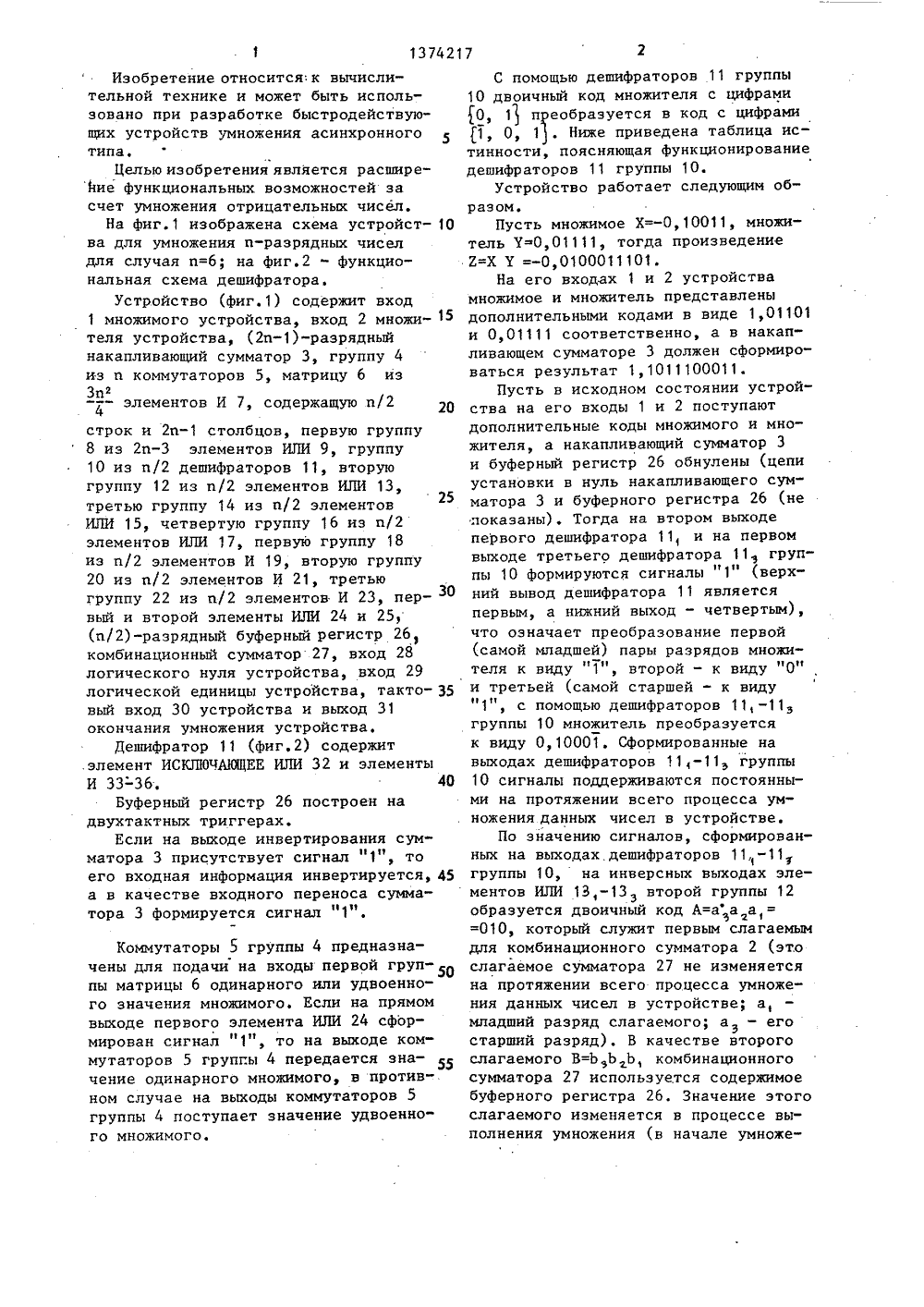

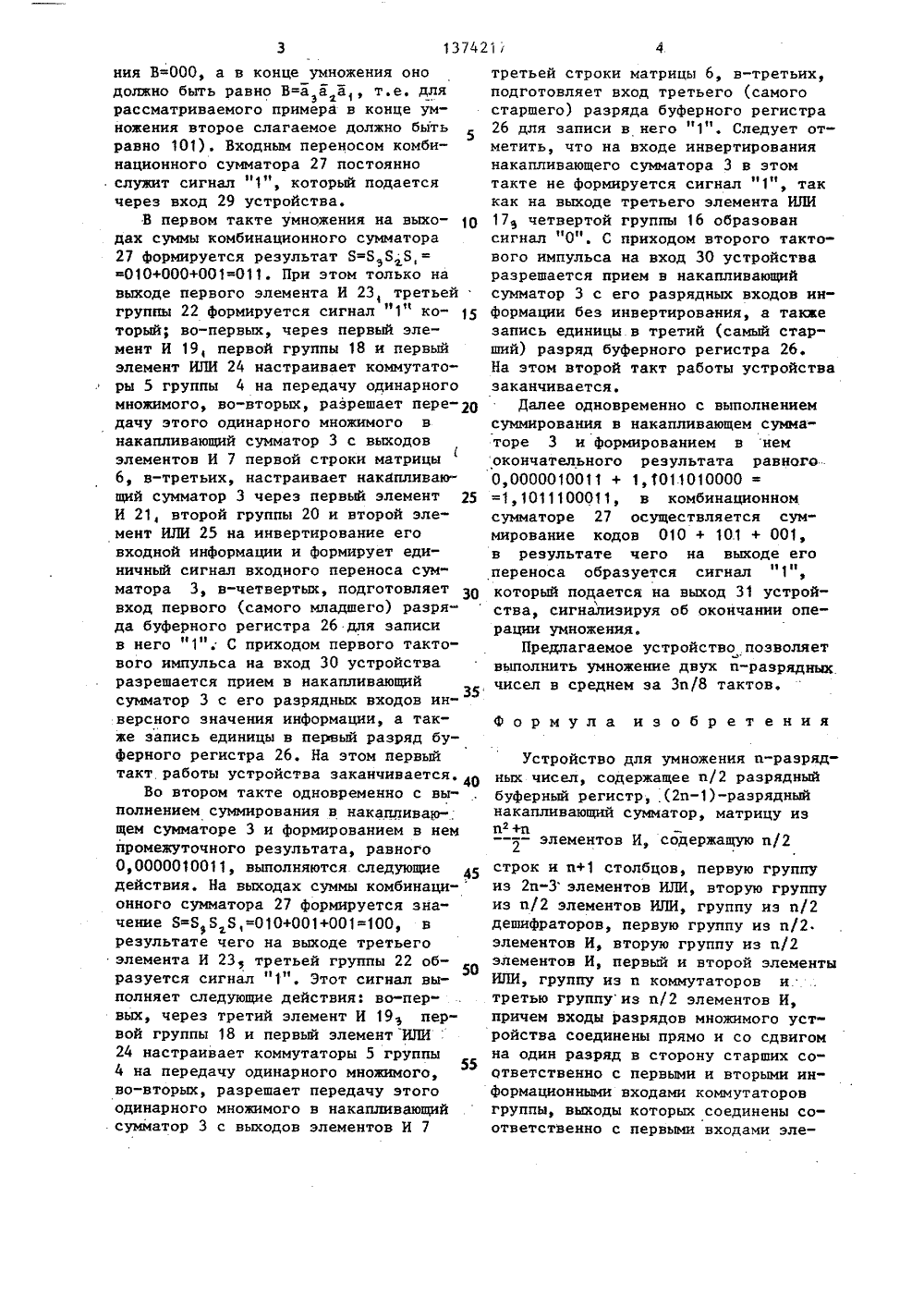

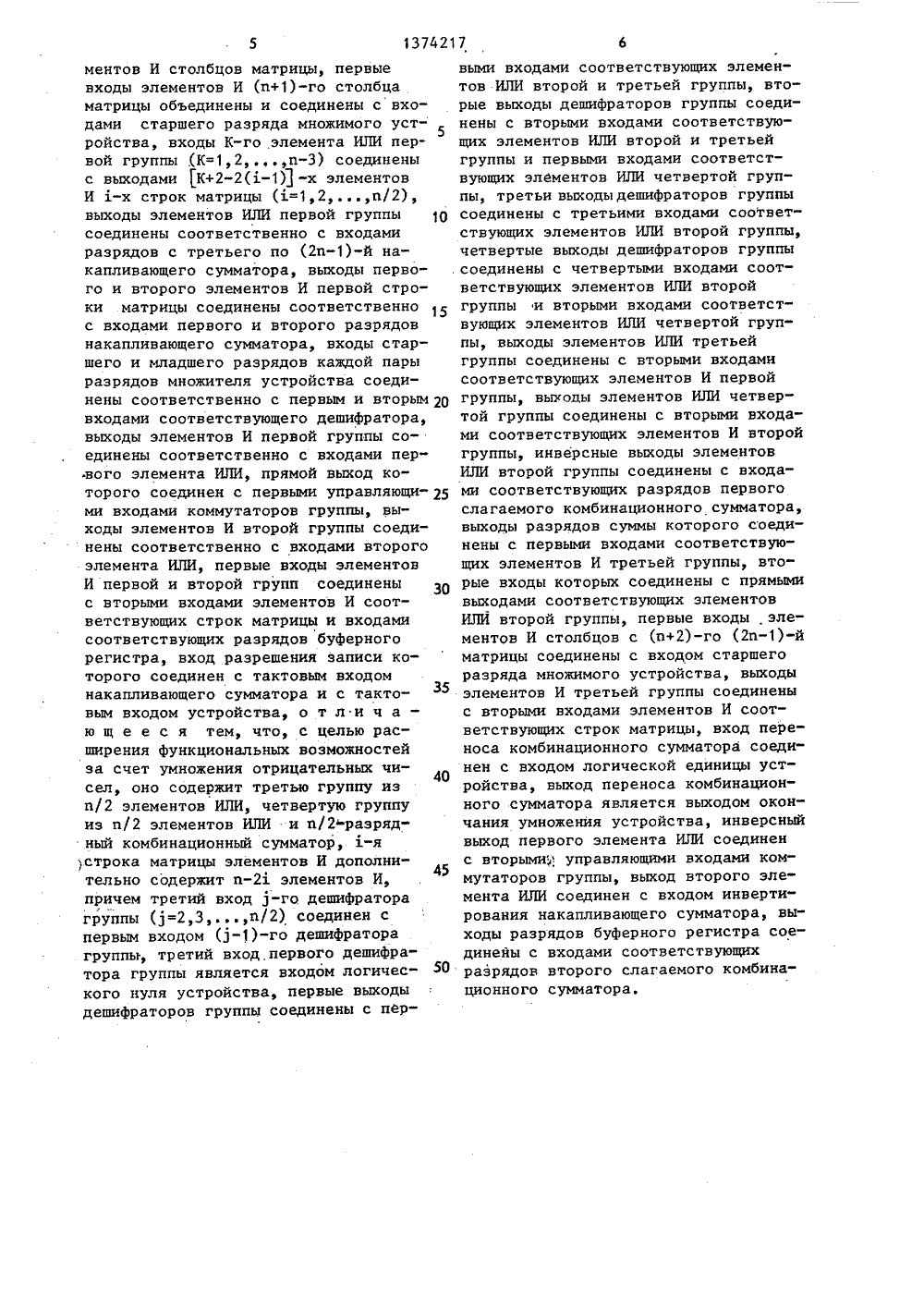

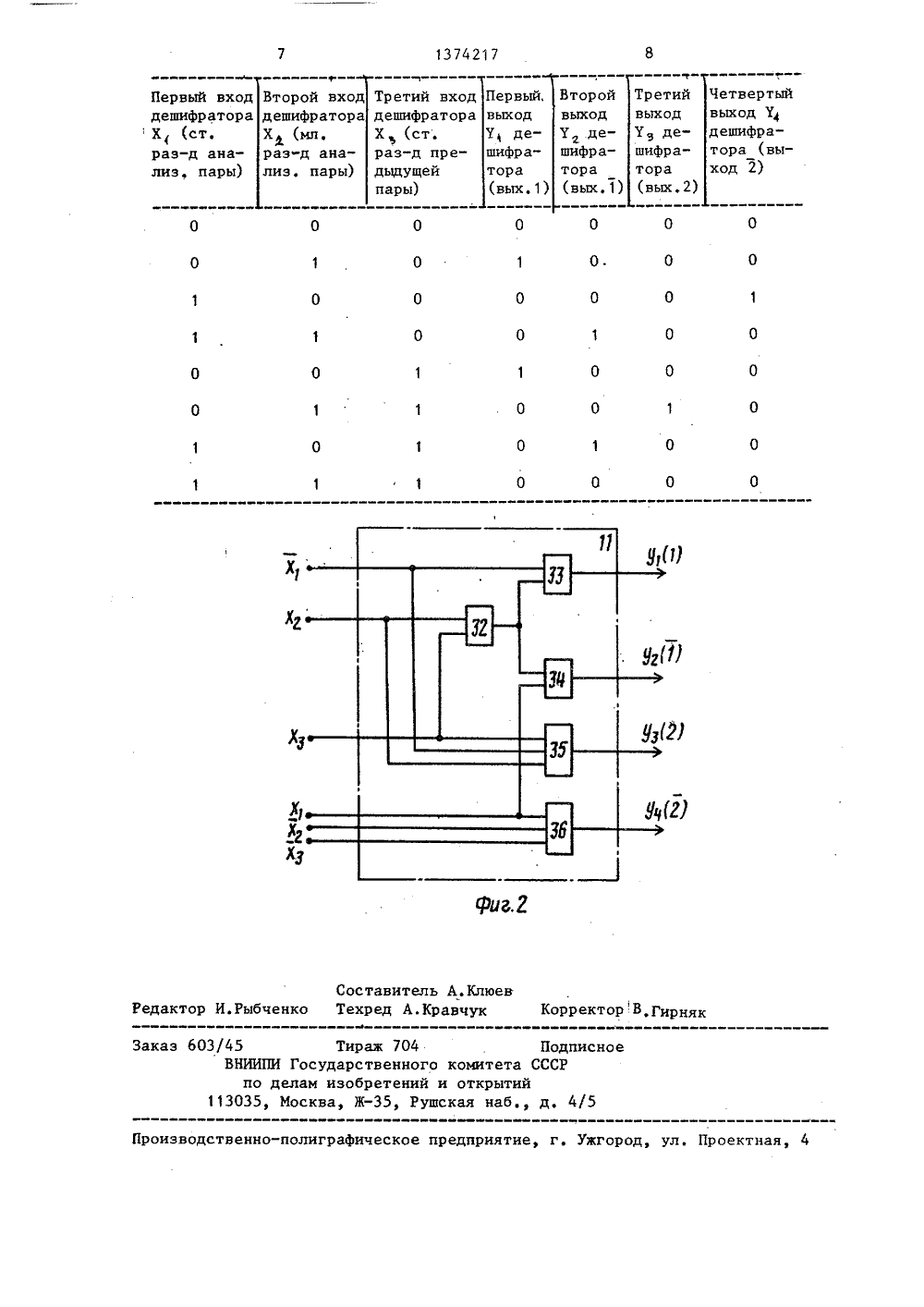

СОЮЗ СОВЕТСКИЮСОЦИАЛИСТИЧЕСКИРЕСПУБЛИК 191 (И) 94 С 06 ГОС ПОД В(.Я(Яйлой ОПИСАНИЕ ИЗОБРЕТЕН ВТОРСКОМУ С ТЕПЬСТВУ(21) 4100190/24 (22) 04.0886 (46) 1502,88, (71) Минский р Бюл. Уадиотех ческий инстиВ 11 (54) РЯДНЫ (57) тель зова щнх содержиИЛИ и2 ил,ваяв Ю АРСТВЕННЫЙ КОМИТЕТ СССРЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ(56) Авторское свидетельство СССУ 1193667, кл, С 06 Р 7/52, 1982Авторское свидетельство СССР 1153, кл. С 06 Р 7/52, 1982. УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ Б-РАЗ- Х ЧИСЕЛИзобретение относится к вычисли ой технике и может быть иснольо при разработке быстродействую стройств умножения асинхронного1 типа, Целью изобретения является расширение Функцональных возможностей за счет умножения отрицательных чисел. Поставленная цель достигается тем, что устройство для умножения п-разрядных чисел, содержащее накапливающий сумматор3, группу 4 коммутаторов 5, матрицу 6 элементов И 7, группу 8 элементов ИЛИ 9, группу 10 дешифраторов 11, группу 12 элементов ИЛИ 13, группу 18 элементов И 19, группу 20 элементов И 21, группу 22 элементов И 23, элементы ИЛИ 24, 25 и буферный регистр 26, дополнительнот группы 14 и 16 элементовкомбинационный сумматор 27.Изобретение относится к вычислительной технике и может быть использовано при разработке быстродействующих устройств умножения асинхронного типа.Целью изобретения является расширение функциональных возможностей за счет умножения отрицательных чисел.На фиг.1 изображена схема устройст ва для умножения и-разрядных чисел для случая п=б; на фиг.2 - функциональная схема дешифратора.Устройство (фиг.1) содержит вход 1 множимого устройства, вход 2 множи теля устройства, (2 п)-разрядный накапливающий сумматор 3, группу 4 из и коммутаторов 5, матрицу б из Зп- - элементов И 7, содержащую и/2 20 строк и 2 пстолбцов, первую группу 8 из 2 пэлементов ИЛИ 9, группу 10 из и/2 дешифраторов 11, вторую группу 12 из и/2 элементов ИЛИ 13, третью группу 14 из и/2 элементов25 ИЛИ 15, четвертую группу 16 из и/2 элементов ИЛИ 17, первую группу 18 из и/2 элементов И 19, вторую группу 20 из и/2 элементов И 21, третью группу 22 из и/2 элементов И 23, первый и второй элементы ИЛИ 24 и 25, (и/2)-разрядный буферный регистр 26 комбинационный сумматор 27, вход 28 логического нуля устройства, вход 29 логической единицы устройства, такто вый вход 30 устройства и выход 31 окончания умножения устройства.Дешифратор 11 (фиг.2) содержит .элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 32 и элементы И 33-36, 40Буферный регистр 26 построен на двухтактных триггерах.Если на выходе инвертирования сумматора 3 присутствует сигнал "1", то его входная информация инвертируется, 45 а в качестве входного переноса сумматора 3 формируется сигнал "1". Коммутаторы 5 группы 4 предназначены для подачи на входы первой груп пы матрицы 6 одинарного или удвоенного значения множимого. Если на прямом выходе первого элемента ИЛИ 24 сформирован сигнал "1", то на выходе коммутаторов 5 групгы 4 передается значение одинарного множимого, в противном случае на выходы коммутаторов 5 группы 4 поступает значение удвоенного множимого,С помощью дешифраторов 11 группы10 двоичный код множителя с цифрами0, 1 преобразуется в код с цифрами1, О, 1, Ниже приведена таблица истинности, поясняющая функционированиедешифраторов 11 группы 10.Устройство работает следующим образомм,Пусть множимое Х=-0,10011, множитель У 0,01111, тогда произведение2=Х У =-0,0100011101.На его входах 1 и 2 устройствамножимое и множитель представленыдополнительными кодами в виде 1,01101и 0,01111 соответственно, а в накапливающем сумматоре 3 должен сформироваться результат 1,1011100011.Пусть в исходном состоянии устройства на его входы 1 и 2 поступаютдополнительные коды множимого и множителя, а накапливающий сумматор 3и буферный регистр 26 обнулены (цепиустановки в нуль накапливающего сумматора 3 и буферного регистра 26 (непоказаны), Тогда на втором выходепервого дешифратора 11, и на первомвыходе третьего дешифратора 11 з группы 10 Формируются сигналы "1" (верхний вывод дешифратора 11 являетсяпервым, а нижний выход - четвертым),что означает преобразование первой(самой младшей) пары разрядов множителя к виду 1 , второй - к виду "0"и третьей (самой старшей - к виду"1", с помощью дешифраторов 11, -11группы 1 О множитель преобразуетсяк виду 0,10001. Сформированные навыходах дешифраторов 11,-11 группы10 сигналы поддерживаются постоянными на протяжении всего процесса умножения данных чисел в устройстве.По зйачению сигналов, сформированных на выходах.дешифраторов 11-11группы 10, на инверсных выходах элементов ИЛИ 13,-13 второй группы 12образуется двоичный код А=а а а,==010, который служит первым слагаемымдля комбинационного сумматора 2 (этослагаемое сумматора 27 не изменяетсяна протяжении всего процесса умножения данных чисел в устройстве; а,младший разряд слагаемого; а - егостарший разряд). В качестве второгослагаемого В=ЬЬЬ, комбинационногосумматора 27 используется содержимоебуферного регистра 26. Значение этогослагаемого изменяется в процессе выполнения умножения (в начале умноже 137421ния В=000, а в конце умножения оно должно быть равно В=а а а т.е. для рассматриваемого примера в конце умножения второе слагаемое должно быть равно 101). Входным переносом комбинационного сумматора 27 постоянно служит сигнал "1", который подается через вход 29 устройства.В первом такте умножения на выходах суммы комбинационного сумматора 27 формируется результат 8=8 Б 8,= 010+000+001=011. При этом только на выходе первого элемента И 23, третьей группы 22 формируется сигнал "1" который; во-первых, через первый элемент И 19, первой группы 18 и первый элемент ИЛИ 24 настраивает коммутаторы 5 группы 4 на передачу одинарного множимого, во-вторых, разрешает передачу этого одинарного множимого в накапливающий сумматор 3 с выходов элементов И 7 первой строки матрицы 6, в-третьих, настраивает накапливающий сумматор 3 через первый элемент 25 И 21, второй группы 20 и второй элемент ИЛИ 25 на инвертирование его входной информации и формирует единичный сигнал входного переноса сум" матора 3, в-четвертых, подготовляет вход первого (самого младшего) разряда буферного регистра 26 для записи в него "1"; С приходом первого тактового импульса на вход 30 устройства разрешается прием в накапливающий сумматор 3 с его разрядных входов инверсного значения информации, а также запись единицы в первый разряд буферного регистра 26, На этом первый такт работы устройства заканчивается, 40Во втором такте одновременно с выполнением суммирования в накапливаю-. щем сумматоре 3 и формированием в нем промежуточного результата, равного 0,0000010011, выполняются следующие действия. На выходах суммы комбинаци-онного сумматора 27 формируется значение 8=8 Б 8,=010+001+001=100, в результате чего на выходе третьего элемента И 23 третьей группы 22 образуется сигнал " 1". Этот сигнал выполняет следующие действия: во-первых, через третий элемент И 19 первой группы 18 и первый элемент ИЛИ 24 настраивает коммутаторы 5 группы 4 на передачу одинарного множимого, во-вторых, разрешает передачу этого одинарного множимого в накапливающий сумматор 3 с выходов элементов И 7 третьей строки матрицы 6, в-третьих, подготовляет вход третьего (самого старшего) разряда буферного регистра 26 для записи в него "1", Следует отметить, что на входе инвертирования накапливающего сумматора 3 в этом такте не формируется сигнал "1", так как на выходе третьего элемента ИЛИ 17 з четвертой группы 16 образован сигнал "0". С приходом второго тактового импульса на вход 30 устройства разрешается прием в накапливающий сумматор 3 с его разрядных входов инФормации без инвертирования, а также запись единицы в третий (самый старший) разряд буферного регистра 26. На этом второй такт работы устройства заканчивается.Далее одновременно с выполнением суммирования в накапливающем сумматоре 3 и формированием в нем окончательного результата равного,0000010011 + 1, 1011010000 = =1,1011100011, в комбинационном сумматоре 27 осуществляется суммирование кодов 010 + 101 + 001, в результате чего на выходе его переноса образуется сигнал "1", который подается на выход 31 устройства, сигнализируя об окончании операции умножения.Предлагаемое устройство позволяет выполнить умножение двух и-разрядных чисел в среднем за Зи/8 тактов.формула изобретенияУстройство для умножения и-разрядных чисел, содержащее и/2 разрядный буферный регистр, (2 и)-разрядный накапливающий сумматор, матрицу из и+и-- элементов И, содержащую и/2 строк и и+1 столбцов, первую группу из 2 иэлементов ИЛИ, вторую группу из и/2 элементов ИЛИ, группу из и/2 дешифраторов, первую группу из и/2 элементов И, вторую группу из и/2 элементов И, первый и второй элементы ИЛИ, группу из и коммутаторов и.третью группуиз и/2 элементов И, причем входы разрядов множимого устройства соединены прямо и со сдвигом на один разряд в сторону старших соответственно с первыми и вторыми инФормационными входами коммутаторов группы, выходы которых соединены соответственно с первыми входами эле 1374217ментов И столбцов матрицы, первыевходы элементов И (п+1)-го столбцаматрицы объединены и соединены с входами старшего разряда множимого уст 5ройства, входы К-го элемента ИЛИ первой группы (К=1,2п) соединеныс выходами К+2-2(1-1) -х элементовИ д-х строк матрицы (д=1,2п/2),выходы элементов ИЛИ первой группы 1 Осоединены соответственно с входами разрядов с третьего по (2 п)-й накапливающего сумматора, выходы первого и второго элементов И первой строки матрицы соединены соответственнос входами первого и второго разрядовнакапливающего сумматора, входы старшего и младшего разрядов каждой пары разрядов множителя устройства соединены соответственно с первым и вторым 20 входами соответствующего дешифратора,выходы элементов И первой группы соединены соответственно с входами первого элемента ИЛИ, прямой выход ко" торого соединен с первыми управляющи ми входами коммутаторов группы, выходы элементов И второй группы соединены соответственно с входами второго элемента ИЛИ, первые входы элементов И первой и второй групп соединены с вторыми входами элементов И соответствующих строк матрицы и входами соответствующих разрядов буферного регистра, вход разрешения записи которого соединен с тактовым входом накапливающего сумматора и с тактовым входом устройства, о т л и ч а - ю щ е е с я тем, что, с целью расширения функциональных возможностей за счет умножения отрицательных чисел, оно содержит третью группу изи/2 элементов ИЛИ, четвертую группу из и/2 элементов ИЛИ и и/2 разрядный комбинационный сумматор, д-я строка матрицы элементов И дополнительно содержит иэлементов И,45причем третий вход 1-го дешифратора группы (=2,3,р/2) соединен с первым входом (3-1)-го дешифратора группы, третий вход первого дешифра" тора группы является входом логичес кого нуля устройства, первые выходы дешифраторов группы соединены с первыми входами соответствующих элементов ИЛИ второй и третьей группы, вторые выходы дешифраторов группы соединены с вторыми входами соответствующих элементов ИЛИ второй и третьей группы и первыми входами соответствующих элементов ИЛИ четвертой группы, третьи выходы дешифраторов группы соединены с третьими входами соответствующих элементов ИЛИ второй группы, четвертые выходы дешифраторов группы соединены с четвертыми входами соответствующих элементов ИЛИ второй группы и вторыми входами соответствующих элементов ИЛИ четвертой группы, выходы элементов ИЛИ третьей группы соединены с вторыми входами соответствующих элементов И первой группы, выходы элементов ИЛИ четвертой группы соединены с вторыми входами соответствующих элементов И второй группы, инверсные выходы элементов ИЛИ второй группы соединены с входами соответствующих разрядов первого слагаемого комбинационного сумматора, выходы разрядов суммы которого соединены с первыми входами соответствующих элементов И третьей группы, вторые входы которых соединены с прямыми выходами соответствующих элементов ИЛИ второй группы, первые входы элементов И столбцов с (и+2)-го (2 п)-й матрицы соединены с входом старшего разряда множимого устройства, выходы элементов И третьей группы соединены с вторыми входами элементов И соответствующих строк матрицы, вход переноса комбинационного сумматора соединен с входом логической единицы устройства, выход переноса комбинационного сумматора является выходом окончания умножения устройства, инверсный выход первого элемента ИЛИ соединен с вторымиу управляющими входами коммутаторов группы, выход второго элемента ИЛИ соединен с входом инвертирования накапливающего сумматора, выходы разрядов буферного регистра соединены с входами соответствующихразрядов второго слагаемого комбинационного сумматора,1374217 О 0 0 О 0 0 0 0 00 О 0 0 0 0 0 0 О 0 0 0 0 0 О 0 0 О О 0 О 0 Составитель А.КлюевРедактор И.Рыбченко Техред А.Кравчук КорректорВ,Гир аказ 603/45 Тираж 704 ВНИИПИ Государственного комитета С по делам изобретений и открытий 113035, Москва, Ж, Рушская наб., д, Под ССР но дприятие, г. Ужгород, ул. Проектна зводственно-полиграфическое Первый вход дешифратораХ (ст.раз-д анализ. пары) Ф Второй вход дешифратора Х (мл.раз-д анализ. пары) Третий входдешифратораХ (ст,раз-д предыдущейпары) Первый,выходУ дешифратора

СмотретьЗаявка

4100190, 04.08.1986

МИНСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ

ЛОПАТО ЛИЛИЯ ГРИГОРЬЕВНА, ШОСТАК АЛЕКСАНДР АНТОНОВИЧ

МПК / Метки

МПК: G06F 7/52

Метки: разрядных, умножения, чисел

Опубликовано: 15.02.1988

Код ссылки

<a href="https://patents.su/5-1374217-ustrojjstvo-dlya-umnozheniya-razryadnykh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для умножения -разрядных чисел</a>

Предыдущий патент: Четырехвходовый одноразрядный сумматор

Следующий патент: Цифровой функциональный преобразователь

Случайный патент: Гидравлический амортизатор ударного действия