Последовательно-параллельное устройство для умножения чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1413625

Авторы: Масленников, Шарипов

Текст

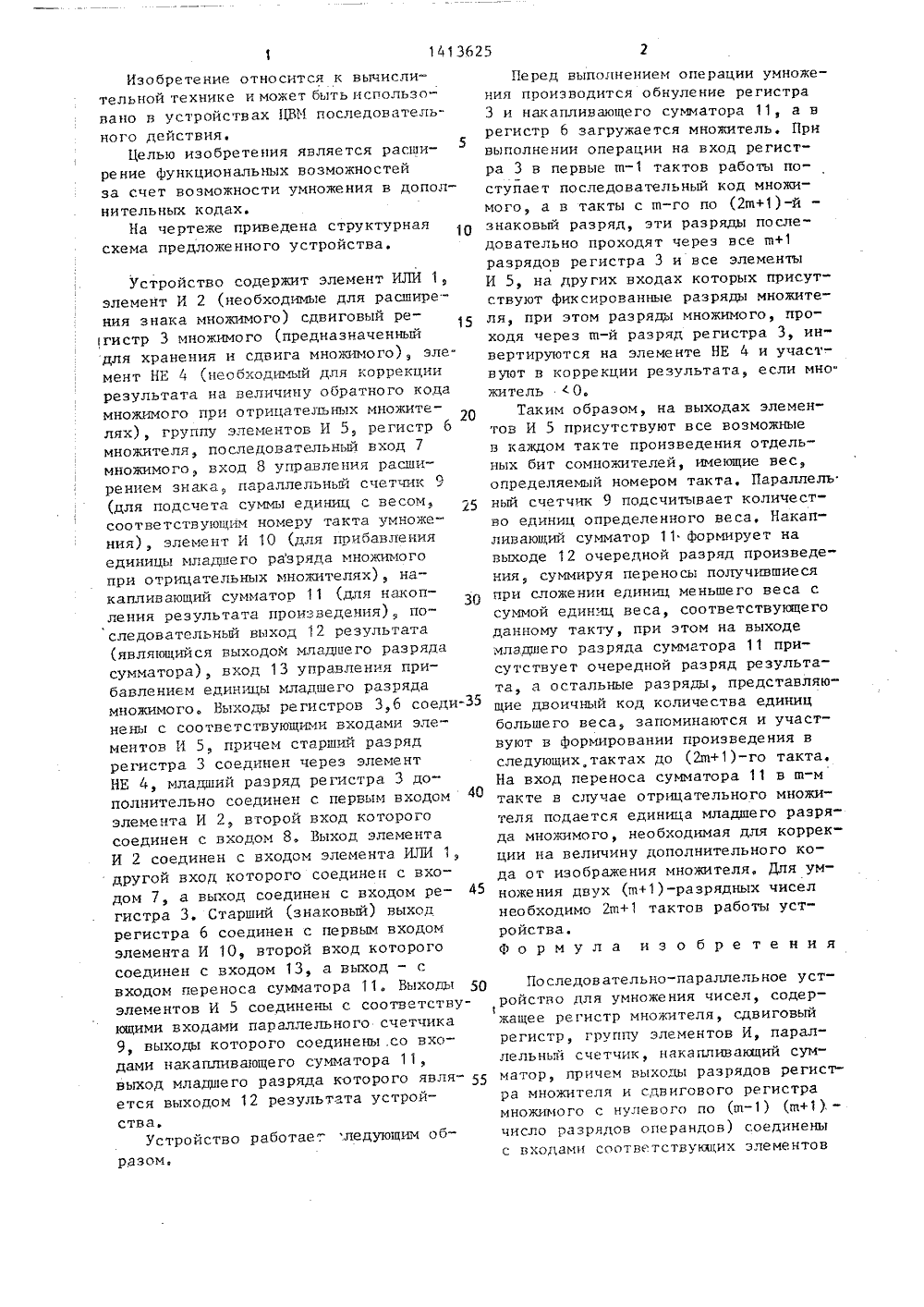

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК А 1 С 06 Р ОПИСАНИЕ ИЗОБРЕТЕНИЯ цифровых60 ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ АВТОРСКОМУ СВИДЕТЕЛЬСТ(54) ПОСЛЕДОВАТЕЛЬНО-ПАРАЛЛ.ЛЬНОЕ УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ(57) Изобретение относится к вычислительной технике и может быть использовано в ЦВМ последовательного действия. Цель изобретения " расширениефункциональных возможностей устройстваза счет умножения в дополнительныхкодах. Устройство содержит элементыИЛИ 1 и И 2 для расширения знаковогоразряда множимого, поступающего последовательно с входа 7, сдвиговый регистр 3 множимого, выход старшегоразряда которого инвертируется на элементе НЕ 4, и с его выхода подаетсяна соответствующие входы элементовИ 5 для получения в каждом такте логических произведений разрядов множимого с фиксированными разрядами множителя, поступающими с регистра 6,Старший разряд множителя подается напервый вход элемента И 10, которыйсовместно с элементом НЕ 4 служит длякоррекции результата на величину дополнительного кода множимого. В каждом такте работы устройства на выходах блока элементов И 5 присутствуютединицы веса, равного весу определяемого в очередном такте разряда произведения, параллельный счетчик 9 подсчитывает количество этих единиц вдвоичном коде, который суммируется внакапливающем сумматоре 11 с соответствующим кодом количества единиц, накопившихся в предыдущих тактах, Навход переноса сумматора на ш-м тактепо сигналу с входа 13 при отрицательных множителях подается единица младшего разряда множимого. Сигнал с. Рвхода 8 управления расширяет знаковыйразряд. Таким образом, в каждом тактеработы устройства с выхода младшегоразряда сумматора на выход 12 поступа-ет скорректированный результат, равный произведению сомножителей в дополнительном коде. 1 ил,Изобретение относится к вычисли" тельной технике и может быть использовано в устройствах ЦВМ последовательного действия.Целью изобретения является расширение функциональных возможностей за счет возможности умножения в дополнительных кодах.На чертеже приведена структурная схема предложенного устройства,Устройство содержит элемент ИЛИ 1,элемент И 2 (необходимые для расширения знака множимого) сдвиговый ре гистр 3 множимого (предназначенныйдля хранения и сдвига множимого), элемент НЕ 4 (необходимый для коррекциирезультата на величину обратного кодамнолцмого при отрицательных множителях), группу элементов И 5, регистр 6множителя, последовательный вход 7множимого, вход 8 управления расширением знака, параллельный счетчик 9(для подсчета суммы единиц с весом,соответствующим номеру такта умножения), элемент И 10 (для прибавленияединицы младшего разряда множимогопри отрицательных множителях), накапливающий сумматор 11 (для накопления результата произведения), последовательный вьход 12 результата(являющийся выходом младшего разрядасумматора), вход 13 управления прибавлением единицы младшего разрядамножимого. Выходы регистров 3,6 соеди иены с соответствующими входами элементов И 5, причем старший разрядрегистра 3 соединен через элементНЕ 4, младший разряд регистра 3 дополнительно соединен с первым входом 4 Оэлемента И 2, второй вход которогосоединен с входом 8. Выход элементаИ 2 соединен с входом элемента ИЛИ 1,другой вход которого соединен с входом 7, а выход соединен с входом регистра 3, Старший (знаковый) выходрегистра 6 соединен с первым входомэлемента И 10, второй вход которогосоединен с входом 13, а выход - свходом переноса сумматора 11, Выходы 50элементов И 5 соединены с соответствующими входами параллельного счетчика9, выходы которого соединены .со входами накапливающего сумматора 11,выход младшего разряда которого является выходом 12 результата устройства.Устройство работае-ледующим образом,Перед выполнением операции умножения производится обнуление регистра 3 и накапливающего сумматора 11, а в регистр б загружается множитель. При выполнении операции на вход регистра 3 в первые щтактов работы поступает последовательный код множимого, а в такты с щ-го по (2 щ+1)-й знаковый разряд, эти разряды последовательно проходят через все щ+1 разрядов регистра 3 и все элементы И 5, на других входах которых присутствуют фиксированные разряды множителя, при этом разряды множимого, проходя через щ-й разряд регистра 3, инвертируются на элементе НЕ 4 и участвуют в коррекции результата, если мно" житель 4 О.Таким образом, на выходах элементов И 5 присутствуют все возможные в каждом такте произведения отдельных бит сомножителей, имеющие вес, определяемый номером такта, Параллель ный счетчик 9 подсчитывает количество единиц определенного веса. Накапливающий сумматор 11 формирует на выходе 12 очередной разряд произведения, суммируя переносы получившиеся при сложении единиц меньшего веса с суммой единиц веса, соответствующего данному такту, при этом на выходе младшего разряда сумматора 11 присутствует очередной разряд результата, а остальные разряды, представляющие двоичный код количества единиц большего веса, запоминаются и участвуют в формировании произведения в следующих, тактах до (2 щ+1)-го такта. На вход переноса сумматора 11 в щ-м такте в случае отрицательного множителя подается единица младшего разряда множимого, необходимая для коррекции на величину дополнительного кода от изображения множителя. Для умножения двух (щ+1)-разрядных чисел необходимо 2 щ+1 тактов работы уст" ройства.Формула из о бре тения По следов атель но-параллель ное у стройство для умножения чисел, содержащее регистр множителя, сдвиговый регистр, группу элементов И, параллельный счетчик, накапливающий сумматор, причем выходы разрядов регистра множителя и сдвигового регистра множииого с нулевого по (щ) (щ+1).- число разрядов операндов) соединены с входами соответствующих элементовСоставитель А.КлюевРедактор М.Келемеш Техред Л.Олейник Корректор О,Кравцова Заказ 3787/52 Тираж 704 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж, РаушскаФ наб д, 4/5Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 3 14136 И группы, выход ш-го разряда регистра множителя соединен с первым входом ш-го элемента И группы, выходы элементов И группы соединены с входами параллельного счетчика, выхо 5 ды которого соединены с входами накапливающего сумматора, выход младшего разряда которого является выходом результата устройства, о т л ич а ю щ е е с я тем, что, с целью расширения функциональных возможностей за счет воэможности умножения в дополнительном коде, оно содержит элементы И, КПИ, НЕ, причем первый вход первого элемента И соединен с выходом нулевого разряда сдвигового регистра множимого, второй вход первого 25 4элемента И соединен с входом управления расширением знака устройства, выход первого элемента И соединен спервым входом элемента ИЛИ, второй .вход которого соединен с входом множимого устройства, а выход соединенс входом сдвигового регистра множимого, выход ш-го разряда которого сое.динен через элемент НЕ с вторым вхо-,дом ш-го элемента И группы, первыйвход которого соединен с первым входом элемента И, второй вход которогосоединен с входом управления прибавлением единицы младшего разряда множимого устройства, а выход соеднненс входом переноса накапливающегосумматора.

СмотретьЗаявка

4184590, 19.01.1987

ПРЕДПРИЯТИЕ ПЯ В-2887

ШАРИПОВ РАШИТ ШАРИПОВИЧ, МАСЛЕННИКОВ ВИТАЛИЙ БОРИСОВИЧ

МПК / Метки

МПК: G06F 7/52

Метки: последовательно-параллельное, умножения, чисел

Опубликовано: 30.07.1988

Код ссылки

<a href="https://patents.su/3-1413625-posledovatelno-parallelnoe-ustrojjstvo-dlya-umnozheniya-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Последовательно-параллельное устройство для умножения чисел</a>

Предыдущий патент: Арифметическое устройство с переменной длиной операндов

Следующий патент: Устройство для вычисления функций двух аргументов

Случайный патент: Устройство коррекции