Патенты с меткой «вычисления»

Устройство для вычисления квадрата и квадратного корня

Номер патента: 1386991

Опубликовано: 07.04.1988

Авторы: Лебединский, Филоненко, Хоменко, Чумак

МПК: G06F 7/552

Метки: вычисления, квадрата, квадратного, корня

...устройства. Перед началом работы в режиме вычисления квадратного корня на вход сброса устройства поступает сигнал (фиг. За), устанавливающий86991 33реверсивный счетчик 1 и накапливающий сумматор 2 в нулевое состояние (фиг. Зе,д) соответственно.Прямоугольные положительные импульсы, представляющие собой число-импульсный код числа (фиг. Зб), поступают на информационный вход устройства. Пройдя через второй элемент И 7, они поступают на вычитающий вход реверсивного счетчика 1. Каждый раз, когда содержимое реверсивного счетчика 1 равно нулю (фиг. Зе) и приходит импульс на его вычитающий вход, на его выходе отрицательного переноса появляется импульс (фиг. Зв), который проходит через элемент ИЛИ 5 и поступает на вход приема информации...

Устройство для вычисления интервальной взаимокорреляционной функции

Номер патента: 1387012

Опубликовано: 07.04.1988

МПК: G06F 17/15

Метки: взаимокорреляционной, вычисления, интервальной, функции

...на вход 1 устройства, вырабатывает одиночный импульс на соответствующем выхо 13870125 10 15 20 25 30 35 40 45 50 55 де распределителя 6 импульсов и перекидывает триггер 7 в единичное состояние. Элемент И 8 открывается и тактовые импульсы от генератора 17 поступают в сумматор 9. С приходом третьего входного импульса второй группы на вход 3 устройства разрешается прохождение информации с сумматоров 9, равной сумме тактовых импульсов, поступающих в сумматор 9 от генератора 17 в промежутке времени между первым импульсом второго потока, и сумме , тактовых импульсов, поступающих в сумматор 9 в промежутке времени между вторым входным импульсом первого потока и третьим импульсом второго потока на входы дешифраторов 20 и 20 адреса. Эти суммы...

Устройство для вычисления булевых производных

Номер патента: 1388843

Опубликовано: 15.04.1988

МПК: G06F 17/10, G06F 7/00

Метки: булевых, вычисления, производных

...14 и 14 арифметических ячеек 5 подблока 4 присутствуют величины 7(0,0,0) (0,0,1); Г(0,0,0)"(0,0,1); Р(0,1,0) (0,1,1); .(0,1,О) (0,1,1); Р(1,О,О) (1,0,); (1,0,0)(1,0,1); Г(1,1,0)(1,1,1); 7(1,1,0)Т(1,1,1). С выходов 14 и 14 арифметических ячеек 5 подблока 4, информация передается на входы подблока 4Благодаря соединениям на вуодах 13 и 13 арифметических ячеек 5 подблока 4 о присутствуют сигналы (О,О,О) (0,0,1); (0,1,0) (0,1,); (О,О,О). Г(О,О,); Г(0,1,0), Г(0,1,); 7(1,0,0) (1,О,1); У(11,0) (1,1,1); 2(1,0,0) (1,0,1); У(1,1,0) Х(1,1,1) соответственно, Через выходы 12, и 12 на адресные входы мультиплексоров 8, и 8арифметических ячеек 5 подблока 4поступает кодовая комбинация 00, В результате информация с первых информационных входов...

Устройство для вычисления функций

Номер патента: 1388848

Опубликовано: 15.04.1988

Автор: Плющ

МПК: G06F 7/38

Метки: вычисления, функций

...регистр2.1 числа, а значение величины рв регистр 2.2 числа, величины - Я 1 "в регистр 2.3 числа, а значение величины Я, в регистр 2.4 числа. Навтором такте работы устройства первый блок 9,1 формирования итерационных коэффициентов вычислит значениевеличины, равноеЬ; = 3+1-к=1+1-0,5=1,5.Аналогично второй блок формирова"ния итерационных коэффициентов 9.2вычислит значение а.а=х(Е)=0,51 =0,5,На выходах первого и второго сумматоров 4. 1 и 4.2 образуются значениявеличинр=Ь р+азра=1,5 1+0,5 1=2,=Ь Я+а Я,=1,5 0,5+0,5 1=1,25,По окончании переходных процессовв сумматорах 4.1 и 4.2 синхроимпульсом, выработанным схемой 5 синхронизации, значения р изапишутся врегистры 2. 1 и 2.3 чисел, а значения, р и Я - в регистры 2.2 и 2,4 чисел,этим же...

Арифметическое устройство для вычисления коэффициентов фурье

Номер патента: 1388893

Опубликовано: 15.04.1988

Авторы: Карасев, Савенкова, Шангин

МПК: G06F 17/14

Метки: арифметическое, вычисления, коэффициентов, фурье

...18 записываются ввыходные регистры 19 н 20, а затем вОЗУ. При втором цикле алгебраическогосуммирования на выходах сумматоров17 и 18 образуются суммы:Таким образом, дополнительная опеРация, необходимая для обработки действительных массивов, выполняется натом же самом оборудовании, что и баЗовая операция БПФ. Операция умножения комплексных массивов выполняетсяпри получении команды на входе 30.Преобразование операндов осуществляЕтся в соответствии с выражениями(3) и (4). Управляющие сигналы вырабатываются в соответствии с временной диаграммой на фиг.5, По сигналу32 на входы умножителей записываются.Входные операнды (первый операнд -через сдвигатели, а второй - по вхоДу И). Результаты перемножения через входы мультиплексоров 9-12 (посигналам...

Устройство для вычисления коэффициентов уолша

Номер патента: 1388895

Опубликовано: 15.04.1988

Авторы: Золотой, Садыхов, Шаренков

МПК: G06F 17/14

Метки: вычисления, коэффициентов, уолша

...слабоза" полненных матриц А Следов а тельно (7) можно предстанить как Уолша видааР (х) =, С,М,(х), (2)(:огде С, коэффициенты разложенияР (х) по кусочно-линейнымКфункциям Уолша.Вычисление спектральных коэффициентов С разложения исходного вектора Г цифрового сигнала в базисе кусочно-линейных функций Уолша н матричной форме имеет видС = Г Р , (Э) где Р - матрица системы функций,биортогональной базису кусочно-линейных функцийУолша.Для Ю4 матрица Р без учета постоянной составляющей имеет вид1388895 112 13 14 Формула изобретения Составитель А.БарановТехред М. Ходанич Редактор А.Огар Корректор С.Шекмар Заказ 1582/51 Тираж 704 ПодписноеВИИИПИ Государственного комитета СССРпо делам изобретений и открытий113035, Москва, Ж, Раушская наб д. 4/5...

Устройство для вычисления симметричных булевых функций

Номер патента: 1396137

Опубликовано: 15.05.1988

Автор: Дергачев

МПК: G06F 7/00

Метки: булевых, вычисления, симметричных, функций

...коизобретений и оЖ, Раушска Заказ 2496 5 1 ИИПИ Гос ло делам 35 Москв 11 роизводственло-лолнгряфическое предприятие, г. Ужгород, ул. Проектная,Изобретение относится к автоматике и вычислительной технике и предназначено для реализации симметричных булевых функций четырех н менее переменных.5Цель изобретения - повышение надюкности за счет сокращения количества выводов.На чертеже представлена функциональ 10 ная схема предлагаемого устройстваУстройство содержит входы 1 - б Устройства, элемент РАВНОЗНАЧНОСТЬ 7, элемент НЕРАВНОЗНАЧНОСТЬ 8, элем ент И 9, элемент СЛОЖЕНИЕ ПО МОДУЛЮ ДВА 10, элемент ИЛИ-НЕ 11 и выход 12 устройства.Устройство реализует все симметричные булевые функции четырех переМенных с помощью настройки - подачи на входы модуля...

Устройство для вычисления квадратного корня

Номер патента: 1397904

Опубликовано: 23.05.1988

Автор: Чуватин

МПК: G06F 7/544, G06F 7/552

Метки: вычисления, квадратного, корня

...С 2 " и Р-кл лю 2Предыдущее значение мнимой частиА , приращения А2 ", В2 "+В 2 " поступают соответственно иэлпервого регистра 1, первого 15, четвертого 18 и второго 16 сдвигателейв цепь, состоящую из пятого 9, третьего 7 и первого 5 сумматоров-вычитателей, в результате в первом сумма.торе-вычитателе 5 формируется новоезначение мнимой части А +, комплексно-.35го переменного, которое фиксируетсяв первом регистре 1,ПредЫцущее значение действитель 40 ной части В, приращения В 2кА 2 ф, А 2 " " поступают соответственно иэ второго регистра 2,второго 16, третьего 17 и первого 15сдвигателей в цепь, состоящую из шестого 10, четвертого 8 и второго 6сумматоров-вычитателей, в результатево втором сумматоре-вычитателе 6 формируется новое значение...

Устройство для вычисления полярных координат

Номер патента: 1399730

Опубликовано: 30.05.1988

Авторы: Банников, Камаев, Михайлев, Розенталь

МПК: G06F 7/548

Метки: вычисления, координат, полярных

...разрядов и трех старших разрядов полярных координат, а также значение большей координаты и коэффициент сдвига записываются соответственно в регистр 3 уг ла и в блок 16 вычисления дальности сигналом с выхода признака окончания деления блока 10 деления, В регистр 3 записывается код угла полярных координат вида 2 , где и - разрядность 25 кода угла полярных координат. Генератор 18 импульсов формирует тактовые импульсы, которые производят деление . в блоке 1 О деления и вычисление дальности в блоке 16 вычисления дальности,зо Значение дальности записывается в регистр 17 дальности.В блоке 16 вычисления дальности вычисление основано на принципе умножения большей прямоугольной коорди 35 наты иа величину секонса угла, находящегося в одном из пяти...

Цифровое устройство для вычисления логарифма числа

Номер патента: 1401456

Опубликовано: 07.06.1988

Авторы: Богославский, Крюков, Литвин, Хохлов, Шантырь

МПК: G06F 7/556

Метки: вычисления, логарифма, цифровое, числа

...регистра 2 сдвига. Еслиже Х 72и Х=1, то при записи входК(2ного кода Х в регистр 2 сдвига на егоинверсном выходе старшего разряда появится сигнал логического нуля, таккак триггер 4, управляющий работоймультиплексора, установлен в единичное .состояние, то ко второму входусхемы И 1 сразу же подключается сиг"нал логического нуля. Это означает,что вычисление закончено и значениехарактеристики и мантиссы логарифмавходного кода Х содержится в счетчике 3 и регистре 2 сдвига,Если Х(2 ф, что означает отсутствие единиц в (к/2) - старших разрядоввходного кода Х, то на выходе первого элемента ИЛИ 6 будет сигнал логического нуля и при записи входногокода Х в регистр 2 сдвига триггер 4будет установлен в нулевое состояние.Это означает, что регистр 2...

Матричное устройство для вычисления свертки

Номер патента: 1401477

Опубликовано: 07.06.1988

Авторы: Авгуль, Мищенко, Седухин, Якуш

МПК: G06F 17/16

Метки: вычисления, матричное, свертки

...в ОБ 5, на выходе умножителя.13 формируется значение ы, х которое подается на сумматор 14, навторой вход которого подается значение у, =О (фиг.2). На выходе сумматора 14 формируется значение у =у+1 1+ Ы,х,.На первом такте на первый, второйи третий входы ОБ 5, подаются соответственно элемент ит , нулевой сигнал у=О и элемент х 1, На выходе сумматора 14 ОБ 5 формируется значение у =у+ ы х,.На втором такте на первый, второйи третий входы ОБ 5 подаются соответственно элемент ю р нулевойсигнал у =О,и элемент х. На выходесумматора 14 ОБ 5, Формируется значение у, =ум х В ОБ 5 на первый, второй и третий входы подаютсясоответственно элемент И, , значениеу и х ф . На выходе сумматора 14ОБ 52 формируется значен е у(;ю =и)"уг + шх,На третьем такте...

Устройство для вычисления модуля и аргумента вектора

Номер патента: 1403063

Опубликовано: 15.06.1988

Авторы: Горькуша, Коржук, Куприец, Поваренко

МПК: G06F 7/548

Метки: аргумента, вектора, вычисления, модуля

...операндь чисел а и 17 поступают на входы соответственно первого 13 и второго 14 логарифмических преобразователей, с выходов которых операнды чисел а и б поступают соответственно на входы уменьшаемого и вычитаемого вычитателя 15.Количество ги старших разрядов числапоступающих на вход приоритетного п 7 ифратора 10, выбираются из соотношения т=и - К.Приоритетный шифратор 10 совместно с первым двигателем 11 производит сдвиг так, чтооы на выходе первого сдвигателя 11 старшая значащая цифра числа а находилась в старшем разряде.С выхода вычитателя 15 операнд числа с поступает на входы косинусного 16 и арктангенсного 17 преобразователей, которые производят преобразование информации в соответствии с функциональными зависимостямиа= ---- . -...

Устройство для вычисления обратной величины нормализованной двоичной дроби

Номер патента: 1405050

Опубликовано: 23.06.1988

Авторы: Белик, Коновалова

МПК: G06F 7/52

Метки: величины, вычисления, двоичной, дроби, нормализованной, обратной

...5, уменьшая значение у1 до тех пор, пока на выходе умножителя 2 не получится г, = 1,00, при этом у = у - д, отличается от у1 ина 2 , где п - разрядностьчисла хПри последующем изменении входного аргумента х в сторону увеличения (х + д х) или уменьшения ,х - д х) на выходе умножителя 2 меняется код г 7 1,0.0 или г1,00.Вследствие изменения кода г и реализации логических операций на элементах НЕ 6, ИЛИ 7 и И 9 импульсы от генератора 8 поступают соответственно или на вычитающий счетный вход реверсивного счетчика 11, или на суммирующий вход. Таким образом, в устройстве образуется переходный процесс, удерживающий значение кода на выходе умножителя 2 в пределах г = 1,0 О+2, что отражает тот факт, что на выходе устройства установился...

Устройство для вычисления угла и значения корректирующей массы

Номер патента: 1405076

Опубликовано: 23.06.1988

Авторы: Кобельков, Козлов, Кочетов, Миркин, Поляковский, Турбин

МПК: G06G 1/04

Метки: вычисления, значения, корректирующей, массы, угла

...А/А и А /Ао, необходимые длярасчета угла и значения корректирующей массы. Формула изобретения Составитель В. СуторминТехред И.Дидык 1(орректор И.Иуска Редактор В, Петраш Тираж 704 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская наб д, 4/5Заказ .3107/54 Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 Изобретение относится к машиностроению и может быть использовано при проведении балансировки по методу двух пусковЦель изобретения - повышение удобства расчета промежуточных относительных величин за счет приведения началь ной вибрации к единице и получениядругих отношений по той же шкале.На чертеже представлено предлага емое устройство.Устройство состоит из...

Устройство для вычисления двумерного быстрого преобразования фурье

Номер патента: 1408442

Опубликовано: 07.07.1988

МПК: G06F 17/14

Метки: быстрого, вычисления, двумерного, преобразования, фурье

...записи блока 1 оператюной памяти и записывается в него по тем же адресам, по которым происходило счи 8тывание в первых 6 тактах. Это обеспечивается повторением управляющих сигналов на входах коммутаторов 4 и 5 (фиг. 3, 08 и О 6) при неизменном состоянии счетчика 8 строк и счетчика 9 столбцов. Таким образом, после вторых (и каждых четных) 16 тактов ГТИ 17 заканчиваются выполнение базовой операции и запись результата вычислений в блок 1 оперативной памяти. Полное выполнение первой (и каждой последующей) итерации осуществляется за 32 такта. На третьих 16 тактах ГТИ 17 начинается выполнение второй итерации первого этапа вычислений. При этом задним фронтом импульса с выхода триггеров 12-16 на 32 происходит переключение счетчика 8 строк в...

Устройство для вычисления скользящего среднего

Номер патента: 1410058

Опубликовано: 15.07.1988

Авторы: Ахметьянов, Семенов

МПК: G06F 17/18

Метки: вычисления, скользящего, среднего

...сумматора 1, прибавляя к его содержимому значение текущего элемента окна , кроме этого , данный ТИ поступае т на вход счетчика 9, увеличивая е го содержимое на " 1 " , и через второй элемент ,1 4 задержки на сдвигающий вход регистра 7 , сдвиг ая его содержимое на один разряд всторону младших. Время задержки элемента 14 задержки выбирается исходя из времени выполнения операции сло-, жения сумматором 1. Следующий ТИ вновь через третий 12 элемент И проходит на первый 10 и второй 11 элементы И и при наличии в младшем разряде сдвигового регистра 7 "1" процесс вычисления повторяется, при наличии в младшем разряде этот ТИ проходит через первый элемент Й 10, изменяет содержимое адресного счетчика 6 так, что из блоков памяти 4 и 5...

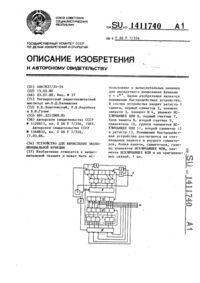

Устройство для вычисления экспоненциальной функции

Номер патента: 1411740

Опубликовано: 23.07.1988

Авторы: Гузик, Золотовский, Коробков

МПК: G06F 7/556

Метки: вычисления, функции, экспоненциальной

...сумматор 12, регистр 13, выход14 устройства.Аргумент х записывается в и-разрядный регистр 1, который представляет собой регистр сдвига. Единичныевыходы всех разрядов регистра 1 (кроме старшего) соединены с входами(п)-разрядного комбинационного сумматора 2. Выходы сумматора 2 .соединены с входами регистра 1 со сдвигомна один разряд в сторону старших разрядов, Выход элемента 3 запрета соединен с входом регистра 1, управляю щнм сдвигом в нем на один разряд всторону старших разрядов, Выход элемента И 4 соединен с входом, управляющим записью сдвинутой суммы изсумматора 2 в регистр 1. Элемент 3запрета и элемент И 4 управляются,сигналом с тактового входа 5 устройства, Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 6, сое-диненный с единичнымивыходами двухстарших...

Устройство для вычисления систем булевых функций

Номер патента: 1411769

Опубликовано: 23.07.1988

МПК: G06F 7/38

Метки: булевых, вычисления, систем, функций

...содержимое соответствующих ячеек которого равно номеру входов, которые с помощью мультиплексора 24 подключаются на выходы 4, При подаче управляющего сигнала на счетный вход счетчика 22 (начальное состояние установлено по второму управляющему входу) после окончания переходных процессов в узле памяти и мультиплек 1411769Ур у Уу Ур ь Уру Угруппы у, у и разбита на две Уйф У 4 ф УрДлЯвычисления исходной системы должны быть обработаны две последовательности переменных х хф, х.х , х, х, х. Таким образом, узел 23 памяти содержит в семи последовательных ячейках, начиная с ячейки с нулевым адресом, числа 1, 2, 5, 2, 3, 4, 5. Полагая, что программа вычисления расположена с нулевого адреса, содержимое памяти изображают таблицей, В каждой ячейке...

Устройство для вычисления функций

Номер патента: 1411775

Опубликовано: 23.07.1988

Авторы: Игнатьева, Плешаков, Редькин

МПК: G06F 17/10

Метки: вычисления, функций

...отрицательные разряды результата заносятся в сдвиговые регистры 6.1 и 6.2 соответственно.Разность положительной и отрицательной 1-разрядных частей результа 50 та, сформированная в вычитателе 6,3 в дополнительном двоичном коде, заносится по стробу С, с (И+4)-го выхода распределителя 1 импульсов в регистр 6,4 результата и может быть считана с его выхода в течение сле 55. дующих 1 тактов работы устройства в параллельном либо последовательном коде. Периодичность вычисления значений функции в режиме конвейерной обработ - ки данных определяется временем считывания тп-разрядного аргумента иэ сдвигового регистра данных первого блока 2 преобразования кода, которое составляет Т = Т,тп, где Тс - период следования синхроимпульсов С.Формула...

Устройство для вычисления функций двух аргументов

Номер патента: 1413626

Опубликовано: 30.07.1988

Авторы: Барметов, Боев, Евтеев

МПК: G06F 7/544

Метки: аргументов, вычисления, двух, функций

...регистр накапливающего сумматора 13 положительным фронтом синхросигнала, поступающего на его стробовый вход.Параллельно с преобразованияминулевого коэффициента мультиплексор 405 пропускает на адресный выход блока,6 памяти код младшей части первогоаргумента, с блока 6 памяти считывается логарифм по основанию двамладшей части аргумента и это значение поступает на вход второго слагаемого сумматора 9 и информационныйвход буферного регистра 7. На входпервого слагаемого сумматора 9 мультиплексор 8 подает код нуля, Логарифм младшей части первого аргумента,проходя через сумматор 9 положительным фронтом синхросигнала, заносится в буферный регистр 11.Этот же положительный фронт синхросигнала увеличивает код счетчика20 на единицу, что приводит...

Устройство для вычисления параметров сеток для решения разностных уравнений

Номер патента: 1413642

Опубликовано: 30.07.1988

Авторы: Звиргздиньш, Спалвинь, Шланген, Янбицкий

МПК: G06F 17/13

Метки: вычисления, параметров, разностных, решения, сеток, уравнений

...выходаузла 118 памяти команд через мультиплексор 123 с выхода регистра 142код адреса конечной занятой ячейкиузлов 126 и 127 оперативной памятипоступает на второй вход сумматора122, на первом входе которого действует суммарный код адреса 1,1-го уэ"ла и код константы (О,-С) . С выходасумматора 122 код адреса поступаетна первый вход узла 126 оперативнойпамяти, в него записывается параметрИ) 1. Содержимое регистра 4увеличивается на единицу, и, как было описано, формируется код адресас константой (-С,О), поступающий напервый вход узла 127 оперативной памятив него записывается параметрИ")( ,После завершения нечетной редукции в узлах 103 и 104 оперативной па"мяти хранятся массивы а .1 и Ь(з ц ос.(сну) 1 у основной и (а)и (а) (рвспомогательной...

Устройство для вычисления суммарного значения дискретно увеличивающегося параметра в различных точках контроля

Номер патента: 1416966

Опубликовано: 15.08.1988

МПК: G06F 17/00

Метки: вычисления, дискретно, значения, параметра, различных, суммарного, точках, увеличивающегося

...на первом входе только элемента И 4 Е-го измерительного канала присутствует "1", поэтому появляется " 1" и на выходе этого элемента И 4, которая поступает стробом записи на вход записи регистра 5, на информационном входе которого к этому времени установился результат суммирования, записывая результат в регистр 1-го измерительного канала. "1" с выхода элемента И 4 также поступает и на вход сброса элемента памяти, устанавливая его в начальное состояние. На выходе элемента 3 устанавливается "О", что приводит к появлению "0" и на выходе элемента И 4, т.е. строб записи заканчивается к появлению "0" на управляющих входах коммутаторов 7 и. 8, закрывая этим прохождение информации на шины 13 и 14, На этом процесс вычисления суммарного значения...

Устройство для параллельного вычисления цифровой двумерной свертки

Номер патента: 1416976

Опубликовано: 15.08.1988

Авторы: Донченко, Кучеренко, Матвеев, Очин

МПК: G06T 7/60

Метки: вычисления, двумерной, параллельного, свертки, цифровой

...работы устройства.В зависимости от сигнала на первом входе 17 управления режимом работы устройства, каждый из коммутаторов 16 д (ш=1,М) передает на выходы 9 соответствующих блоков выТчисления 1 либо частичные суммын(М+ )либо частичные суммын (ир 11 егП 31х И которые далее суммируются суммирующим блоком с образованием либо результата ЦДС с ЯСС размером МрИ (в первом случае), либо результата ЦДС с произвольным ядром размером М хИ+1х ( - у-)35Для реализации операции свертки с ядром размером (2 М) х М, обладающим центральной симметрией, или с0+1ядром размером (2 М) х ( в ), симметричным относительно центральной строки в устройство дополнительно вводятся (М) сумматоров, причем выходы 1-го (11,М) сумматора 18 (фиг. 7) соединены с первыми...

Устройство для вычисления остатка по модулю от двоичного числа

Номер патента: 1417192

Опубликовано: 15.08.1988

МПК: H03M 7/18

Метки: вычисления, двоичного, модулю, остатка, числа

...коммутатора 9, Содержимое регистров 6 и 7 произвольно.На первом такте число А, определяемое ш старшими разрядами преобразуемого числа Х, преобразуются блоком 2 в остаток В по модулю Р.Аналогично на выходе блока 3 получается остаток В 1, от числа А, по модулю Р. Значение числа В через коммутатор 8 поступает на вход блока 4 где оно умножается на константу Р по модулю Р и складывается с Вб, в сумматоре 5.Таким образом, по окончании переходных процессов на выходе сумматора 5 имеем Результат суммирования записывается в момент поступления импульса по входу 11,4 в регистр 6.На втором такте преобразования в момент поступления импульса по входу 11.4 в регистр 6.На втором такте преобразования в момент поступления импульса по входу 11,1 содержимое...

Устройство для вычисления полинома -й степени

Номер патента: 1418708

Опубликовано: 23.08.1988

Авторы: Валов, Виткин, Угрюмов

МПК: G06F 7/544

Метки: вычисления, полинома, степени

...табл. 3.По сигналу записи с входа 8 записи устройства в регистры мультиплексоры 1.1-1,4 заносятся значения коэфФициентов полинома с входов 6,1-6,4 коэффициентов полинома. На выходах сумматоров -го .яруса появляется информация о соответствующем коэффициенте полинома аПоступление данных на вход 5 аргумента устройства сопровождается стробирующим сигналом пуска на входе 7 запуска устройства, По сигналу пуска в устройстве осуществляется запись значения аргумента в регистр 11 ар" гумента, установка счетчика 14 в нулевое состояние, а также по заднему фронту импульсного сигнала пуска производится запуск генератора 13 тактовых импульсов. На выходе 9 готовности результата устройства появляется ну-левой сигнал.При такой дисциплине запуска...

Устройство для вычисления функции вида f( )=

Номер патента: 1418709

Опубликовано: 23.08.1988

Автор: Кашалов

МПК: G06F 7/552

Метки: вида, вычисления, функции

...импульс обнуляет младшие (%-Ч) разрядов счетчика 1. По заднему фронту счетного 25 импульса первый триггер 4 переключается в единицу, которая поступает на первый и второй элементы И 16 и 17. Элемент И 17 открыт сигналом логической "1" с инверсного выхода вто- ЗО рого триггера 18. Б этом случае тактовые импульсы (синхросерии С с пе" .риодом) с генератора 15 тактовых импульсов через открытый элемент И 17 поступают на вход разряда с весом 2 первого счетчика 1, увеличивая его содержимое на квант 2 1.Тактовый импульс поступает также на тактирующий вход первого сумматора 4, в котором осуществляется сло жение его содержимого (Ь Я(рс кодом второго регистра 3 (ь Я 1(ри вычисление, таким образом, локального тренда д Я (р) . Спустя время,...

Устройство для вычисления скользящего спектра

Номер патента: 1418746

Опубликовано: 23.08.1988

Авторы: Грязнов, Каневский, Куц, Сергиенко

МПК: G06F 17/14

Метки: вычисления, скользящего, спектра

...блока 3 памяти с выходаузла 40, а два старших разряда - свыхода коммутатора 5, на управляющемвыходе 18 которого присутствует еди"ничное значение, на управляющем выходе 19 во второй итерации присутствует единичнсе значение и требуемая последовательность весовых коэффициениМтов И , на которое требуется домножить операнцы второй итерации, посту"пает на вход блока 4 БПФкоэффициен 1ты И записаны в блоке 8 памяти (коэффициентов) И в последовательностиопределяемой алгоритмом БПФ.В 68 и 70-м тактах работа устройства аналогична 66-му такту, В 71-м такте выполняется очередная запись исходных операндов, кроме того, на управляющих входах коммутатора 39 присутствует код 010, который обеспечивает прохождение на вход регистра32 кода И-г = 12.В 72-м...

Устройство для вычисления функции 1-х

Номер патента: 1420600

Опубликовано: 30.08.1988

Авторы: Золотовский, Коробков

МПК: G06F 7/552

Метки: вычисления, функции

...формируетсяРегистр б представляет собой обычный в триггере 7 и с его выхо50о выхода поступап )-разрядный регистр суммы. Уп- ет на выход 12 и в регистр 9. Поравление записью суммы в него произ- окончании п+1 цикла с выходов 12, 13водится по вхо 3 Вь о5 соеду . и ды сумматора может быть считая параллельный1динены с входами регистра б с11р езультатй кода.перекосом на 2 разряда, благодарячему осуществляется сдвиг суммы на . 552 разряда в сторону старших разрядов.По завершении вычислений искомаяфункция У считывается с выхода 121420600 Цикл 1 ВС 6 ф 111131111 00000000 ЛС 2 ф 10031101 ТР 7 ф 1 ВС 90000000 Хг00301 0000000001 51 т 0 5ООООООООООО 1 О 11 О По сигналу Сг По сигналу С тр 7О Хорракгрга 5,ОООООООООО ОО 1 О 1Цикл 2 ВСЬ11131101 0110100...

Устройство для вычисления систем булевых функций

Номер патента: 1424005

Опубликовано: 15.09.1988

МПК: G06F 7/00

Метки: булевых, вычисления, систем, функций

...упрззлеция, вход 28 запускаустройств, пятый выход 29 блока 12 40упрдпленця,Граф-схема работы блока упрдьленця 1 фцг. 2) содержит следующие обозцд сцця мцкроопердццй и признаков:45Л 1 - микроопердцця одновременного.сброса в Осчстчцкд, регистров,регистров команд, эдписц информациив сдвцгающцй регистр с входов дляподачи переменных, усгдцовкд пРизнака готовности результата рдвным О(т.е, результат отсутствует);Л 2 - микрооперация записи в регистры комднд,А 3 - микроопе 1)ацця записи в регистры,Л 4 - микрооперация одновременногосдвига сдвигающего регистра и увеличения счетчика на 1; А 5 - установка признака готовности результата равным 1;Р - признак окончания вычислений всеми обрабатывающими блоками устройства, При Р = 0 каждый иэ них...

Устройство для вычисления систем булевых функций

Номер патента: 1424007

Опубликовано: 15.09.1988

МПК: G06F 7/00

Метки: булевых, вычисления, систем, функций

...на вход регистра 5 адреса (в младший разряд), В регистр 9 записывается информация, поступающая из регистра 4 команд, В шинные формирователи 6 из блока 13 управления пода 10 ется сигнал, который устанавливает шинные формирователи 6 в состояние импеданса, при этом блок 11 отключен от выхода регистра 5 адреса (режим считывания из стека). Мультиплексор15 7 настраивается на передачу значений из регистра 9, С выхода мультиплексора 7 значения поступают на адресные входы блока 8 памяти, откуда информация заносится в регистр 4 команд. При переходе к выполнению подпрограммы происходит настройка мультиплексора 3 по управляющим сигналам, поступающим в регистр 10, которые затем передаются на управляющие входы муль 25 типлексора 3, на прием...