Устройство для вычисления экспоненциальной функции

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1411740

Авторы: Гузик, Золотовский, Коробков

Текст

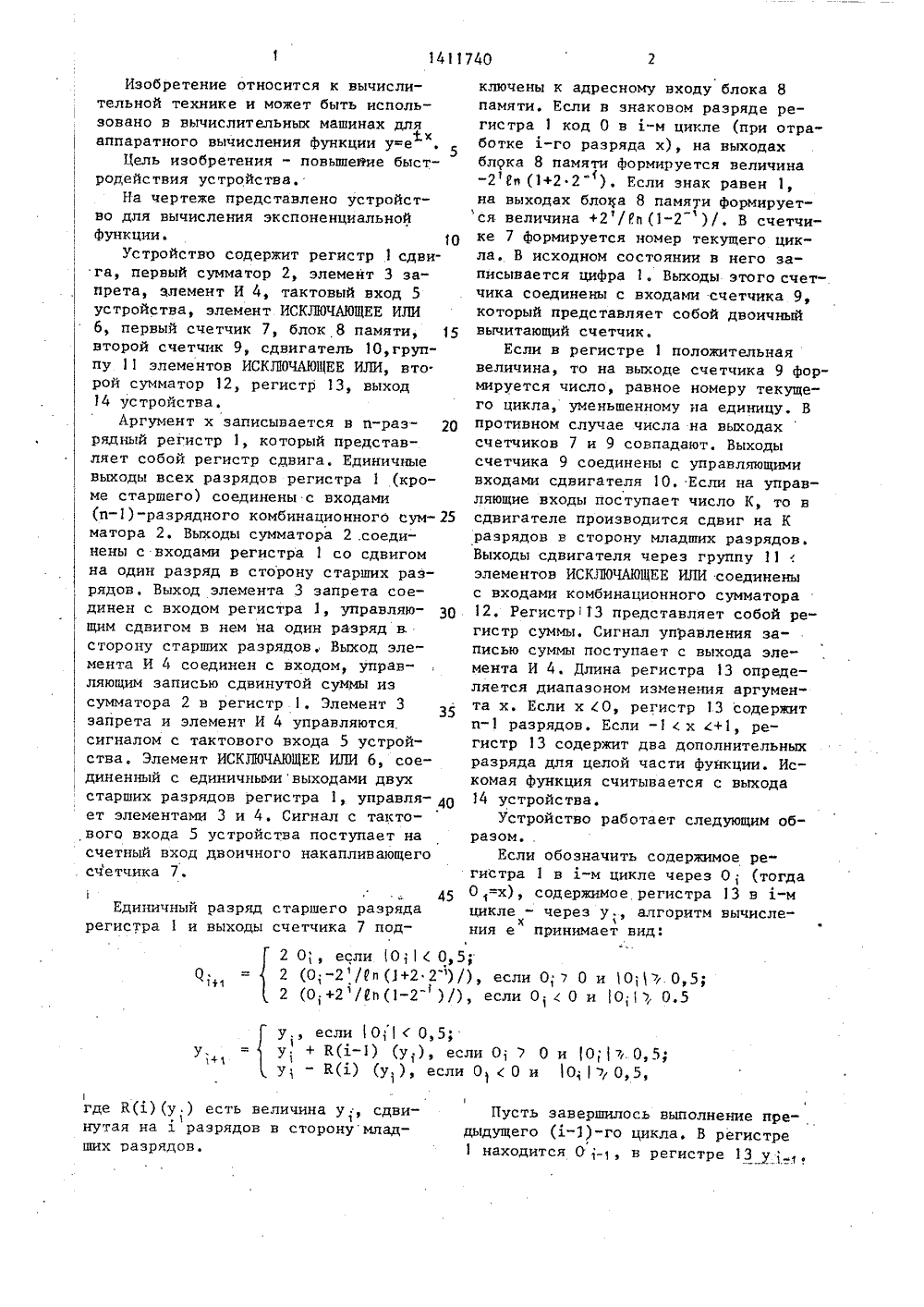

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК ЯО 1411740 4606 ОПИСАНИЕ ИЗОБРЕТЕНИЯ ВТО ОМУ СВИДЕТЕЛЬСТВ(21) (22) (46) (71) ах скин обков 53) 56) 11 А(54) УСТРОЙСТВО ДЛЯ НЕНЦИАЛЬНОЙ ФУНКЦИИ (57) Изобретение от лительной технике и ЫЧИСЛЕНИЯ ЭКСПО сится к вычисожет быть ис- . л ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ 4067827/24-2415.05,8623,07,88, Бюл. 9 27Таганрогский радиотехтут им.В,Д.КалмыковаВ.Е.Золотовский, Р.В..86. пользовано в вычислительных машиндля аппаратного вычисления функцииу = е , Целью изобретения являетсяповышение быстродействия устройстваВ состав устройства входят регистрсдвига, первый сумматор 2, элементзапрета 3, элемент И 4, элемент ИСКД 0 ЧАЮЩЕЕ ИЛИ 6, первый счетчик 7,блок памяти 8, второй счетчик 9,сдвигатель 10, группа элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 11, второй сумматори регистр 13. Повышение быстродействия устройства достигается за счетвведения первого и второго сумматоров, блока памяти, сдвигателя, группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и их оригиналных связей.и1411740 ключены к адресному входу блока 8 памяти. Если в знаковом разряде регистра 1 код 0 в 1-м цикле (при отработке 1-го разряда х), на выходах блдка 8 памяти формируется величина -21 о (1+22 ), Если знак равен на выходах блока 8 памяти формируется величина +2/1 п (1-2 ) /. В счетчике 7 Формируется номер текущего цикла. В исходном состоянии в него записывается цифра 1, Выходы этого счетчика соединены с входами счетчика 9, который представляет собой двоичный вычитающий счетчик.Если в регистре 1 положительная величина, то на выходе счетчика 9 Формируется число, равное номеру текущего цикла, уменьшенному на единицу. В противном случае числа на выходах счетчиков 7 и 9 совпадают. Выходы счетчика 9 соединены с управляющими входами сдвигателя 10, Если на управляющие входы поступает число К, то в сдвигателе производится сдвиг на К разрядов в сторону младших разрядов. Выходы сдвигателя через группу 11 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены с входами комбинационного сумматора 12, Регистр 13 представляет собой регистр суммы. Сигнал управления записью суммы поступает с выхода элемента И 4. Длина регистра 13 определяется диапазоном изменения аргумента х. Если х (О, регистр 13 содержит празрядов. Если -1 с х с+1, регистр 13 содержит два дополнительных разряда для целой части функции. Искомая функция считывается с выхода 14 устройства.Устройство работает следующим образомЕсли обозначить содержимое ре" гистра 1 в 1.-м цикле через 0(тогда 0 =х), содержимое регистра 13 в 1-м цикле - через у., алгоритм вычислехния е принимает вид:1), если 0; 7 0 и О; Ъ. 05;если 0; ( 0 и О; ), 0,5 2 0;, если (01 ( 0,5- 2 (О;"2/О (1+2 2 )/ 2 (О,+2/Ко(1-2 )/) у., если О,0,5;У; + В(1-1) (у;), если 0; ) 0 и О;ъ. 0,5; У, 10) (у), если 01 с 0 и О 7 0,5,уИзобретение относится к вычислительной технике и может быть использовано в вычислительных машинах дляаппаратного вычисления функции уе1 хЦель изобретения - повышение быстродействия устройстваНа чертеже представлено устройство для вычисления экспоненциальнойФункции. 10Устройство содержит регистр 1 сдвига, первый сумматор 2, элемент 3 запрета, элемент И 4, тактовый вход 5устройства, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ6, первый счетчик 7, блок 8 памяти, 15второй счетчик 9, сдвигатель 10,группу 1 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, второй сумматор 12, регистр 13, выход14 устройства.Аргумент х записывается в и-разрядный регистр 1, который представляет собой регистр сдвига. Единичныевыходы всех разрядов регистра 1 (кроме старшего) соединены с входами(п)-разрядного комбинационного сумматора 2. Выходы сумматора 2 .соединены с входами регистра 1 со сдвигомна один разряд в сторону старших разрядов, Выход элемента 3 запрета соединен с входом регистра 1, управляю щнм сдвигом в нем на один разряд всторону старших разрядов, Выход элемента И 4 соединен с входом, управляющим записью сдвинутой суммы изсумматора 2 в регистр 1. Элемент 3запрета и элемент И 4 управляются,сигналом с тактового входа 5 устройства, Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 6, сое-диненный с единичнымивыходами двухстарших разрядов регистра 1, управля ет элементами 3 и 4. Сигнал с тактового входа 5 устройства поступает на счетный вход двоичного накапливающего . счетчика 7. 45Единичный разряд старшего разрядарегистра 1 и выходы счетчика 7 подгде К (1) (у . ) есть величина у, сдвинутая на 1 разрядов в сторонумладших разрядовПусть завершилось выполнение предыдущего (х)-го цикла, В регистре 1 находится О -1, в регистре 13 у;740 Составитель А.ШуляповТехред М.Ходанич Корректор Л.Пилипенко Редактор В,Петраш Заказ 3655/44 Тираж 704 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская наб., д, 4/5Производственно-полиграфическое предприятие, г. Ужгород, ул. 1 роектная, 4 3 1411Пусть 10;, 1О, 5 и 0;, ) О, Из блока 8 памяти вызывается величина-2 и (1+2 2- ) . В сумматоре 2 формируется разнесть 0;-21 и(1+2 2 ),в сумматоре 12 - суммау 1=у;+ К(1-1)(у).По затухании переходных процессовподается сигнал С на вход 5. В регистр 1 записывается удвоенное,значение разности 0;-2 9 п(1+2.2 ), врегистр 13 " суммау;.+ К(1-1) (у, ).Если 0; (О, цикл выполняется аналогично но 15О; =О;, +2 / Р(1-2 ) /,-Е (у 1 )ЕслиО; 1О, 5, сигнал С не проходит на вход управления записью регистров 1 и 13, но проходит на вход 20управления сдвигом регистра 1. Получают01 = 2 01,Одновременно по сигналу С содержимое 25счетчика 7 номера цикла увеличивается на единицу. Формула изобретения30Устройство для вычисления экспо- . ненциальной функции, содержащее регистр сдвига, регистр, первый и второй счетчики, элемент запрета и элемент И, выход элемента запрета соединен с входом сдвига регистра сдвига, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, в него введены первый и второй сумматоры, блок памяти, сдвига тель, группа элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, причем тактовый вход устройства соединен с первыми входами элемента запрета и элемента И и со счетным входомпервого счетчика, прямой выход и-горазряда регистра сдвига (где и - количество разрядов регистра сдвига)соединен с первым входом элементаИСКЛЮЧАЮЩЕЕ ИЛИ, входом старшего разряда адреса блока памяти, с первымивходами элементов ИСКЛЮЧАЮЩЕЕ ИЛИгруппы и первым входом первого сумматора, инверсный выход и-го разря- .да регистра сдвига соединен с управляюпщм входом второго счетчика, выход которого соединен с управляющимвходом сдвигателя, выходы которогосоединены с вторыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы, выход которой соединен с вторым входом первого сумматора, выход которого соединен с информационным входом регистра,выход которого соединен с вторым входом второго сумматора и с информационным входом сдвигателя и являетсявыходом функции устройства, выход(и)-го разряда регистра сдвига соединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединенс вторыми входами элемента запрета вэлемента И, выходы первого счетчикасоединены с входами младших разрядог,адреса блока памяти и информационны-:ми входами второго счетчика, выходэлемента И соединен с входами записирегистра сдвига и регистра, с первого по (и)-й разрядные выходы регистра сдвига соединены с первымивходами второго сумматора, выходы которого соединены с второго по и-йразрядными входами регистра сдвига,информационный выход блока памяти соединен с вторым входом второго сумматора.

СмотретьЗаявка

4067827, 15.05.1986

ТАГАНРОГСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. В. Д. КАЛМЫКОВА

ЗОЛОТОВСКИЙ ВИКТОР ЕВДОКИМОВИЧ, КОРОБКОВ РОАЛЬД ВАЛЕНТИНОВИЧ, ГУЗИК ВЯЧЕСЛАВ ФИЛИППОВИЧ

МПК / Метки

МПК: G06F 7/556

Метки: вычисления, функции, экспоненциальной

Опубликовано: 23.07.1988

Код ссылки

<a href="https://patents.su/3-1411740-ustrojjstvo-dlya-vychisleniya-ehksponencialnojj-funkcii.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления экспоненциальной функции</a>

Предыдущий патент: Синусно-косинусный преобразователь

Следующий патент: Устройство для умножения чисел в модулярной системе счисления с плавающей запятой

Случайный патент: Матричный коммутатор