Устройство для вычисления функции 1-х

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1420600

Авторы: Золотовский, Коробков

Текст

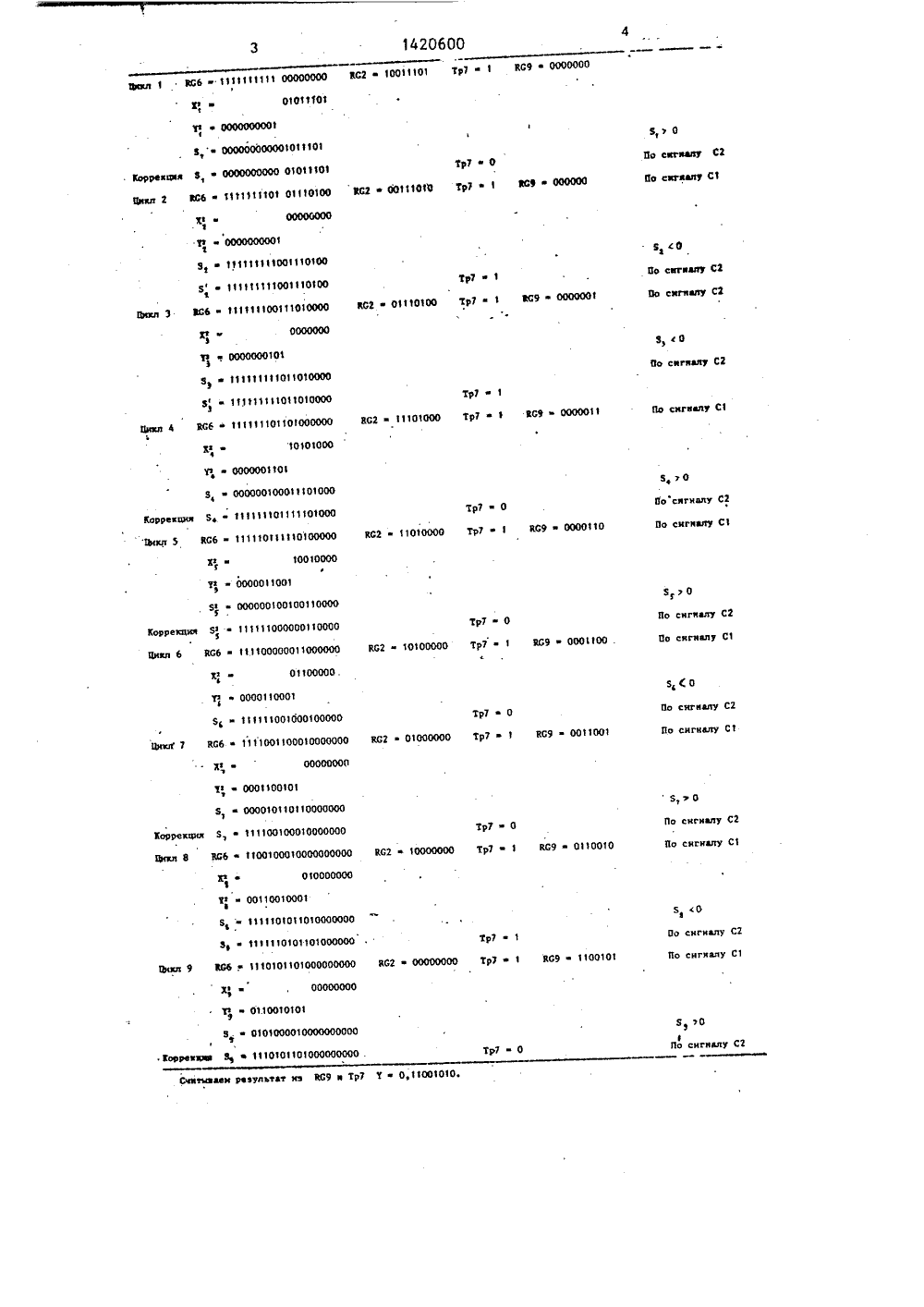

(см. таблицу). 2Изобретение относится к вычисли- тригге 7 (ггера (младший разряд) и выхотельной технике и может быть исполь- дов 13 регистра 9 (старшие разряды) .эовано в вычислительных машинах для При необходимо ходимости с выхода 12 можетаппаратного вычисления функции т 1 Г -Х . быть сыть читан последовательный код реЦелью изобретения является упроще- зультата,ние устройства. Устройство работает следующим обНа чертеже приведена схема устрой- разом,ства. Перед началом вычислений в реУстройство содержит: вход 1 аргу гистр 2 записьывается аргумент Х, тригмента, регистр 2 аргумента, вход 3 гер 7 сброшен в состояние 1 , в ре 11 11сдвига , первую группу элементов И 4 , гистр 6 записывается к о 1 1 1 . . . 1 1 О О . .сумматор 5 , буфер ный регистр 6 , триг ( в младшихге 7 вхо 8адших разрядах записываются1гер, вход 8 синхронизации, регистр нули в остальньтальных единицы). Вычисле 9 результата, вторую группу элемен ние одного ра ф Утов И 10 вхозряда функции произвотов И , вход 11 логического нуля, дится за один цикл. Тл. ак как все цикоды , результата, лы аналогичны огранограничимся рассмотАргумент Х с входа 1 устройства рением некотороторого д-го цикла.записывается в регистр 2 аргумента,Регистр 2 представляет собой обычный 20 Цикл начинается с подачи сигналаи-разрядный регистр сдвига влево, Уп- С 1 на вход 3 Пвход , о этому сигналу ранееравление сдвигом осуществляется сиг- вычисленные р азряды в регистре 9Уналом, поступающим на вход 3 устрой- сдвигаются влев Вво. младшии разрядчства. Выходы регистра 2 через первую регистра 9 записывается (-1)-й раз- .группу элементов И 4 соединены с вхо ряд У. Триггер 7 переходит в состоядами сумматора 5 буферного регистра б, ние "1". Одновременно в регистре 2Триггер 7 представляет собой обычный происходит сдвиг аргумента Х. В реР -тригге . Его вхо Я гистр 6 записывается предыдущая сумчвходом .3 сдвига устроиства, вход С ма Я,.-1 из сумматора со сдвигом насинхронизации соединен с входом 8 30 2 разряда в сторону старших разрядов.устройства инфо ма онныйР ци вход Р По завершении сдвига на выходах групсоединен с выходом знакового разряда пы элементов И 4 формируется частичсумматора 5. Единичный выход тригге- ный квадра Х.т ., на выходах группыра 7 соединен с вхо ом с(и+4)-м аз я ом) вр р д ), входом регистра 9 5 квадрат 712, которые поступают в сум-.чи входами второи группы элементов И матор 5, где формируется сумма Я10. Регист 91собой обычныйр результата представляет По завершении суммировани 8я на входсо о о ычный регистр сдвига влево. поступает сигнал С 2, Если сумма Я;правление сдвигом осуществляется по отрицательна сьна, состояние триггера 7входу 3 устройства, При сдвиге код и 40 не меняется. Если Я 7 у О, триггер 7из триггера 7 записывается в (и)-й переходит в состояние "0" и У = О,Разряд регистра 9. Выходы регистра 9 По затухании переходных процессовчерез вторую группу элементов И 10 цикл завершен, Внбвь подается сигналсоединены с входами 4, 5.(и+2)- С 1, и выполняется следующий цикл.го разр дов сум атора 5 На нулевой 45 Нетрудно заметить что устройствовход устройства 11 постоянно посту 11выполнено таким бпает сигм о разом, что поддерсигнал0 . Сумматор 5 представ- живается равенстволяет собой обычный (2 п+2)-разрядный Х 2 + Р - 1 = О,параллельный комбинационный сумматор. Текущий разряд функции У формируетсяРегистр б представляет собой обычный в триггере 7 и с его выхо50о выхода поступап )-разрядный регистр суммы. Уп- ет на выход 12 и в регистр 9. Поравление записью суммы в него произ- окончании п+1 цикла с выходов 12, 13водится по вхо 3 Вь о5 соеду . и ды сумматора может быть считая параллельный1динены с входами регистра б с11р езультатй кода.перекосом на 2 разряда, благодарячему осуществляется сдвиг суммы на . 552 разряда в сторону старших разрядов.По завершении вычислений искомаяфункция У считывается с выхода 121420600 Цикл 1 ВС 6 ф 111131111 00000000 ЛС 2 ф 10031101 ТР 7 ф 1 ВС 90000000 Хг00301 0000000001 51 т 0 5ООООООООООО 1 О 11 О По сигналу Сг По сигналу С тр 7О Хорракгрга 5,ОООООООООО ОО 1 О 1Цикл 2 ВСЬ11131101 0110100 ВС 2001110 Ь Тр 71 Хг Ха сО По сигналу С 2 По сигналу С 2 5 со По сигналу С 2 По сигналу С 1 1001000 Хг ю 5+ го Посигналу С 2 По сигналу С 1 Хг01100000 . Тг0000110001 51 С О 5 в 111003000100000 тр 7- О По сигналу Сг По сигналу С 1 Цеиг 7 ЯС 611100110000000000 ЯС 201000000 Тр 71 ЯС 9 0011001 Х 1 е 1Оо сигналу Сг По сигналу С 1 ВС 9110010 Х а Э00000000 Тг е 01.10030105010000010000000000 5 гоПо сигналу Сг й н 1110101103000000000 ТР 1 ф 0 Считнмаан Реэулътат нз ВС 9 н ТР 7 ТО, 1001010. Тг н 0000000001151311111 10011101005 а 111111111001110100когкл 9 ВС 6111111100111010000 Тг и 00000003051111111011010000 5 1113113 1011010000 Цикл 6 ВСЬ111111301103000000 Мг000000110150000001000 1101000 Хоррекцин 51 11111101111101000 Цикл 5 ВС 61111 О 33130100000 Тг 0001001015000010110110000000 Хоррекцня 51311100300010000000 0100000000011001000111 1101011010000000 Тр 7 1 ЛС 2 ф 01110100 Тр 11 ВС 9 в 00000015 1420600 6Ф о р м у л и и з о б р е т е н и я тата выхо ы элеме Составитель В,СычевТехред М.Ходанич Корректор М,Васильева Редактор М.Циткина Заказ 4331/54 Тираж 704 ПодписноеВНИИПИ Государственного комитета СССРпо делам изобретений и открытий113035, Москва, Ж, Раушская наб., д. 4/5э Производственно-полиграфическое прецприятие, г, Ужгород, ул. Проектная, 4 Устройство для вычисления функции П - Х, содержащее регистры аргуменб та, результата, сумиатор, буферный регистр, две группы элементов И, триггер, причем входы сдвига всех регистров и вход установки триггера подключены к входу сдвига устройства, 10 информационный вход регистра аргумента подключен к входу аргумента устройства, выходы разрядов регистра результата и выход триггера образуют выход результата устройства, вход синхронизации триггера является входом синхронизации устройства, прямой выход первого старшего разряда регистра аргумента подключен к первым входам элементов И первой группы, ин О версный выход второго разряда регистра аргумента подключен к второму входу второго элемента И первой группы, прямые выходы с второго по и-й разрядов регистра аргумента подключены к 2 б вторым входам первого и с третьего по п-й элементов И первой группы соответственно, выход триггера подключен к вторым входам элементов И второй группы и к последовательному ин- ;О формационному входу регистра резульд нтов И второй группы соединены с входами с четвертогопо (и+2)-й разрядов первого слагаемого сумматора, вход второго слагаемогокоторого подключен к выходу буферногорегистра, а выходы с третьего по(2 п+2)-й разрядов сумматора подключенк информационным входам с первого по2 п-й разрядов буферного регистра,о т л и ч а ю щ е е с я тем, что, сцелью упрощения устройства, выходы спервого по (и)-й разрядов злеиентовИ первой группы подключены к входаис (и+5)-го по (2 п+2) "й разрядов первого слагаемого суиматора, выходы(и)-го и и-го разрядов элементов Ипервой группы подключены к информационным входам (2 п+1) и (2 п+2)-го разрядов буферного регистра соответственно, выход триггера подключен квходу (и+4)-го разряда первого слагаемого сумматора, первый, второй, третий и (и+3)-й разряды входа первогослагаемого сумматора соединены с входом логического нуля устройства, выход первого разряда сумматора соединен с информационным входои триггера,прямые выходы регистра результатасоединены с первыми входами элементов И второй группы,

СмотретьЗаявка

3982248, 29.11.1985

ТАГАНРОГСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. В. Д. КАЛМЫКОВА

ЗОЛОТОВСКИЙ ВИКТОР ЕВДОКИМОВИЧ, КОРОБКОВ РОАЛЬД ВАЛЕНТИНОВИЧ

МПК / Метки

МПК: G06F 7/552

Метки: вычисления, функции

Опубликовано: 30.08.1988

Код ссылки

<a href="https://patents.su/4-1420600-ustrojjstvo-dlya-vychisleniya-funkcii-1-kh.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления функции 1-х</a>

Предыдущий патент: Цифровой измеритель времени установления цифроаналоговых преобразователей

Следующий патент: Вычислительная система

Случайный патент: Способ получения топливных фракций