Устройство для вычисления систем булевых функций

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

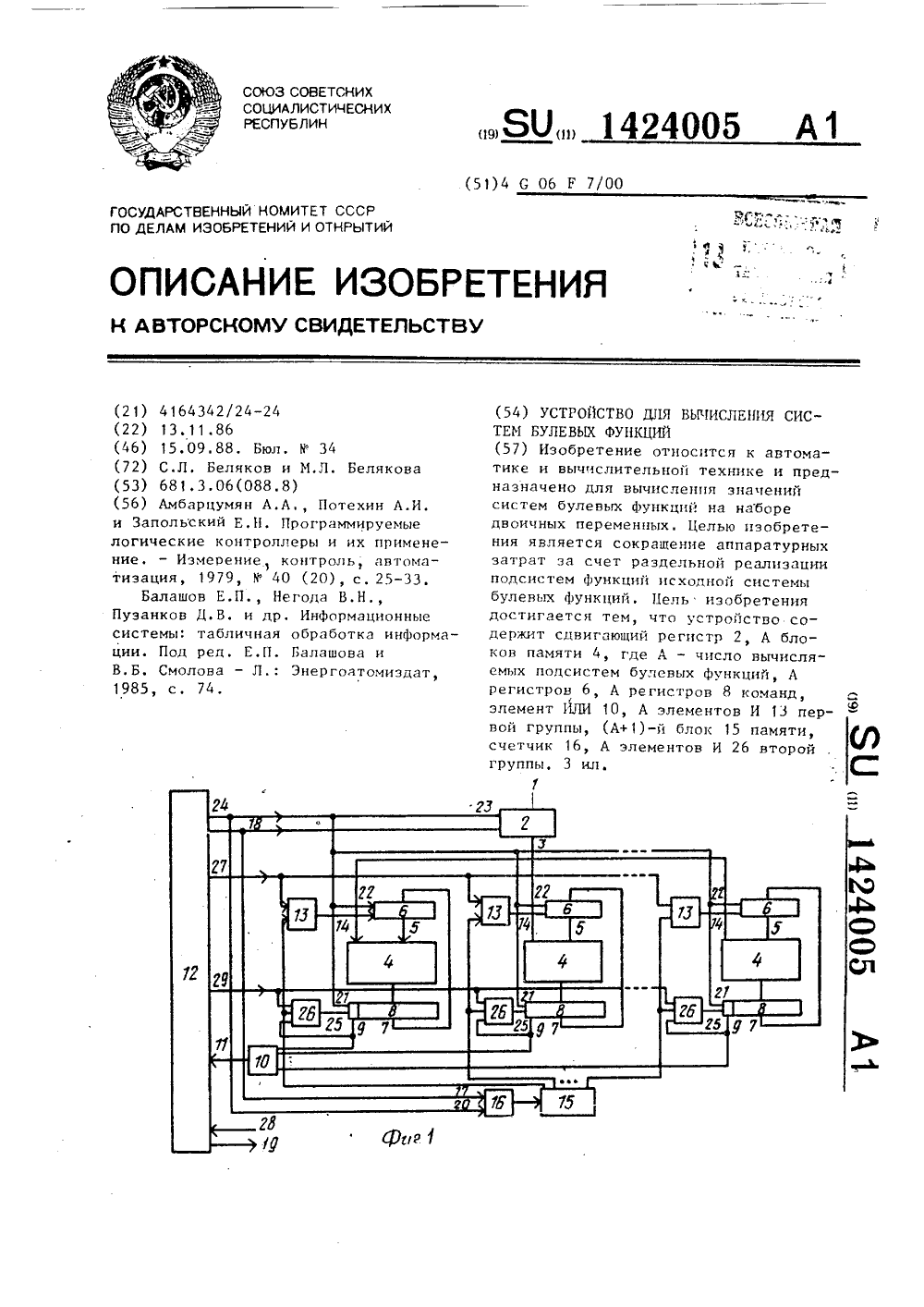

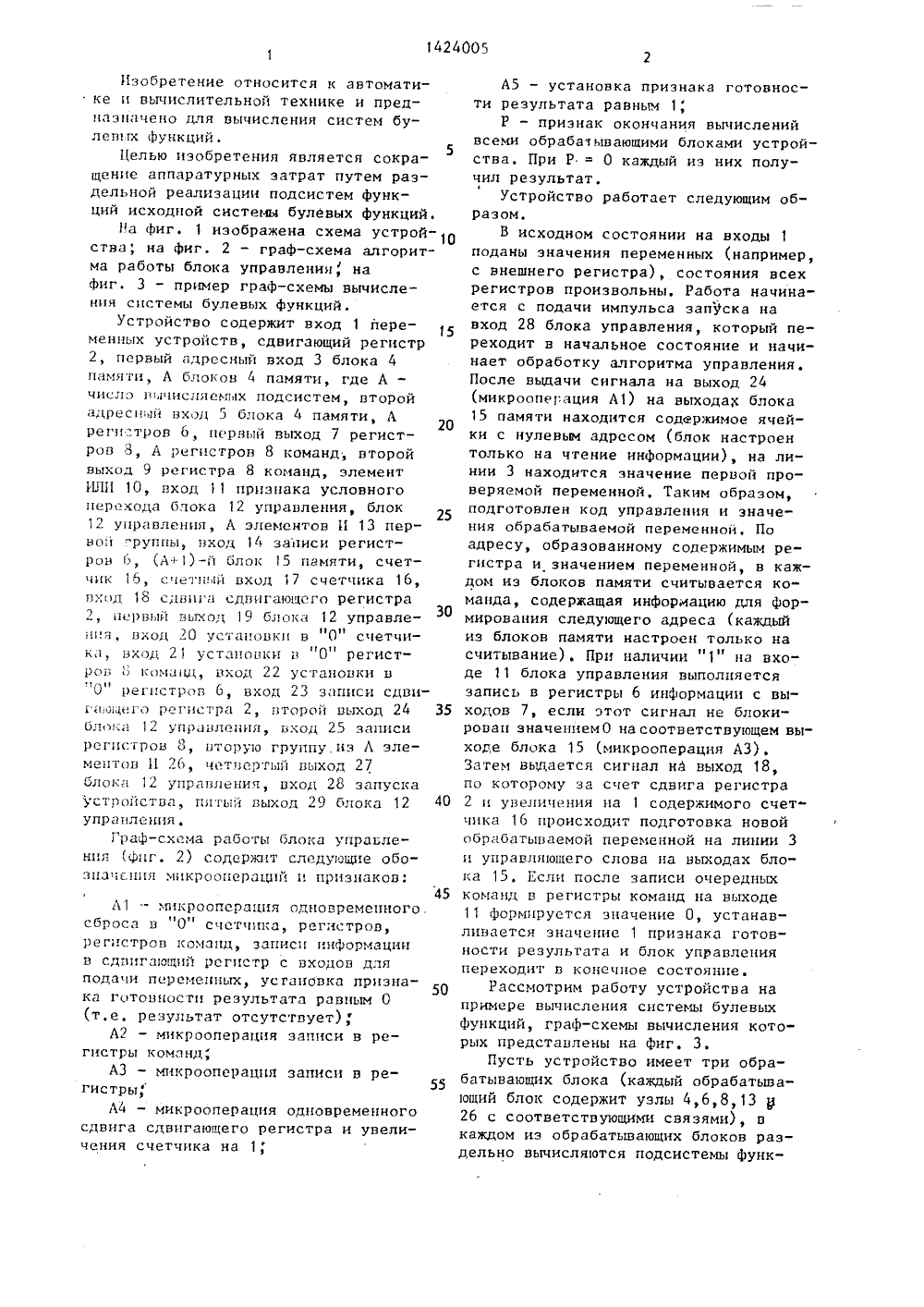

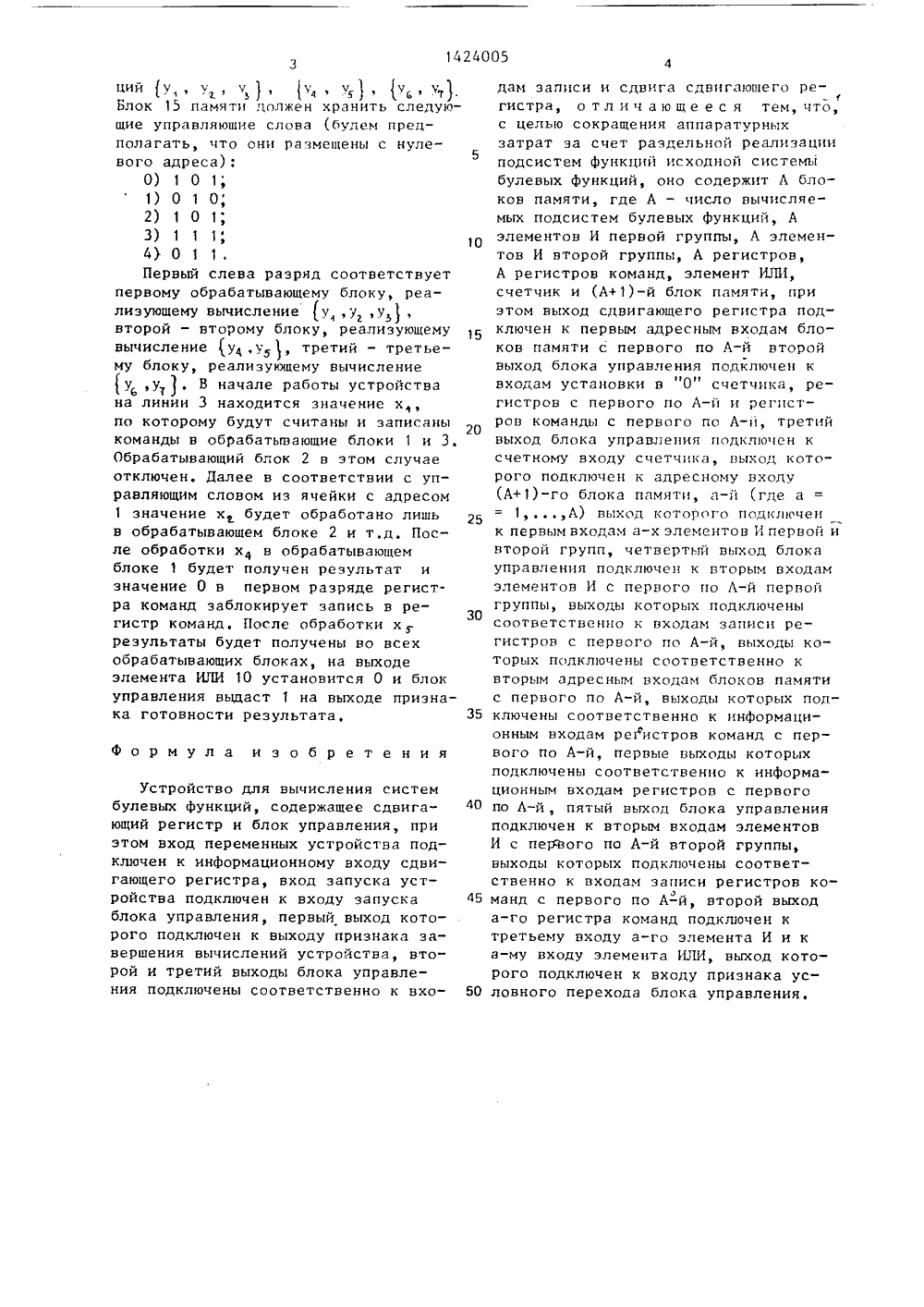

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИ 4 ЕСНРЕСПУБЛИК А 7/00 И СУДАРСТВЕННЫЙ КОМИТЕТ СССРДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИ ОПИСАНИЕ ИЗОБР А ВТОРСНОМУ СВИДЕТЕЛЬСТ(54) УСТРОЙСТВО ДЛЯ ВЬГИСЛЕНЯМИ СИСТЕМ БУЛЕВЫХ ФУНКЦИЙ (57) Изобретение относится к автоматике и вычислительной технике и предназначено для вычисления значений систем булевых функций на наборе двоичных переменных. Целью изобретения является сокращение аппаратурных затрат за счет раздельной реализации подсистем функций исходной системы булевых функций, Цель изобретения достигается тем, что устройство содержит сдвигающий регистр 2, А блоков памяти 4, где А - число вычисляемых подсистем булевых функций, А регистров 6, А регистров 8 команд, с элемент ИЛИ 10, А элементов И 13 первой группы, (А+1)-й блок 15 памяти, счетчик 16, А элементов И 26 второй группы, 3 ил.1Изобретение относится к автоматике ц вычислительной технике и предндэнчено для вычисления систем булевлзх Функций,1 елью изобретения является сокра 5щенце аппаратурных затрат путем раздельной реализации подсистем функций исходной системы булЕвых функций.1 зд Фиг. 1 изображена схема устройствд, на фиг, 2 - граф-схема алгоритма работы блока управлении, нафиг. 3 - пример граф-схемы вычисления системы булевых функций,Устройство содержит вход 1 переменных устройств, сдвигающий регистр2, первый адресный вход 3 блока 4памяти, А блоков 4 памяти, где А -число вычисляемых подсистем, второйадресц зй вход 5 блока 4 памяти, Л20реги=тров 6, цервьзй выход 7 регистров 8, Л регистров 8 команд; второйвыход 9 регистра 8 команд, элементИЛИ 10, вход 11 признака условногоперехода блока 12 управления, блок12 уцрвленця, А элементов И 13 первой руппы, вход 14 записи регистров 6, (Л+1)-й блок 15 памяти, счетчик 16, счетный вход 17 счетчика 16,ззход 18 сдвига сдвцгдющсго Регистра2, первый выход 19 блока 12 управле 30ц,я, вход 20 установки в 0 счетчик, ззхэд 21 устдцовкц в "О" регистров 8 колызд, вход 22 установки в0 регистров 6, вход 23 эпцси сдвига.зщего регистра 2, второй выход 24 35блока 12 управления, вход 25 записирегистров 8, вторую группу цэ Л элементов И 26, четвертый выход 27блок 12 упрззлеция, вход 28 запускаустройств, пятый выход 29 блока 12 40упрдпленця,Граф-схема работы блока упрдьленця 1 фцг. 2) содержит следующие обозцд сцця мцкроопердццй и признаков:45Л 1 - микроопердцця одновременного.сброса в Осчстчцкд, регистров,регистров команд, эдписц информациив сдвцгающцй регистр с входов дляподачи переменных, усгдцовкд пРизнака готовности результата рдвным О(т.е, результат отсутствует);Л 2 - микрооперация записи в регистры комднд,А 3 - микроопе 1)ацця записи в регистры,Л 4 - микрооперация одновременногосдвига сдвигающего регистра и увеличения счетчика на 1; А 5 - установка признака готовности результата равным 1;Р - признак окончания вычислений всеми обрабатывающими блоками устройства, При Р = 0 каждый иэ них получил результат.Устройство работает следующим образом.В исходном состоянии на входы 1 поданы значения переменных (например, с внешнего регистра), состояния всех регистров произвольны, Работа начинается с подачи импульса запуска на вход 28 блока управления, который переходит в начальное состояние и начинает обработку алгоритма управления. После выдачи сигнала на выход 24 (микрооперация Л 1) на выходах блока 15 памяти находится содержимое ячейки с нулевым адресом (блок настроен только на чтение инФормации), на линии 3 находится значение первой проверяемой переменной, Таким образом, подготовлен код управления и значения обрабатываемой переменной. По адресу, образованному содержимым регистра и значением переменной, в каждом из блоков памяти считывается команда, содержащая информацию для Формирования следующего адреса (каждый из блоков памяти настроен только на считывание). При наличии "1" на входе 11 блока управления выполняется запись в регистры 6 информации с выходов 7, если этот сигнал не блокирован эначециемО на соответствующем выходе блока 15 (микрооперация АЗ). Затем выдается сигнал нЛ выход 18, по которому за счет сдвига регистра 2 ц увеличения ца 1 содержимого счетчика 16 происходит подготовка новой обрбатываемой переменной на линии 3 ц управляющего слова на выходах блока 15. Гслц после записи очередных команд в регистры команд на выходе 11 Формцруется значение О, устанавливается значение 1 признака готовности результата и блок управления переходит в конечное состояние,Рассмотрим работу устройства на примере вычисления системы булевых Функций, граФ-схемы вычисления которых представлены на фиг, 3.Пусть устройство имеет три обрабатывающих блока (каждый обрабатывающий блок содержит узлы 4,6,8,13 у 26 с соответствующими связями), в каждом иэ обрабатывающих блоков раздельно вычисляются подсистемы Функ1424005 УУу У оставитель В,Смирнов ехред М,Ходанич тор Л.Пата дактор А.Маковская акаэ 4688/5 Подписно ираж В 1 1 ИИП 4 роектная, 4 изводственно-полиграфическое предприятие,жго по3035,Государственн елам изобрете сква, Ж, Р го комитета СССий и открытийушская наб., д,

СмотретьЗаявка

4164342, 13.11.1986

ФИЛИАЛ "ВОСХОД" МОСКОВСКОГО АВИАЦИОННОГО ИНСТИТУТА ИМ. С. ОРДЖОНИКИДЗЕ

БЕЛЯКОВ СТАНИСЛАВ ЛЕОНИДОВИЧ, БЕЛЯКОВА МАРИНА ЛЕОНТЬЕВНА

МПК / Метки

МПК: G06F 7/00

Метки: булевых, вычисления, систем, функций

Опубликовано: 15.09.1988

Код ссылки

<a href="https://patents.su/4-1424005-ustrojjstvo-dlya-vychisleniya-sistem-bulevykh-funkcijj.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления систем булевых функций</a>

Предыдущий патент: Устройство для ввода информации

Следующий патент: Многофункциональный логический модуль

Случайный патент: Приспособление к деревообрабатывающим станкам для безразметочной обработки деталей