Устройство для вычисления функции вида f( )=

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1418709

Автор: Кашалов

Текст

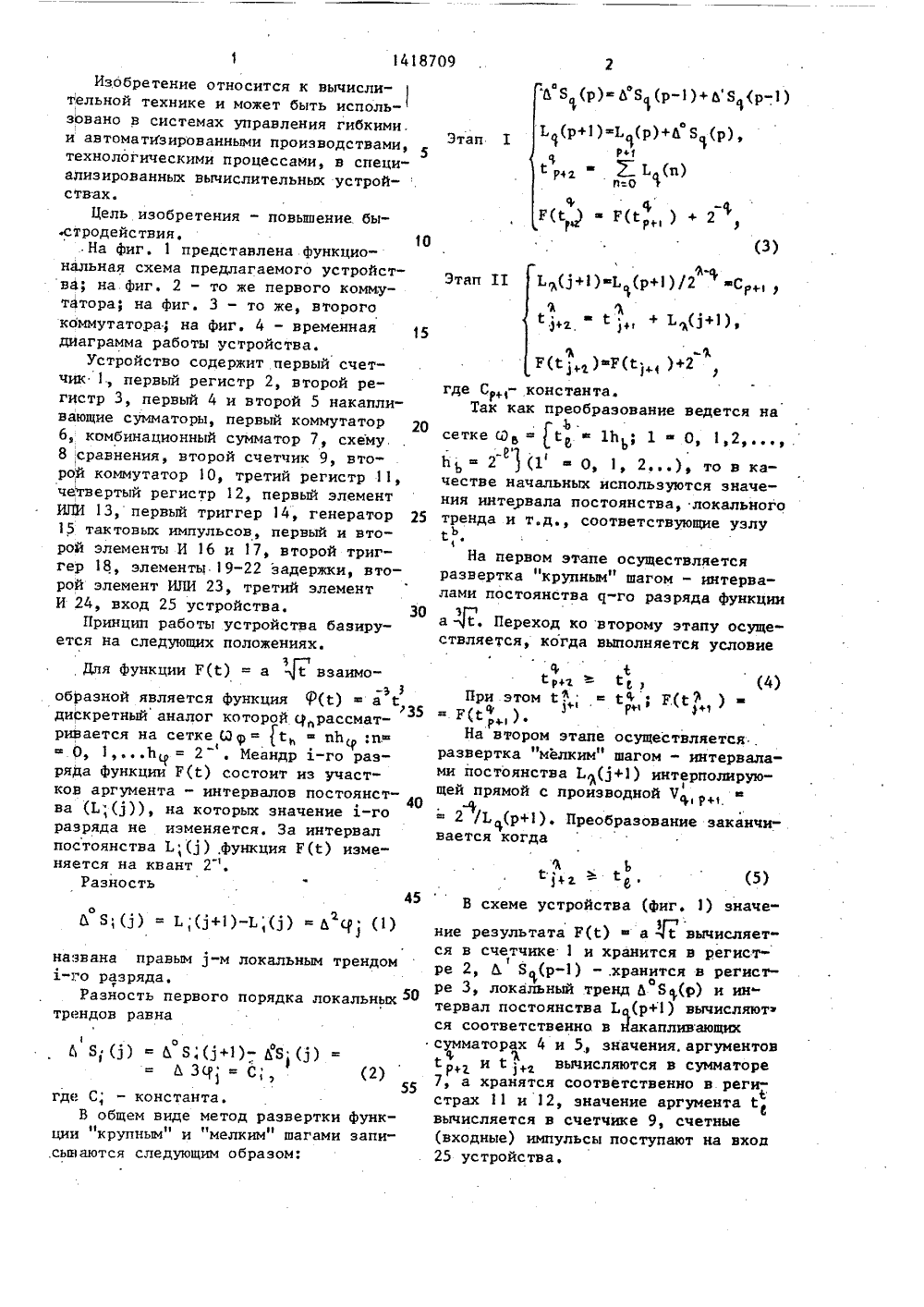

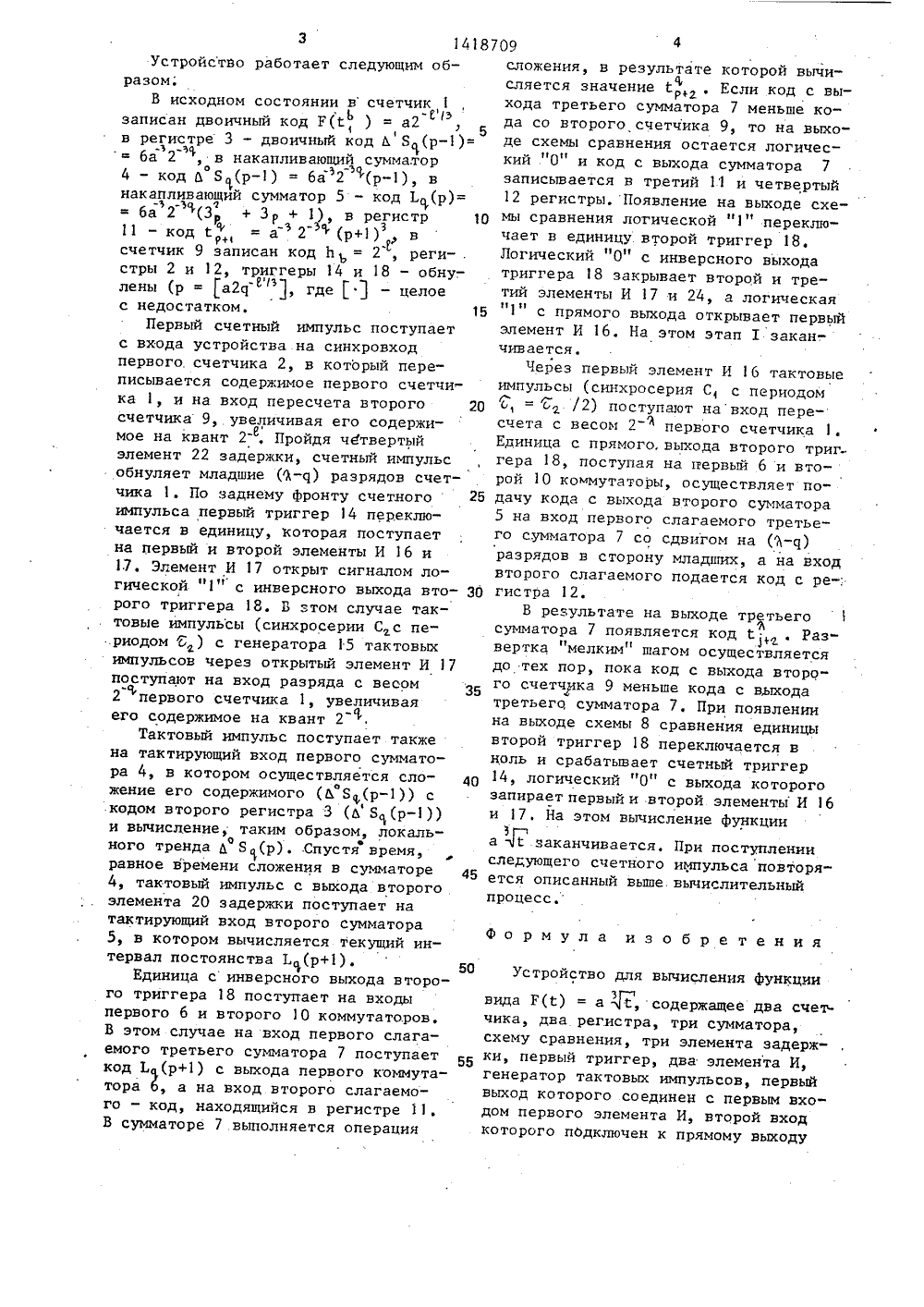

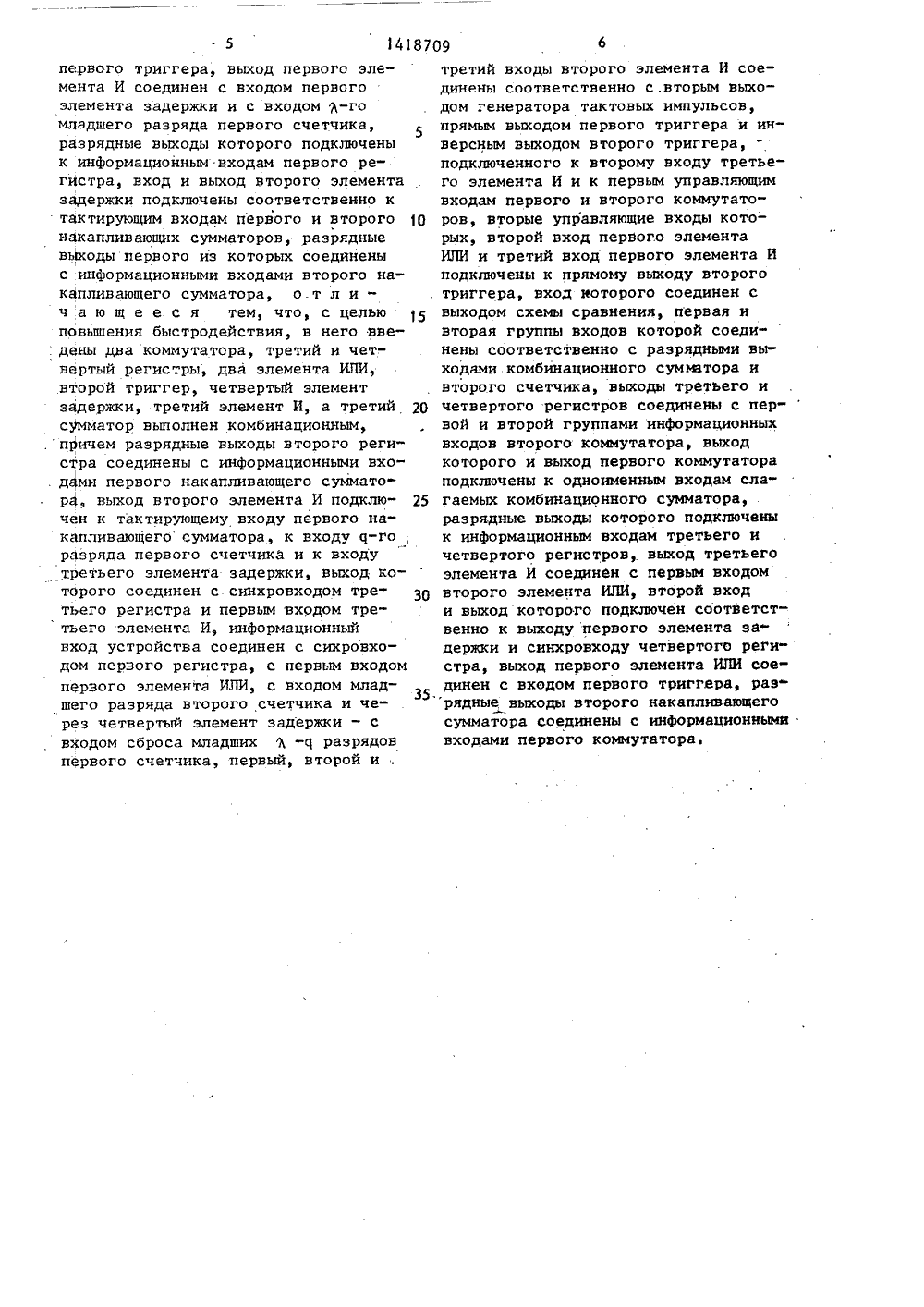

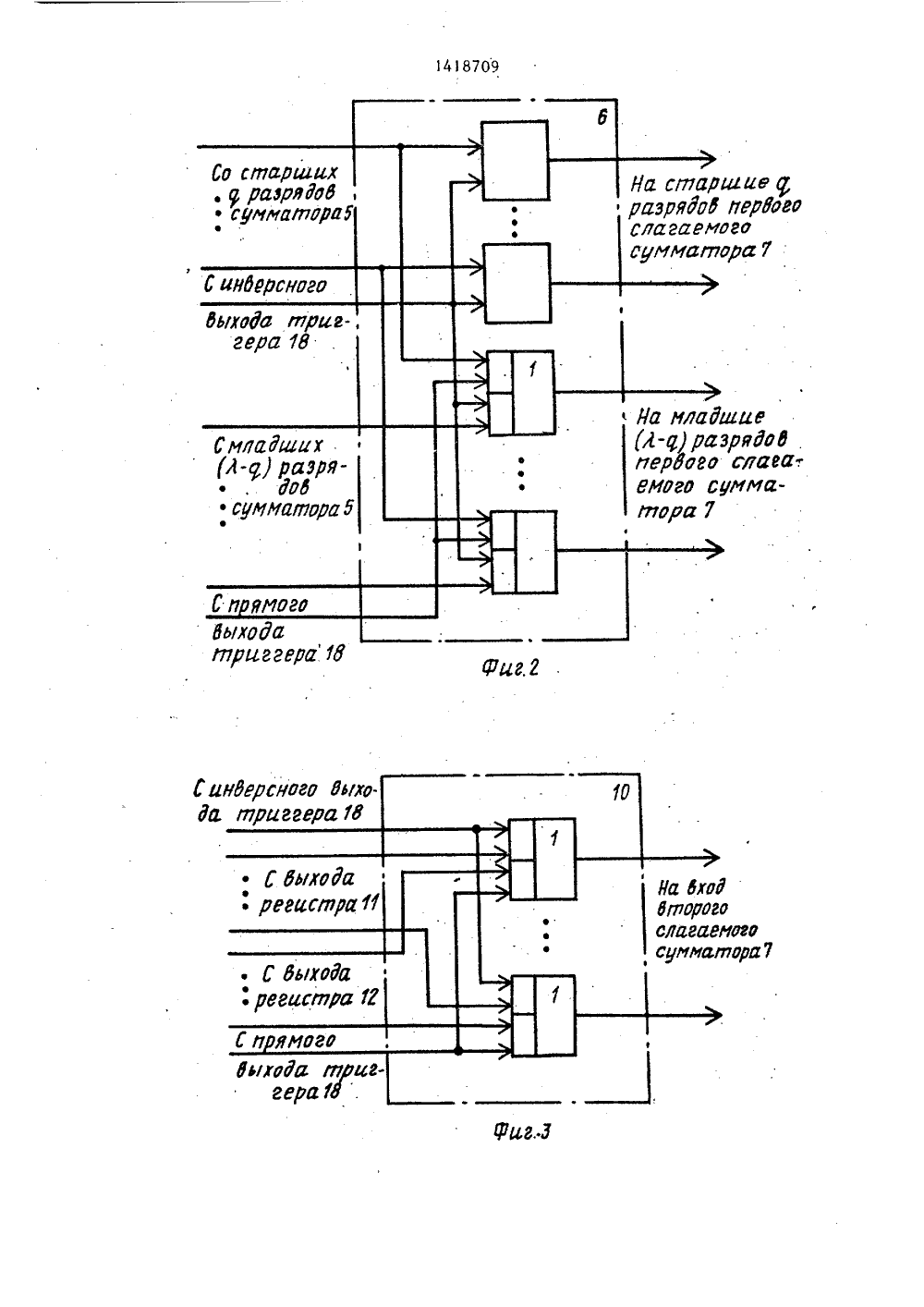

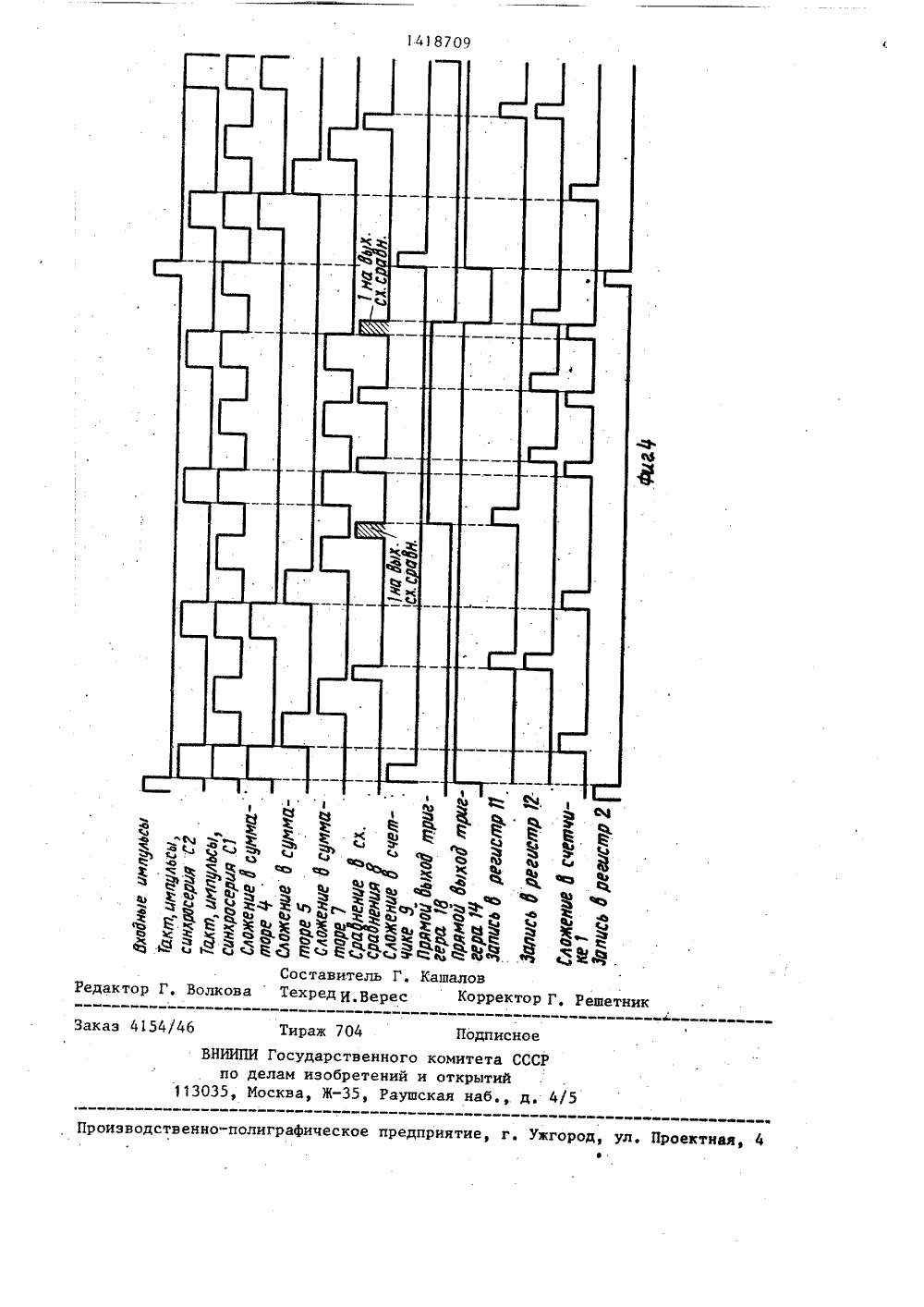

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИН 19) (11) 1)4 СО ЪСаС.1 Р"-11, А Я45 ПИСАНИЕ ИЭОБРЕТЕНИВТОРСКОМУ СВИДЕТЕЛЬСТВУ 1 тг, г ггЬ оерым" ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ(71) Гомельский конструкторско-техно-логический и экспериментальный институт по техническому перевооружению и подготовке производства(56) Авторское свидетельство СССР У 949654, кл. С 06 Р 7/552, 1982.Авторское свидетельство СССР 11 г 1129609, кл, С 06 Р 7/552, 1984. (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИИ ВИДА Р = а 1 г.(57) Изобретение относится к вычисли тельной технике и может быть использовано в системах управления гибкими автоматизированными производствами, технологическими процессами в специализированных вычислительных устройствах. Цель изобретения - повышение быстродействия. Изобретение позволяет в несколько десятков раз повыситьскорость извлечения корня третьей степени и реализует умножение резуль тата на вещественный коэффициент, Повышение скорости преобразования достигается за счет декомпозиции алг ритма развертки на два этапа. На п вом этапе развертка ведется "крупн шагом в некотором "среднем" о-м разряде и приращение функции осуществляется квантами 2 1; На втором этапе ведется развертка "мелким" шагом в младшем 9 -м разряде, а приращение-а функции реализуется квантами 2 . Для достижения поставленной цели в устрои ство введены два коммутатора 6 и 10, третий 11 и четвертый 12 регистры, два элемента ИЛИ 13 и 23, второй триг гер 18, четвертый элемент 22 задерж- ки, третий элемент И 24. Дополнительно введенное оборудование позволяет осуществить переход к развертке "мелким" шагом путем сдвига в первом коммутаторе 6 значения длины интервала постоянства на (3-Ч) разрядов в сторону младших, После вычисления текущего значения функции Р(1) = а реализуется возврат к развертке "круп ным" шагом. 4 ил.Разность45 Ь 8,(д) = Ь;(З+1)-Ь;(д) - ЬсР(1) названа правым 1-м локальным трендом ь.-го разряда.разность первого порядка локальных 50 трендов равна Ь 8; - Ь 8;(З+1)- Ь 8;(1)- ЬЗЯ = С1 (где С; - константа.В общем виде метод развертки функции "крупным" и "мелким" шагами запи.сьд)аются следующим образом:(2)55 Изобретение относится к вычислительной технике и может быть исполь- зовано в системах управления гибкими. и автоматизированными производствами5 технологическими процессами, в специализированных вычислительных устрой-ствах.Цель изобретения - повышение быстродействия. 10На фиг1 представлена функциональная схема предлагаемого устройства; на фиг. 2 - то же первого коммутатора; на фиг. 3 - то же, второго кбммутатора, на фиг. 4 - временная диаграмма работы устройства.Устройство содержит первый счетчик 1, первый регистр 2, второй регистр 3, первый 4 и второй 5 накапливающие сумматоры, первый коммутатор 20 6, комбинационный сумматор 7, схему 8 сравнения, второй счетчик 9, второй коммутатор 10, третий регистр 11, четвертый регистр 12, первый элемент ИЛИ 13, первый триггер 14, генератор 25 15 тактовых импульсов, первый и второй элементы И 16 и 7, второй триггер 18, элементы 19-22 задержки, второй элемент ИЛИ 23, третий элемент И 24, вход 25 устройства. 30Принцип работы устройства базируется на следующих положениях.г-(, Для функции Р(й) = а 1 й взаимо-Ъ 3 образной является функция Р(й)а35 дискретный аналог которой срассматривается на сетке И= С щ пЬ .пщО, 1,Ь( = 2 . Меандр д-го разряда функции Р(1) состоит из участков аргумента - интервалов постоянст 40 ва (Ь"3, на которых значение 3.-го разряда не изменяется. За интервал постоянства Ь;( ),функция Р(й) изменяется на квант 2 .(3) Ф-(Ь Д+1) Ь (р+ ) /2 С +(ъ %с;- е;+ Ь 43+1)е Этап П Р(.(.с) Р(Е;)+2где С+,- константа.Так как преобразование ведется на.ъсетке Яь " СЕ 1 Ь(о, 1 О, 1,2 . Ь 2 )(1 щО, 1, 2), товкачестве начальных используются значения интервала постоянства, локального тренда и т.д., соответствующие узлуь(На первом этапе осуществляется развертка "крупным" шагом - интервалами постоянства с 1-го разряда функциизГа -ЧС. Переход ко второму этапу осуществляется, когда выполняется условие( - фС 1 (4)При этом й 1( = е(1 Р(Е T )Рн ф1+(фНа втором этапе осуществляется, развертка "мелким" шагом - интервалами постоянства Ь(1+1) интерполирующей прямой с производной Ч(+(Фф: 2 /Ь (р+1). Преобразование заканчивается когда Ь"Р - ЕВ схеме устройства (фиг. 1) значение результата Р(С) щ а 1 й вычисляет 3 Гся в счетчике 1 и хранится в регистре 2, й Б (р) - .хранится в регисторе 3, локальный тренд а Я(1,(р) и ин тервал постоянства Ь( (р+1) вычисляютф ся соответственна в накапливающих сумматорах 4 и 5, значения, аргументов С+( и 11+с вычисляются в сумматоре 7, а хранятся соответственно в регистрах 11 и 12, значение аргумента йЕ вычисляется в счетчике 9, счетные(входные) импульсы поступают на вход 25 устройства.3 14187Устройство работает следующим образом;В исходном состоянии в счетчик 1 записан двоичный код р( ) = а 2 в регистре 3 - двоичный код Ь Я(р)=-3 -Ъба 2 1, в накапливающий сумматор 4 - код 6 Я(р) = ба 2 (р-), в накапливающйй сумматор 5 - код(р)= = ба 2 Ч(3 + Зр + 1), в регистр 10з -з з счетчик 9 записан код Ь = 2, реги- . стры 2 и 12, триггеры 14 и 18 - обну. - лены (р = а 2 Ч , где- целое с недостатком. 15Первый счетный импульс поступает с входа устройства на синхровход первого. счетчика 2, в который переписывается содержимое первого счетчика 1, и на вход пересчета второго 20 счетчика 9, увеличивая его содержимое на квант 2 , Пройдя четвертый элемент 22 задержки, счетный импульс обнуляет младшие (%-Ч) разрядов счетчика 1. По заднему фронту счетного 25 импульса первый триггер 4 переключается в единицу, которая поступает на первый и второй элементы И 16 и 17. Элемент И 17 открыт сигналом логической "1" с инверсного выхода вто- ЗО рого триггера 18. Б этом случае тактовые импульсы (синхросерии С с пе" .риодом) с генератора 15 тактовых импульсов через открытый элемент И 17 поступают на вход разряда с весом 2 первого счетчика 1, увеличивая его содержимое на квант 2 1.Тактовый импульс поступает также на тактирующий вход первого сумматора 4, в котором осуществляется сло жение его содержимого (Ь Я(рс кодом второго регистра 3 (ь Я 1(ри вычисление, таким образом, локального тренда д Я (р) . Спустя время, равное времени сложения в сумматоре 45 4, тактовый импульс с выхода второго элемента 20 задержки поступает на тактирующий вход второго сумматора 5, в котором вычисляется текуший интервал пос тоянс тв а(Р+1)50Единица с инверсного выхода второго триггера 18 поступает на входы первого 6 и второго 1 О коммутаторов, В этом случае на вход первого слагаемого третьего сумматора 7 поступает код Ь(р+1) с выхода первого коммутатора 6, а на вход второго слагаемого - код, находящийся в регистре 11. В сумматоре 7 выполняется операция 094сложения, в результате которой вычисляется значение 1,Если код с вы%хода третьего сумматора 7 меньше кода со второго счетчика 9, то на выходе схемы сравнения остается логический "О" и код с выхода сумматора 7 записывается в третий 11 и четвертый 12 регистры. Появление на выходе схемы сравнения логической "1" переключает в единицу второй триггер 18.Логический "0" с инверсного выхода триггера 18 закрывает второй и третий элементы И 17 и 24, а логическая "1" с прямого выхода открывает первый элемент И 16. На этом этап 1 закан-. чиваетсяЧерез первый элемент И 16 тактовые импульсы (синхросерия С, с периодом С, = о /2) поступают навход пересчета с весом 2первого счетчика 1. Единица с прямого. выхода второго триггера 18, поступая на первый 6 и второй 10 коммутаторы, осуществляет подачу кода с выхода второго сумматора 5 на вход первого слагаемого третьего сумматора 7 со сдвигом на (-с) разрядов в сторону младших, а на вход второго слагаемого подается код с ре-: гистра 12.В результате на выходе третьегоасумматора 7 появляется код с, . Развертка "мелким" шагом осуществляется до тех пор, пока код с выхода второго счетчрка 9 меньше кода с выхода третьего сумматора 7, При появлении на выходе схемы 8 сравнения единицы второй триггер 18 переключается в ноль и срабатывает счетный триггер 14, логический "0" с выхода которого запирает первый и второй элементы И 16 и 17. На этом вычисление функции3 Га 1 заканчивается. При поступлении следующего счетного импульса повторяется описанный выше. вычислительный процесс,Формула изобретенияУстройство для вычисления функцчизвида Р(Е) = а ЧЕ, содержащее два счетчика, два регистра, три сумматора, схему сравнения, три элемента задержки, первый триггер, два элемента И, генератор тактовых импульсов, первый выход которого соединен с первым входом первого элемента И, второй вход которого пОдключен к прямому выходу4187 первого триггера, выход первого элемента И соединен с входом первого элемента задержки и с входом 3-го младшего разряда первого счетчика, разрядные выходы которого подключены к информационным входам первого регистра, вход и выход второго элемента задержки подключены соответственно к тактирующим входам первого и второго 10 накапливающих сумматоров, разрядные вЫходы первого из которых соединены с информационными входами второго накапливающего сумматора, о.т л и - ч а ю щ е е. с я тем, что, с целью повышения быстродействия, в него введены два коммутатора, третий и четвертый регистры, два элемента ИЛИ, второй триггер, четвертый элемент задержки, третий элемент И, а третий 20 сумматор выполнен комбинационным, причем разрядные выходы второго регистра соединены с информационными вхо. дами первого накапливающего сумматора, выход второго элемента И подклю чен к тактирующему входу первого на" капливающего сумматора, к входу п-го, разряда первого счетчика и к входу третьего элемента задержки, выход которого соединен с синхровходом третьего регистра и первым входом третьего элемента И, информационный вход устройства соединен с сихровходом первого регистра, с первым входом первого элемента ИЛИ, с входом младшего разрядавторого счетчика и через четвертый элемент задержки - с входом сброса младших-ц разрядов первого счетчика, первый, второй и 09 6третий входы второго элемента И соединены соответственно с.вторым выходом генератора тактовых импульсов, прямым выходом первого триггера и инверсным выходом второго триггера, подключенного к второму входу третьего элемента И и к первым управляющим входам первого и второго коммутаторов, вторые управляющие входы которых, второй вход первого элемента ИПИ и третий вход первого элемента И подключены к прямому выходу второго триггера, вход которого соединен с выходом схемы сравнения, первая и вторая группы входов которой соединены соответственно с разрядными выходами комбинационного сумматора и второго счетчика, выходы третьего и четвертого регистров соединены с первой и второй группами информационных входов второго коммутатора, выход которого и выход первого коммутатора подключены к одноименным входам слагаемых комбинационного сумматора, разрядные выходы которого подключены к информационным входам третьего и четвертого регистров, выход третьего элемента И соединен с первым входом второго элемента ИЛИ, второй вход и выход которого подключен соответственно к выходу первого элемента за держки и синхровходу четвертого реги-стра, выход первого элемента ИЛИ соединен с входом первого триггера, раз "рядные выходы второго накапливакицего сумматора соединены с информационными входами первого коммутатора.1418709 еше актор Г. В Подпися аказ 4154/46 7 Тир ВНИИПИ Госу по делам 035, МоскварственногообретенийЖ, Рауш комитет открыт кая набд. 4/5 графическое предприятие, г. Ужгород, ул,Производственн тная 1 3ффс сц еОа6 Ф:,Од щ Фэ фоэмс ф. о ф ф ф Ю Екф:3 40 сэ Ф сл ,э И с 5 1 6,ь.э ъоСоставитель Гд олкова Техред И.Верес Фф1 % с фЯйэ

СмотретьЗаявка

4180808, 15.01.1987

ГОМЕЛЬСКИЙ КОНСТРУКТОРСКО-ТЕХНОЛОГИЧЕСКИЙ И ЭКСПЕРИМЕНТАЛЬНЫЙ ИНСТИТУТ ПО ТЕХНИЧЕСКОМУ ПЕРЕВООРУЖЕНИЮ И ПОДГОТОВКЕ ПРОИЗВОДСТВА

КАШАЛОВ ГЕОРГИЙ ИВАНОВИЧ

МПК / Метки

МПК: G06F 7/552

Метки: вида, вычисления, функции

Опубликовано: 23.08.1988

Код ссылки

<a href="https://patents.su/6-1418709-ustrojjstvo-dlya-vychisleniya-funkcii-vida-f.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления функции вида f( )=</a>

Предыдущий патент: Устройство для вычисления полинома -й степени

Следующий патент: Устройство программного управления

Случайный патент: Способ получения тетр. аметилендиоксидисульфон метилциклогексклметана