Патенты с меткой «сумматор»

Матричный сумматор

Номер патента: 1545217

Опубликовано: 23.02.1990

МПК: G06F 11/30, G06F 7/50

Метки: матричный, сумматор

...значеНия при сохранении возможности изменения в избыточном коде режима В одНого разряда из числа первого и пято 1 а и двух разрядов из числа второго,третьего, четвертого.В первом режиме В = 00) матричНый сумматор работает следующим образом.При поступлении на входы 1 и 2слагаемых матричного сумматора кодовоперандов Х и У совместно с сигналомпризнака операции на входе 3 кодыоперандов Х и У через коммутаторы 1 Ои 11 поступают на входы группы элементов ИЛИ 14 и группы элементов И15. При этом на выходе результатаузла 20 суммирования Формируется код 45цифры2 = (Х + Т 3 тпос 14,а на выходе переноса узла 20 суммирования - код цифрыО, при (Х + У)(4;Р =1, при (Х+ Т 4 Коды этих чисел соответственно через коммутаторы 22 и 30 поступают на выходы 31...

Оптоэлектронный сумматор

Номер патента: 1548780

Опубликовано: 07.03.1990

Авторы: Имнаишвили, Кобесашвили, Натрошвили

МПК: G06E 1/04

Метки: оптоэлектронный, сумматор

...на второй входоптоэлектронного элемента И 24, открывает его и на выходе появляетсявысокий потенциал, который подаетсяна второй вход десятого элемента КЛК 1016 второй группы, в результате чегообнуляется десятый регенеративныйоптрон 10,После прекращения второго разрешающего сигнала на вход 7 начинаетсявыполнение второго и третьего шаговалгоритма суммирования. В этом случае, если в пятом регенеративномоптроне 10 первого разряда (ячейка1) находится единица, то высокий потенциал подается на входы второгоэлемента 17 задержки и четвертогоэлемента И 14четвертой группы и через элементы ИЛИ 16,-169 второйгруппы обнуляет регенеративные оптроны 10,-10 первого разряда (ячейка1,), При этом, если старшая единицамантиссы суммы...

Разрядно-аналоговый сумматор

Номер патента: 1548797

Опубликовано: 07.03.1990

Авторы: Гильгурт, Новицкий, Пухов, Романцов

МПК: G06G 7/14

Метки: разрядно-аналоговый, сумматор

...2,1-2.3. На первыйвход указанного аналогового сумматора 2,2 с выхода второго аналоговогосумматора 1.2 первой группы аналоговых сумматоров поступает напряжение,равное -(2+4)В.Таким образом, на выходе первогоаналогового сумматора 2.1 второй группы аналоговых сумматоров и соответственно на выходе первого разряда 7,1выходной шины формируется величина,равная (8+5-10)В=З В.На выходе второго аналогового сумматора 2,2 второй группы аналоговыхсумматоров и одновременно на второмразряде 7,2 выходной шины формируетсяуровень, равный (2+4+1) В=7 В, Натретьем разряде 7.3 выходной шины формируется величина, равная (0+0+0)В==0 В,Таким образом, на выходной шине7.1-7,3 устройства получается величина у 1 Оф 3 фО 7+О 0 6П р и м е р 2, Пуст. в некоторый...

Накапливающий сумматор

Номер патента: 1557561

Опубликовано: 15.04.1990

Авторы: Костров, Луканов, Низовой

МПК: G06F 7/50

Метки: накапливающий, сумматор

...Когда код двоичного числа счетчика 3 станет равным коду двоичного числа предварительндй записи,поступающего на блок элементов сравнения 5, тогда с выхода (А=В) блокаэлементов сравнения 5 снимается сигнал "1". Этот сигнал инвертируется. элементом НЕ 6 и поступает на входтриггера 7.Триггер 7 переключается, Прохождение тактовых импульсов через элементИ 8 на счетчик 3 прекращается, таккак с переключением триггера 7 с еговыхода на первый вход элемента И 8поступает напряжение "О",Так перед началом суммированияосуществляется запись счетчик 3 кодазаданного двоичного числа.Далее на вход сумматора 1 поступает код двоичного числа, который складывается с содержимым счетчика 3.Полученная сумма записывается врегистр памяти 2 в момент спада...

Сумматор с последовательным переносом

Номер патента: 1559342

Опубликовано: 23.04.1990

Автор: Сурнин

МПК: G06F 7/50

Метки: переносом, последовательным, сумматор

...21, а также на входе переноса сумматора 21. На входах сумматора 22 значения сигналбв сохраняют55 сл . На выходе 38 суммы сумматора 22 устанавливается значение третьего разряда результата, на выходе переноса сумматора 22 и, соОТВетственно, на выходе переноса сумматора 20 - эначениепереноса по результату сложения всумматоре 22. На первых входах элементов И 5 и 11 устанавливаются единичные сигналы соответственно, черезвторье входы элеменэов ИЛИ 1 и 1 наПЕРВОМ И ВТОРОМ ОСНОВНЫХ ВХОДаХ, СУМматора 20 устанавливаются значения А иВсоот.ветственно,1 акт пятый. На входах сумматора 22и наль 1 (если они были) выпадают. Навыходах сумматора 22 и входах суммато"р;: 20 значения си алов сохраняются,На выходе 36 суммы сумматора 20 уста вливается...

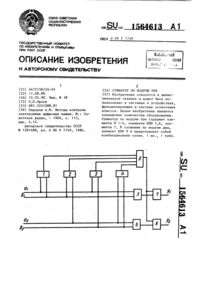

Сумматор по модулю три

Номер патента: 1564613

Опубликовано: 15.05.1990

Автор: Орлов

МПК: G06F 7/49

...к вычислительной технике и может быть исполь-зовано в системах и устройствах,функционирующих в системе остаточныхклассов.Цель изобретения - сокращение количества оборудования.На чертеже представлена функцион,льная схема сумматора по модулю 10т и.Сумматор по моцулю три содержитэ ементы И 1-4, элементы ИЛИ 5 и 6,э ементы 7 и 8 сложения по модулюд а и элемент ИЛИ 9. , 15Сумматор работает следующим образ м.Суммируемые модульные остатки А ==а а, и В = ЬЬ, заданы двухразрядн ми кодами, Известно, что результат 20с ммирования С = 2 У У как функцияо А и В определяется в соответствиис таблицей.Из анализа таблицы следует, чточ тырехэлементные входные комбинации 25( а,ЬЬ), содержащйе в точностид е единицы, соответствуют инверсномуз ачению...

Параллельный накапливающий сумматор

Номер патента: 1564614

Опубликовано: 15.05.1990

Авторы: Квитка, Кожемяко, Короновский

МПК: G06F 7/49

Метки: накапливающий, параллельный, сумматор

...триггеров 1 - 1 з.Сложение начинается подачей на входы 5 - 5и 7 1 - 7 соответственно первого и второго слагаемых. Все триггеры 1 - 1 и тех разрядов сумматора, в которых второе слагаемое со" держит "1", устанавливаются в состояние "1", а выходы элементов НЕРАВНО" ЗНАЧНОСТЬ 2- 2 п разрядов, содержащих "1", устанавливаются также в15 состояние "1", При этом, несмотря на. присутствие "1" на счетных входах триггеров 1- 1 и в виде выходных единичных сигналов элементов НЕРАВНОЗНАЧНОСТЬ 2- 2 д, состояние триг геров не изменяется. Изменение состояния триггеров происходит в том слу;ае, когда элементы НЕРАВНОЗНАЧНОСТЬ 2 - 2 и соответствующих разрядов пе,реходят из состояния "1" в состояние 25"0", Переход из состояния "1" в состояние 0" возможен в...

Параллельный накапливающий сумматор

Номер патента: 1564616

Опубликовано: 15.05.1990

Авторы: Бенашвили, Вашакидзе, Имнаишвили, Натрошвили

МПК: G06F 7/50

Метки: накапливающий, параллельный, сумматор

...код 0000 (при этом пятый разряд сумматора переходит в единичное состояние).Для вычитания двоичных операндов разрешающий сигнал подается на входы 20 14 и 15, В результате вторые элементы И 4 и ИЛИ-НЕ 6 оказываются подготовленными для приема информации, Приэтом на выходе второго элемента И 4 первого разряда присутствует низкий 25 потенциал, поскольку на его третий вход постоянно подается низкий потенциал с входа 9. Предположим, что в разрядах сумматора предварительно введено уменьшаемое, представляющее 30 собой кбд 10000. Разряды вычитаемого операнда подаются на информационные входы 11 -11, сумматора. Предположим, что вычитаемое представлено ко-дом 0111. В первом разряде единица на первом входе второго элемента ИЛИНЕ 6...

Сумматор по модулю пять

Номер патента: 1566342

Опубликовано: 23.05.1990

Автор: Музыченко

МПК: G06F 7/49

...элементзапрета и один элемент И - НЕ, 1 ричемвход третьего разряда первого слагаемого сумматора соединен с первымивходами третьего элемента ИЛИ и четвертого элемента И, вход третьегоразряда второго слагаемого сумматорасоединен с первым входом третьегоэлемента И и вторыми входами третьего элемента ИЛИ и первого элемента И,вхоц второго разряда первого слагаемого сумматора соединен с первымивходами четвертого элемента ИЛИ и пятого элемента И, второй вход которогосоединен с вторым входом четвертогоэлемента ИЛИ и входом второго разрядавторого слагаемого сумматора, входпервого разряда первого слагаемогокоторого соединен с первыми входамиэлемента И-НЕ, второго элемента И ипятого элемента ИЛИ, второй вход которого соединен с входом первого...

Многоразрядный накапливающий пневматически сумматор

Номер патента: 1569812

Опубликовано: 07.06.1990

Авторы: Булгаков, Зайченко, Мовчан, Романцов

МПК: G06D 1/04

Метки: многоразрядный, накапливающий, пневматически, сумматор

...двухвхдавай сумматор, Последний содержит тре.;мембранные реле 38 - 5. Реле 40,и 44 реализуют фуцкцпк ИЛ 1, Пптаццереле 40 - 44 осуществляетск 1 о каналу 13 через дрссель 1 б.Иногоразрядць 1 й сумматор рабтаетследующим образом.В исходном состяции ц( выхде ре 31 сигнал Р = 1, так кяк перепадна дроссе 1 е б равен "0", Входнойсигнал Р 1, в канале 1 равен "0, осцовной выходной сигнал Р г канале 9 равен "0", сигнал переноса Р,1- 0 в канале 7. ри подаче сигналаР = 1 в кана.1 1 ц 1 р( йлет ца вы 112 ногораэрядный накапливающий пневматический сумматор, содержащий первый канал питания, входные каналы,одноразрядные двухвходовые сумматооь.последовательно соединенные междубой каналами переноса и перваяпа ячеек задержки на такт, связан ь,с...

Последовательный сумматор

Номер патента: 1571573

Опубликовано: 15.06.1990

Авторы: Андреев, Малиночка, Черняк

МПК: G06F 7/49

Метки: последовательный, сумматор

...поступает значение старшего разряда, в данном случае единица, Одноразрядный сумматор 3 производит сложение единицы, присутствующей на егопервом входе, с нулями, присутствующими на втором входе и входе переноса. На выходе суммы одноразрядногосумматора 3 получается единичныйсигнал, а на выходе переноса - нулевой. На выходах 26 - 21 блока 2 формирования дополнительных сигналовсуммы и переноса формируется код000010. По переднему фронту синхроимпульса в регистр 1 записывается код000 О, в триггер 4 задержки записывается нуль, а в триггер 8 задержкизаписывается единица. На вход 11 поступает нулевое значение следующегоразряда входного кода, Одноразрядныйсумматор 3 производит сложение нулей,присутствующих на всех его входахи на выходах...

Параллельный двоичный сумматор

Номер патента: 1571577

Опубликовано: 15.06.1990

Автор: Марченко

МПК: G06F 7/50

Метки: двоичный, параллельный, сумматор

...Р, и Р,так как воздействие на В-вход триггера 3 ( + 1 ) сигналом Р; +, продолжается после снятия сигнала до установления триггеров 3 (1 + 1) и2 ( + 1) в ноль,После установления триггеров2 , 3в ноль сигнал с 1 равенединице, и если в ячейке 1 (х - 1)имеется условие возникновения сигнала переноса Й 1 ф(й 1; 11 ф 1-а)сигнал Р;на выходе элемента ИЛИ7 (. - 1) становится равен единицеи устанавливает по Б-входу н единицутриггер 3 (1), Поскольку на предыдущем этапе распространения переносаи инверсного переноса триггеры 2 .и 3 (5.) были установлены в ноль, итриггер 2 (х) сигналом Р; 1 в единицу не устанавливается, перенос изячейки 1 ( - 1) в ячейку 1далее н ячейку 1 ( + 1) не распространяется,Из описанного ныне следует, чтоперенос Р в любой...

Одноразрядный двоичный сумматор

Номер патента: 1575170

Опубликовано: 30.06.1990

Авторы: Заболотный, Максимов, Петричкович, Филатов

МПК: G06F 7/50

Метки: двоичный, одноразрядный, сумматор

...выходах 12 и 13+ (а;О+Ь;) 1;Я = 1;.,ЯК;=1;, 3(а;9 Ь;);8 = 1 9 К =1, (+)(а;ЮЬ,).Благодаря наличию,цвух выхоцовосумм Я; и 8, и двух выходов переносов 1. и 1 ф сумматор позволяет(Формировать два комплекта сумм и переносов: один при условии, что входящий в группу перенос равен нулю,а другой при условии, что входящий.перенос равен единице, Таким образам, "предлагаемый сумматор может бытьиспользован при построении условногосумматора (см, фиг,2),Формула изобретенияОдноразрядный двоичный суюазор, содержащий элемент РАВНОЗНАЧНОСТЬ, блок Формирования суммы и блок формирования перекоса, причем входы слагаемых сумматора подключены к.входам элемента РАВНОЗНАЧНОСТЬ прямой и инверсный выходы которого соединены соответственно с первыми и вторыми входами...

Одноразрядный десятичный сумматор в коде “5421

Номер патента: 1575171

Опубликовано: 30.06.1990

Автор: Тимошкин

МПК: G06F 7/50

Метки: 5421, десятичный, коде, одноразрядный, сумматор

...причем выходы разрядов трехразрядного двоичного сумматора соединены с первыми входами соответствующих разрядов корректирующего трех- разрядного двоичного сумматора, выходы разрядов которого соединены с выходами разрядов десятичного сумматора с первого по третий, выход четвертого разряда которого соединен с выходом сумматора по модулю два, первый, второй и третий входы блока формирования сигнала коррекции соединены с выходами соответственно первого, второго и третьего разрядов трехразрядного двоичного сумматора, а выход годключен к вторым входам первого и второго разрядов корректирующего треХраЗ - рядного двоичного сумматора, входу первых, вторых и третьих разрядов первого и второго операндов десятичного сумматора соединены...

Четырехвходовый одноразрядный сумматор

Номер патента: 1575172

Опубликовано: 30.06.1990

МПК: G06F 7/50

Метки: одноразрядный, сумматор, четырехвходовый

...сумматор работает следующим образом,На входы 6 .9 подаются двоичные переменные х. хсоответственно, На выходе 10 реализуется логическая функция Значения логических функций, реализуемых четырехвходовым одноразрядным сумматором, представлены в таблице. х/6 х /7 х/8 х/9 Г/12 Г/11 йо/10 25 й = х х 9 хЯ Формула изобретения Четырехвходовый одноразрядный сумматор, содержащий элемент И и элемент СЛОЖЕНИЕ ПО МОДУЛЮ 2, выход которого соединен с выходом суммы сумматора, а -й вход (=1,2,3) соединен с 30 Е = К(К(х,х,х,х )к х х хххЧх хххЧхххх 4 Ух хух х) х-м входом сумматора, четвертый вход 35соединен с четвертым входом сумматора и первым входом элемента И, выход соответствующая сигналу младшего переноса, На выходе 12 реализуется логическая...

Параллельный накапливающий сумматор

Номер патента: 1578710

Опубликовано: 15.07.1990

Авторы: Квитка, Кожемяко, Стратиенко

Метки: накапливающий, параллельный, сумматор

...входные мультиплексоры 31-3 я поступят на вторые входы элементов , 2-2 НЕРАВНОЗНАЧНОСТЬ, Все элементы 2 -2 тех разрядов, в которых слагаемое содержит "1", устанавливаются в состояние "1". При этом триггеры в 1 и остаются в прежнем состоянии, несмотря на присутствие "1" на их счетных входах, Триггеры 1 -1 изменяют свое состояние в том случае, .когда элементы 2-2 НЕРАВНОЗНАЧНОСТЬ соответствующих разрядов переходят из состояния "1" в состояние "0. При следующем такте. сигналы, присутствующие на входах 5-5сумматора, снимаются. Элементы 2-2 НЕРАВНОЗНАЧНОСТЬ, находящиеся в состоянии "1", переходят в состояние "0", Триггеры 1-1 соответствующих разрядов переходят в состояние "1". Четные разряды в "сжатом" виде первого операнда ("1111") будут...

М-разрядный комбинационный сумматор

Номер патента: 1580348

Опубликовано: 23.07.1990

Авторы: Ильин, Кравченко, Юсупов

МПК: G06F 7/50

Метки: комбинационный, м-разрядный, сумматор

...И нулевого узла суммирования, вторые входы которых соединены с входом нулевого разряда второго слагаемого сумматора, выход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ каждого узла суммирования соединен с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ этого узла суммирования, выходкоторого является выходом соответствующего разряда суммы сумматора, выход первого элемента И -го узласуммирования соединен с первым входом первого элемента ИЛИ -го узласуммирования, второй вход которогосоединен с выходом второго элементаИ -го узла суммирования, вход переноса сумматора соединен с первымивходами третьих элементов И 1-х узлов суммирования и первым входомэлемента И узла переноса, выход которого соединен с первым входом элемента ИЛИ узла переноса, второй...

М-разрядный комбинационный сумматор

Номер патента: 1580349

Опубликовано: 23.07.1990

Авторы: Ильин, Кравченко, Юсупов

МПК: G06F 7/50

Метки: комбинационный, м-разрядный, сумматор

...бы одно значение Р0 (1 с = О 1.-1), т.е. хотя быв одном разряде, предшествующем -му,разряды слагаемых имеют одинаковыезначения (А 1, = О, В = О или А = 1,В 1, 1). При этом входной переносне оказывает влияния на формированиео = Ао Во 6 С Выходной перенос сумматора формируется на элементах И 13 и ИЛИ 14 в соответствии с выражениемоСон = С м+ СдиРо Р,Р и выдается на выход 15. 30 Формула изобретенияМ-разрядный комбинационный сумматор, состоящий из М узлов суммирования и узла переноса, содержащего элемент И и элемент ИЛИ, выход кото - рого соединен с выходом переноса 4 О сумматора, причем все узлы суммирования содержат два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и элемент И, а д-й узел суммирования (где= 1,2. М) дополнительно содержат три элемента И 45 и...

Матричный сумматор

Номер патента: 1582187

Опубликовано: 30.07.1990

МПК: G06F 7/50

Метки: матричный, сумматор

...пропускает на входы узла 14 кодых(х + 2)птод 4 = 1;уз (у - 2)птой 4, щ 2При этом на выходах результата ипереноса узла 14 формируются кодыг. - 3;р -0Пороговый элемент 23 ошибки необнаруживает и элемент И 7 остаетсяоткрытым.На выходе результата узла 15 фор"мируется кодг ф (г + св)птос 14 = 1. 2187Этот код записывается в регистр22 по очередному тактовому импульсучерез элемент И 13, Но из-за неисправности этого регистра в него записывается код г = 0000.ОТакой же код формируется и на выходе узла 16, что обнаруживает пороговый элемент 24.10 По сигналу с выхода элемента И 7на регистр 19 записывается код 0,который затем через элементы И группы26 поступает на вход узла 27 дешифрации, на выходе которого формируется код переноса р = 0. Узел 29...

Параллельный накапливающий сумматор

Номер патента: 1587496

Опубликовано: 23.08.1990

Авторы: Квитка, Короновский, Лебедева, Лужецкий, Стахов

Метки: накапливающий, параллельный, сумматор

...вход второго сумматора 26,по модулю два поступает потенциалЛог, О" (Лог. 1 п) и на его выходеформируется потенциал пЛог, О (Лог.1 ), который поступает на второйвход второго элемента И 24, При несовпадении (совпадении) двух "Лог.1"на входе второго элемента И 24; наего выходе формируется потенциал"Лог.О" (Лог,1) и на шине переноса формируется сигнал заема г, = О(г; =1). В момент поступления повходу 3 счетного импульса триггер 22переключается в противоположное состояние.При вычитании в прямом коде, в случае, когда уменьшаемое меньше вычитаемого, возникают заемы в триггеры18 и 19 знака, предварительно установленные в нулевое состояние, которые в виде единиц заема распростра-,няются в мультиплексоры 16 и, 1 7.С их помощью триггеры 18 и 19...

Комбинационный сумматор

Номер патента: 1589269

Опубликовано: 30.08.1990

Авторы: Ильин, Кравченко, Юсупов

МПК: G06F 7/50

Метки: комбинационный, сумматор

...Значение условного пеореноса С., проходит через элементы,ИЛИ 23-25, соответствующие (1.-1)-муразряду суммирования, на входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 6-8 соответствено, и 1.-й разряд суммы Б; будет равенБ. = А ЗВ;ЮС;.,Второй случай.Все значения Р =1К (К=О, , 1-1), т.е. во всех разрядах, предшествующих 1-му, разряды слагаемых имеют разные значения (А =О, В, =1 или Ак=1, В=О) . При этом в связи с тем что условием формирования15892 условных переносов является равенство нулю входного переноса, все С =О.о Входной перенос сумматора проходит через элементы И 13-15 ИЛИ 23-2515 соответствующие (1-1)-му разряду суммирования, на входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 6-8 соответственно и определяет значение истинного переноса из (1-)-го разряда...

Разрядно-аналоговый сумматор

Номер патента: 1589293

Опубликовано: 30.08.1990

Авторы: Гильгурт, Добрыдина, Новицкий, Романцов

МПК: G06G 7/14

Метки: разрядно-аналоговый, сумматор

...шины 4;напряжение на третьемвыходе (-1)-го аналогоразрядного преобразователя Й-Днапряжение на первомвыходе (д+1)-го аналогоразрядного преобразователя ф+1),В начальный момент времени на 30 и-разрядные шины 3 и 4 подаются входные сигналы, а именно: на вход 3.1 напряжение 2 В; на вход 3,2-" напряжение 6 В; на вход 3.3 - напряжение 8 В; на вход 4.1 - напряжение 4 В; на вход 4.2 - напряжение 8 В; на вход 4,3 - напряжение 5 В,На выходах аналоговых сумматоров 1появляются напряжения; 40 3 Б (1 = -О 1( е 2 + -- 4 + О+О) 1 Ю ф 4 4Эти напряжений подаются на входыаналого-разрядных преобразователей 2, 55Рассмотрим подробнее работу аналого-разрядных преобразователей на при" мере второго разряда. Напряжение 11 = -0,65 В инвертируется ацалоговым...

Параллельный сумматор

Номер патента: 1594523

Опубликовано: 23.09.1990

Автор: Телековец

МПК: G06F 7/49

Метки: параллельный, сумматор

...с = 1 сумматор производит сло жение отрицательного двоичного числа(а) с числом в избыточноч системесчисления (Ь) а с выходов 15 и 16сумматора выдается отрицательное значение результата, т,е. с выходов 15и 16 выдаются соответственно отрицательное и положительное значения результата (Ь-а),При с = 1 сумматор также производит вычитание из двоичного положительного числа (а) числа в избыточнойсистеме счисления (Ь), а с выходов15 и 16 сумматора выдается положительное значение результата (а-Ь),Формула.изобретенияПараллельный сумматор, содержащийв каждом разряде блок Аормированияотрицательной суммы и блок Аормированин положительного переноса, первый триггер результата, причем вход синхронизации первого триггера результата соедцнен с входом...

Десятичный сумматор в избыточной системе счисления

Номер патента: 1594524

Опубликовано: 23.09.1990

МПК: G06F 7/49

Метки: десятичный, избыточной, системе, сумматор, счисления

...величина Р. Еечетырехразрядный код образуется навыходах элементов ИЛИ 21, 23-25,Сложение этой величины с промежуточным результатом осуществляется в блоке 4 Аормироваиия конечного результата, состоящем из одноразрядныхсумматоров 1-20, Тем самым в блоках 3 и 4 (коррекции и Аормирования .конечного результата) реализуетсятретий шаг алгоритма.Входы и выходы положительного иотрицательного переносов используются для связи между разрядами в параллельном многоразрядном десятичномсумматоре в избыточной зцакоразрядной системе счисления,Рассмотрим пример сложений десятичных знакоразрядных чисел по выше приведенному алгоритму. Значенияоперандов в обычном десятичном представлении равны Х = 26345, а У =- 18094,В знакоразрядном представлении их...

@ -входовый сумматор

Номер патента: 1596320

Опубликовано: 30.09.1990

Авторы: Голуб, Гричук, Царев, Чепурняк

МПК: G06F 7/50

Метки: входовый, сумматор

...разряда происходит по переднему фронту синхроимпульса, который подается по шине 5 синхронизации, по этомуже фронту записывается в соответствующие триггеры 8 и 9 информация с выходовкомбинационного сумматора 7. После подачи импульса по шине 6 установки в "0" всетриггеры устанавливаются в нулевое состояние. ПоСле первого синхроимпульса втриггеры 9 записываются значения первогомладшего) разряда соответствующих сумм,которые появляются на их выходах 3, а втриггеры 8 записываютая соответствующиезначения переноса, после второго синхроимпульса на выходах 4 появляются значения второго разряда соответствующих сумми т.д. Максимальное количество импульсов,необходимое для получения всех разрядов суммы в чисел: Т = а + 1 од 2 п + 1, где в -...

Комбинационный сумматор

Номер патента: 1596321

Опубликовано: 30.09.1990

Авторы: Варшавский, Кондратьев, Романовский, Цирлин

МПК: G06F 7/50

Метки: комбинационный, сумматор

...малосигнальный элемент НЕ29 или 30 значение логической единицы,установившееся на одном из выходов суммы в результате подачи рабочего наборавходных сигналов, сохраняется до тех пор,40 пока все входы сумматора не перейдут винертное состояние.После того, как все входы сумматораперейдут в инертное состояние, открываются транзисторы 19-26 р-типа и единичный45 потенциал поступает на входы элементовНЕ 27 и 28, где он "перетягивает" выходымалосигнальных элементов НЕ 29 и 30, врезультате чего на выходах элементов НЕ 27и 28, т.е. на выходах з и з, устанавливается50 значение логического нуля, что свидетельствует о возврате сумматора в инертное состояние, Таким образом, индикациямоментов окончания переходных процес-сов в сумматоре осуществляется по...

Накапливающий сумматор

Номер патента: 1597880

Опубликовано: 07.10.1990

МПК: G06F 7/50

Метки: накапливающий, сумматор

...По следующему тактовому импульсу на выходах регистра 2старшего разряда формируется удвоенное значение входного кода. Этотпроцесс увеличения суммы продолжается с приходом каждого очередноготактового импульса на вход записинакапливающего сумматора. Аналогичное суммирование входного кода происходит. и,в младших разрядах накапливающего сумматора, однако код суммы в них изменяется с более низкой,частотой, поскольку входы разрешениязаписи регистров 2 подключены к разрядным выходам делителя 3 частоты,Тем не менее это не приводит к искажению текущего кода числа в старшем.разряде (и, соответственно, среднейчастоты выходных сигналов накапливающего сумматора), если сохраняется кратность значения коэффициента де" ления и модуля той части...

Одноразрядный сумматор

Номер патента: 1599854

Опубликовано: 15.10.1990

Авторы: Рогозов, Срывкина, Тяжкун, Чернов

МПК: G06F 7/50

Метки: одноразрядный, сумматор

...и через диод 7 отберет входной ток транзистора 34, Последний закроется, но откроется транзистор 35, что вызовет насыщение транзистора 37. В результате на выходах сумматора устанавливаются нулевые значения сигналов: Р = Б = С.Если сигнал высокого логического уровня установлен на одном иэ входов (например, А = 1, В = С = 0), то био ОеЗ Тою Тф 2 То 3 6 з = -0,2 Тц, При этом транзистор ЗЬ откроется, что приведет к насыщению транзистора 33, который через свой коллектор и диод 7 отберет входной ток транзистора 34. Последний закроется, и, так как транзистор 35 закрыт, откроется транзистор 36 и закроется транзистор 37. В результате на выходах сумматора установятся следующие сигналы Ь = 1, Р = О.Если сигнал высокого уровня установлен на...

Накапливающий сумматор избыточного кода

Номер патента: 1603370

Опубликовано: 30.10.1990

МПК: G06F 7/49

Метки: избыточного, кода, накапливающий, сумматор

...выход 15, устанавливается на соответствующем выходе разряда выхода 16 сумматора. Одновременно единичный сигнал из шестого разряда, проходя 15 по цепочке вход 6, элемент ИЛИ 25, элемент 26 запрета, триггер 30, выход 15 одноразрядного сумматора 5, устанавливается на соответствующем выходе разряда выхода 16 сумматора, единичный сигнал из шестого разряда, проходя по цепочке вход 12, элемент ИЛИ 27, первый вход элемента И 28 одноразрядного сумматора 5, подготавливает его к срабатыванию, 25Одновременно единичный сигнал из пятого разряда проходит через вход 6, элемент И 31, устанавливается на выходе 19. одноразрядного сумматора 5 и далее поступает через вход 13 30 на второй вход элемента И 28 одноразрядного сумматора 5, вызывает его...

Сумматор по модулю семь

Номер патента: 1603371

Опубликовано: 30.10.1990

Автор: Музыченко

МПК: G06F 7/49

...22, второй вход которого соединен с выходом элемента ИЛИ-НЕ 18, а выход - с выходом первого разряда сумматора.Сумматор может содержать элемент И 23, соединенный входами с выходами элементов И 2, 4 и б, а выходом - с входами элементов ИЛИ-НЕ 14, 16 и 18.Функционирование сумматора в случае отсутствия элемента И 23 поясняется табл. 1, в которой приведены выходные сигналы всех элементов для всех возмож. ных значений входных слагаемых. Очевидно, что при подаче;на входы сумматора кодов чисел Х и У на его выходах формируется код числа (Х + 7)той 7, Исключение составляет случай Х=1=7, При этом на. выходах сумматора формируется код числа "7", т.е. результат верный, но не приведенный по модулю,Функционирование сумматора в случае наличия элемента И...