Разрядно-аналоговый сумматор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

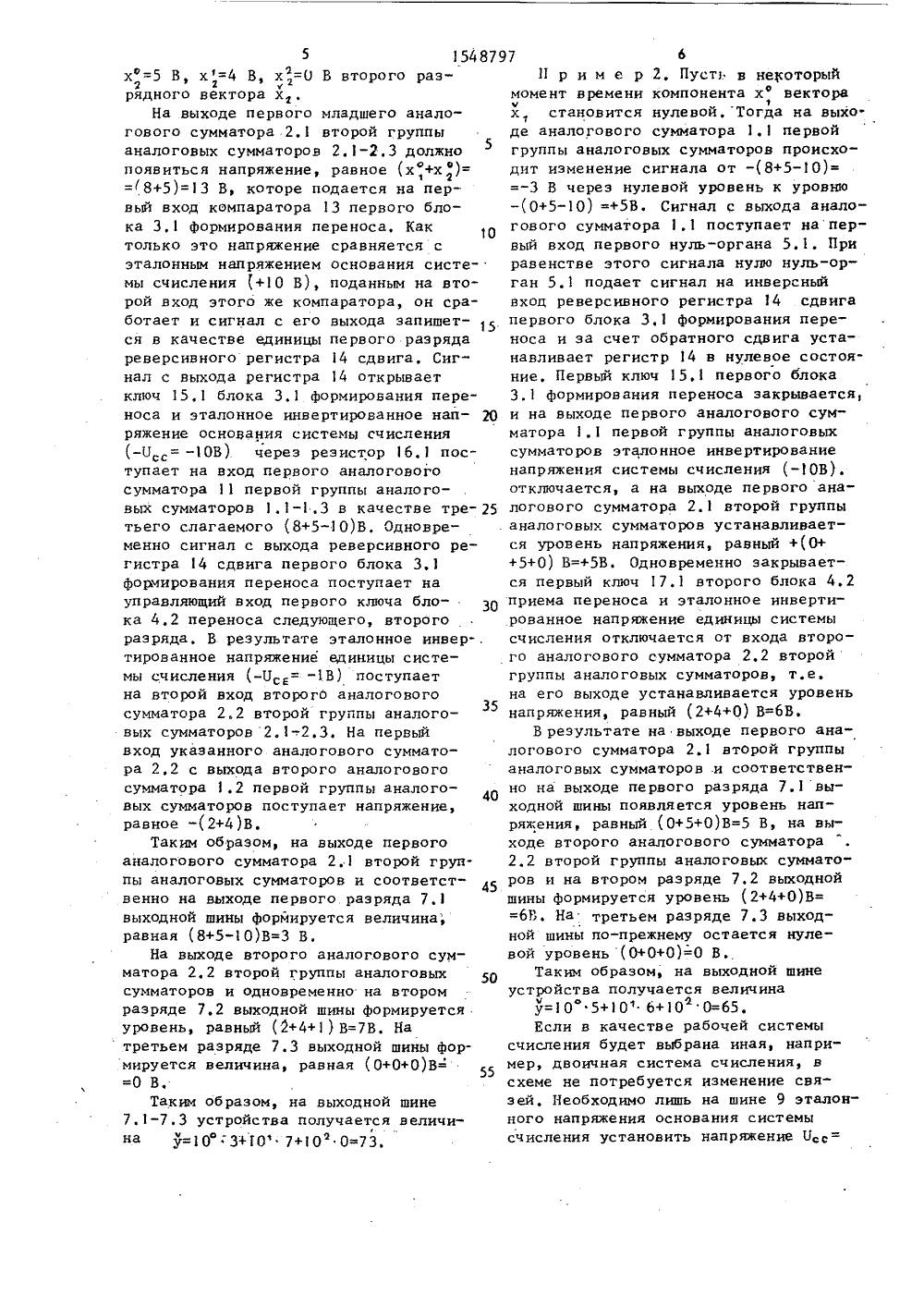

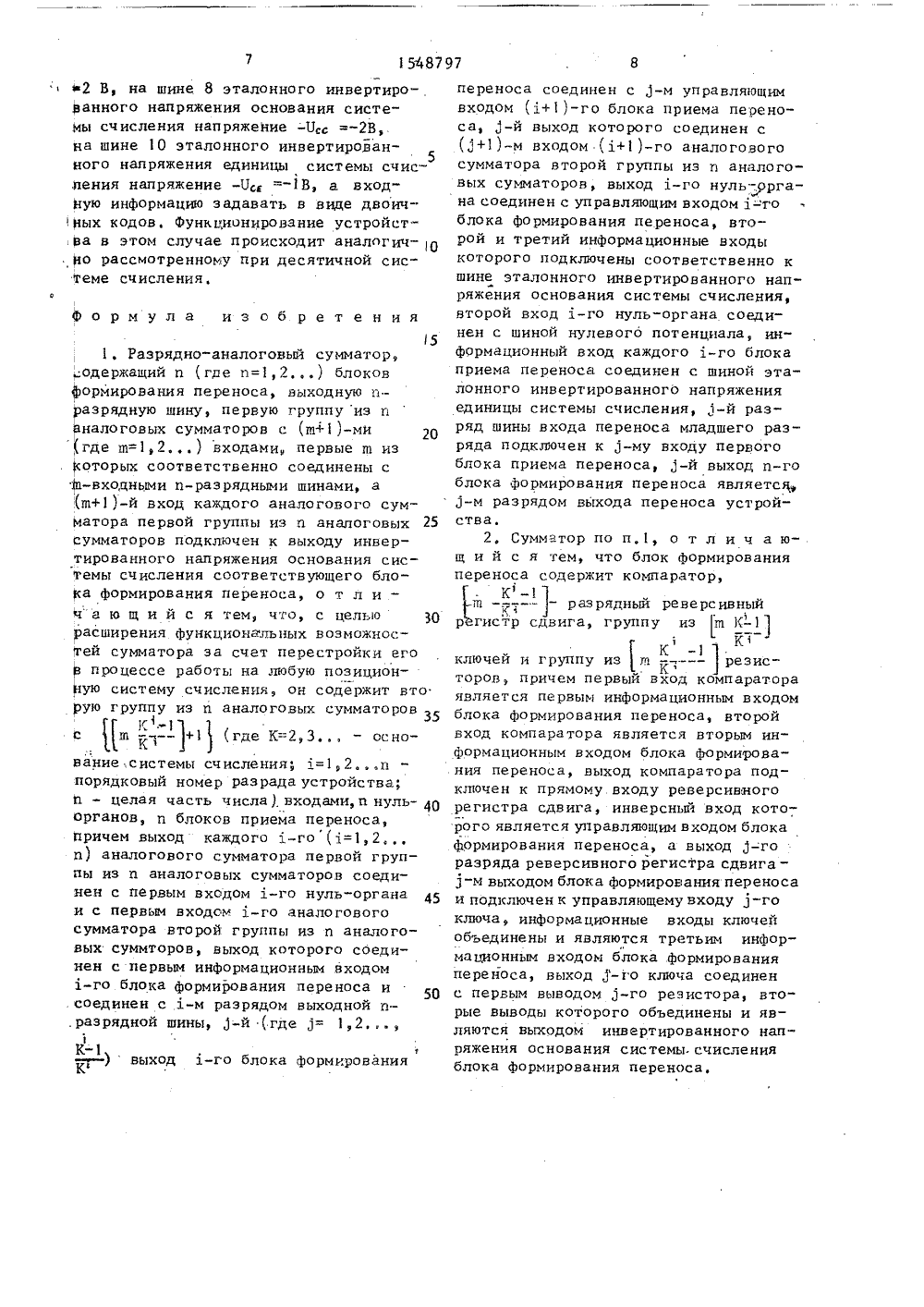

(57) Изобретение отчислитель ной технридной вычислительбыть использованометических устройс. действия. Цель изоние функциональныхтройства в части ппроцессе работы насистему счисленияжит первую и вторсумматоров 1,1, 12,3, блоки 3 формиблоки 4 приема пе5, входные шины,б ГОВЫИ СУММАТОР эн н средс лем м УС(088,8)е свидеС Об СсвицетелС 060 оманцов,льгурт о СССР1974.СС СР1874. ель с 7/14 ств/ ходную шину СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯПРИ ГКНТ СССР 1703/24-2409.8703,90. Бюл. В 9титут проблем моделированиятике АН УССР и Специальноеторско-технологическое бюромоделирования Института пролирования в энергетике АН С 51)5 С 06 С 7/14 носится к области выики, в частности к гибной технике, и может для построения арйфтв параллельногобретения - расширевозможностей усерестройки его влюбую позиционнуюУстройство содерую группы аналоговыхгф 131 и 2.1, 2,2, рования переноса, реноса, нуль-органы1548797 11 входа переноса младшего разряда, шину 2 выход% переноса старшего разряда, Перестройка на любую позиционную систему счисления достигается путем установки на шинах 8-10 соответствующих напряжений. 1 э,п,ф-лы, 3 ил. Изобретение относится.к вычислительной технике, в частности к гибриднойвычислительной технике, и может бытьиспользовано для построения арифмети-5ческих устройств параллельного действия, а также в специализированных разрядно-аналоговых устройствах в качестве основного блока для синтеза матричных умножений, функциональных преобазований и иных матричных устройств,Целью изобретения является расширение функциональных возможностей устройства в части перестройки его впроцессе работы на любую позиционную 25с ис тему сч ис лени я,На фиг. 1 приведена схема разрядно-аналогового сумматора для частотного случая, когда количество разря 30дов п.=З, количество слагаемых ш=2на Фиг, 2 - схема блока формированияпереноса; на фиг, 3 - схема блока приема переноса,Разрядно-аналоговый сумматор содер,жит первую группу аналоговых сумматоров 1.1-1,3, вторую группу аналоговых,сумматоров 2,1-2,3, блоки 3.1-3,3 формирования переноса, блоки 4.1-4,3 приема переноса, нуль-органы 5.1-5.3,входящие шины 6.1 -6,6, выходную шину7,1-7,3, шину 8 эталонного инвертиро 40ванного напряжения основания системысчисления (-У .), шину 9 эталонногонапряжения основания системы счисления (1 ), шину 10 эталонного инверти-рованного напряжения единицы системы(-У ), шину 11 ода переноса младшего разряда, шину 12 выходапереноса старшего разряда,Блок 3 формирования переноса(фиг. 2) состоит из компаратора 13,реверсивного регистра 14 сдвига, ключей 15,1-15,3, резисторов 16,1-16,3,Блок 4 приема переноса (фиг, 3)состоит из ключей 17,1-173.Работа разрядно-аналогового сумматора на примере реализации выражения вида 1 1 шину 8 эталонного инвертированногонапряжения основания системы счисления, шину 9 эталонного напряжения основания системы счисления, шину Оэталонного инвертированного напряжения единицы системы счисления, шину Представим (1) в разрядной форме,ч м чу, х х - разрядные векторы,Формируемые каку=7 г у, х,=Ег х, х=:.гх, (2)ЬО 1 о.Еогде г - основание системы счисления.Рассмотрим изложенное на примере,когда г=10, а число слагаемых ш=2П р и м е р 1, Пусть дано х,=28,х =45, тогда в соответствии с (1)у=28+45=73,Запишем исходные данные х и х1и результат у в разрядной форме, полагая, что информация представлена тремядесятйчными разрядами, т,е. п=З.Первый разряд х разрядного векто 1ра х, равен восьми, второй храэ 1ряд равендвум, а третий х равен нулю,1Разряды х, х", х разрядного векторач21 Фх равны соответственно пяти, четыреми нулю,Выполним операцио поразрядного сумм чмирования векторов хи х ,у= 710 у=1 О 3+10 7+10 0=73. Работа устройства начинается с момента подачи на шину 9 эталонного напряжения основания системы счисления напряжения, соответствующего основанию системы счисления О(например, 1 О В для десятичной системы счисления), на шину 8 эталонного инвертированного напряжения основания системы счисления напряжения -Ц =-1 О В, на шину 1 О эталонного инвертированного напряжения единицы системы счисления напряжения -У=-1 В. На шину 11 входа переноса младшего разряда (для данногоСлучая на один вход) подается нулевой потенциал. На первый разряд первой входной разрядной шины 6,1 подается напряжение, равное значению перчвого разряда вектора х те, х=8 В, на вход второго разряда первой входной разрядной шины 6,3 - значение х"=1 =2 В, а на вход третьего разряда 6,5 - значение х, =ОВ., На входы 6,2, 6,4 и 6,6 второй входной разрядной шины подаются соответственно компоненты1548797 5хф=5 В, х=4 В, х=О В второго разчрядного вектора х,На выходе первого младшего аналогового сумматора 2,1 второй группыаналоговых сумматоров 2,1-2.3 должно5появиться напряжение, равное (х,+х)==8+5)=13 В, которе подается на первый вход компаратора 13 первого блока 3,1 формирования переноса, Кактолько это напряжение сравняется сэталонным напряжением основания системы счисления (+1 О В), поданным на второй вход этого же компаратора, он сработает и сигнал с его выхода запишет.ся в качестве единицы первого разрядареверсивного регистра 14 сдвига, Сигнал с выхода регистра 14 открываетключ 15,1 блока 3,1 формирования переноса и эталонное инвертированное напряжение основания системы счисления(-У с= -10 В) через резистор 16,1 поступает на вход первого аналоговогосумматора 11 первой группы аналоговых сумматоров 1,1-1,3 в качестве третьего слагаемого (8+5-10)В. Одновременно сигнал с выхода реверсивного регистра 14 сдвига первого блока 3,1формирования переноса поступает науправляющий вход первого ключа блока 4,2 переноса следующего, второгоразряда, В результате эталонное инвер-,тированное напряжение единицы системы счисления (- = -1 В) поступаетна второй вход второго аналоговогосумматора 2,2 второй группы аналого 35вых сумматоров 2,1-2.3. На первыйвход указанного аналогового сумматора 2,2 с выхода второго аналоговогосумматора 1.2 первой группы аналоговых сумматоров поступает напряжение,равное -(2+4)В.Таким образом, на выходе первогоаналогового сумматора 2.1 второй группы аналоговых сумматоров и соответственно на выходе первого разряда 7,1выходной шины формируется величина,равная (8+5-10)В=З В.На выходе второго аналогового сумматора 2,2 второй группы аналоговыхсумматоров и одновременно на второмразряде 7,2 выходной шины формируетсяуровень, равный (2+4+1) В=7 В, Натретьем разряде 7.3 выходной шины формируется величина, равная (0+0+0)В==0 В,Таким образом, на выходной шине7.1-7,3 устройства получается величина у 1 Оф 3 фО 7+О 0 6П р и м е р 2, Пуст. в некоторый момент времени компонента хф вектора чх, становится нулевой,Тогда на выходе аналогового сумматора 1,1 первой группы аналоговых сумматоров происходит изменение сигнала от -(8+5-0)= =-3 В через нулевой уровень к уровню -(О+5-10) =+5 В. Сигнал с выхода аналогового сумматора 1,1 поступает на первый вход первого нуль-органа 5,1, При равенстве этого сигнала нулю нуль-орган 5,1 подает сигнал на инверсный вход реверсивного регистра 14 сдвига первого блока 3.1 формирования переноса и за счет обратного сдвига устанавливает регистр 14 в нулевое состоя" ние. Первый ключ 15,1 первого блока 3.1 формирования переноса закрывается, и на выходе первого аналогового сумматора 1,1 первой группы аналоговых сумматоров эталонное инвертирование напряжения системы счисления (-1 ОВ). отключается, а на выходе первого аналогового сумматора 2,1 второй группы аналоговых сумматоров устанавливается уровень напряжения, равный +(О+ +5+0) В=+5 В, Одновременно закрывается первый ключ 17.1 второго блока 4,2 приема переноса и эталонное инвертированное напряжение единицы системы счисления отключается от входа второго аналогового сумматора 2,2 второй группы аналоговых сумматоров, т.е, на его выходе устанавливается уровень напряжения, равный (2+4+0) В=63.В результате на выходе первого аналогового сумматора 2.1 второй группы аналоговых сумматоров .и соответственно на выходе первого разряда 7,1 выходной шины появляется уровень напрях;ения, равный (0+5+0)В=5 В, на выходе второго аналогового сумматора 2,2 второй группы аналоговых сумматоров и на втором разряде 7,2 выходной шины формируется уровень (2+4+0)В= =6 В. На третьем разряде 7.3 выходной шины по-прежнему остается нулевой уровень (0+0+0)=0 В.Таким образом, на выходной шине устройства получается величинау=1 0 5+10" 6+10 0=65.Если в качестве рабочей системы счисления будет выбрана иная, например, двоичная система счисления, в схеме не потребуется изменение связей, Необходимо лишь на шине 9 эталонного напряжения основания системы счисления установить напряжение 11 с=м 2 В, на шине 8 эталонного инвертированного напряжения основания системы счисления напряжение -Бсс =-2 В,на шине 10 эталонного инвертированного налряжения единицы системы счис 5ления напряжение -Б =-1 В, а входНую информацию задавать в виде двоичНых кодов, Функционирование устройст 1 Ва в этом случае происходит аналогич. Но рассмотренному при десятичной системе счисления,Формула изобретения 15 1-го блока формирования 1, Разрядно-аналоговый сумматор, содержащий и (где в=1,2) блоков ормирования переноса, выходную празрядную шину, первую группу из и аналоговых сумматоров с (ш+1)-ми (где ш=1,2) входами первые ш из Которых соответственно соединены с ш-входными и-разрядными шинами, а (ш+1)-й вход каждого аналогового сумМатора первой группы из и аналоговых 25 сумматоров подключен к выходу инвертированного напряжения основания системы счисления соответствующего блока формирования переноса, о т л и - ч" а ю щ и й с я тем, что, с целью расширения функциональных возможностей сумматора за счет перестройки его з процессе работы на любую позицион 1 ую систему счисления, он содержит вто рую группу из и аналоговых сумматоров ЗК -135 с т 1 +1 ( где К==2, 3 - ос нование,системы счисления; 1=1,2 п порядковый номер разрада устройства; П - целая часть числа ) входами, и нуль Оорганов, и блоков приема переноса, причем выход каждого -го (1=1, 2 и) аналогового сумматора первой груп - пы из и аналоговых сумматоров соединен с первым входом -го нуль-органа и с первым входсм -го аналогового сумматора второй группы из и аналоговых суммторов, выход которого соединен с первым информационным .входом-го блока формирования переноса и50 соединен с .-м разрядом выходной и- разрядной шины, )-й (где 1= 1,2,1К-)выходкр переноса соединен с )-м управляющимвходом (х+1)-го блока приема переноса, )-й выход которого соединен с+1)-м входом (т+1)-го аналоговогосумматора второй группы из п аналоговых сумматоров, выход -го нуль. органа соединен с управляющим входом д-гоблока формирования переноса, второй и третий информационные входыкоторого подключены соответственно кшине эталонного инвертированного напряжения основания системы счисления,второй вход -го нуль-органа соединен с шиной нулевого потенциала, информационный вход каждого 1-го блокаприема переноса соединен с шиной эталонного инвертированного напряженияединицы системы счисления, 1-й разряд шины входа переноса младшего разряда подключен к 1-му входу первогоблока приема переноса, 1-й выход п-гоблока формирования переноса является.1-м разрядом выхода переноса устройства,2. Сумматор по п,1, о т л и ч а ющ и й с я тем, что блок формированияпереноса содержит компаратор,К - 1 11щ в - разрядный реверсивныйКр гистр сдвига, грува у ив и И гК - 1 1ключей и группу из шрезисКторов, причем первый вход компаратораявляет ся пе рвым информационным входомблока формирования переноса, второйвход компаратора является вторым информационным входом блока формирования переноса, выход компаратора подключен к прямому входу реверсивногорегистра сдвига, инверсный вход которого является управляющим входом блокаформирования переноса, а выход -горазряда реверсивного регистра сдвига -1-м выходом блока формирования переносаи подключен к управляющему входу 1-гоключа, информационные входы ключейобъединены и являются третьим информационным входом блока формированияпереноса, выход )-го ключа соединенс первым выводом 1-го резистора, вторые выводы которого объединены и являются выходом инвертированного напряжения основания системы счисленияблока формирования переноса.1548797 Составитель В,АлекпТехред А.Кравчук Редактор рректор С,Черни Ср 3 ак оизводственно-издательский комбинат "Патент", г. Ужг л. Гагарина, 101 42 Тираж 559Государственного комитета по из 113035, Москва, Ж,ретениям и открьгт ушская наб., д, 4 исное при Г

СмотретьЗаявка

4301703, 08.09.1987

ИНСТИТУТ ПРОБЛЕМ МОДЕЛИРОВАНИЯ В ЭНЕРГЕТИКЕ АН УССР, СПЕЦИАЛЬНОЕ КОНСТРУКТОРСКО-ТЕХНОЛОГИЧЕСКОЕ БЮРО СРЕДСТВ МОДЕЛИРОВАНИЯ ИНСТИТУТА ПРОБЛЕМ МОДЕЛИРОВАНИЯ В ЭНЕРГЕТИКЕ АН УССР

ПУХОВ ГЕОРГИЙ ЕВГЕНЬЕВИЧ, РОМАНЦОВ ВЛАДИМИР ПЕТРОВИЧ, НОВИЦКИЙ АЛЕКСАНДР ФЕДОРОВИЧ, ГИЛЬГУРТ СЕРГЕЙ ЯКОВЛЕВИЧ

МПК / Метки

МПК: G06G 7/14

Метки: разрядно-аналоговый, сумматор

Опубликовано: 07.03.1990

Код ссылки

<a href="https://patents.su/5-1548797-razryadno-analogovyjj-summator.html" target="_blank" rel="follow" title="База патентов СССР">Разрядно-аналоговый сумматор</a>

Предыдущий патент: Устройство для сложения длительностей импульсов

Следующий патент: Устройство для моделирования прогиба корпуса турбины

Случайный патент: Станок для сшивания табачных листьев