Параллельный сумматор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1594523

Автор: Телековец

Текст

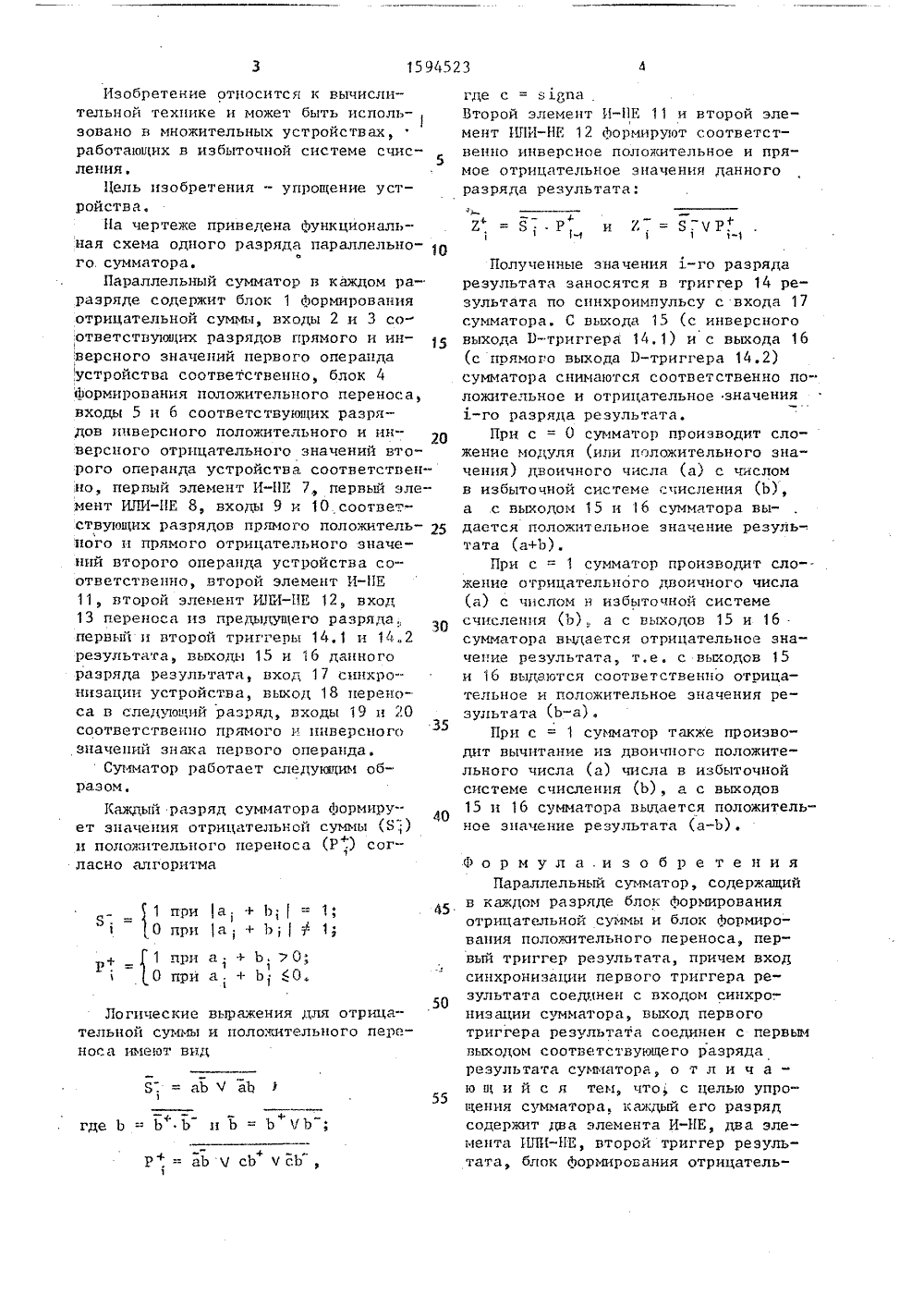

СОЮЗ СОВЕТСНИИСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 9) 111) 1 1)5 С 06 У 7/4 ОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГКНТ СССР ОПИСАНИЕ ИЗОБРЕТЕН ВТОРСНОМУ СВИДЕ 2(57) Изобретение олительной технике 1353/24-2401860990. Банрогский УМИАТО ычи осится кможет быт испольвах, ра- счисенид дю зобретения - сокр В каждый х-й раз держащий блоки 1, ицательной суммы ления. Цельоборудованиясумматора, смирования отр с пол еноса, тр14 , введ11 и два еры ре- элеа ИЛИного пега 14и-НЕ 7,12, 1 ил жителзультментаНЕ 8 ко ны дв емен 13(088.8)ое свидетельство СССРС 06 Р 7/49, 1977.свидетельство СССРС 06 Г 7/49, 1971. зовано в множительных устрои ботаищих в избыточной системИзобретение относится к вычислительной технике и может быть использовано в множительных устройствах,работающих в избыточной системе счис 5ления.Цель изобретения - упрощение устройства,На чертеже приведена функциональная схема одного разряда параллельно Ого. сумматора.Параллельный сумматор в каждом раразряде содержит блок 1 дюрмированияотрицательной суммы, входы 2 и 3 соответствующих разрядов прямого и инверсного значений первого операндаустройства соответственно, блок 4йормирования положительного переноса,входы 5 и 6 соответствующих разрядов инверсного положительного и инверсного отрицательного значений второго операнда устройства соответственно, первый элемент И-НЕ 7, первый элемент ИЛИ-НЕ 8, входы 9 и 10 соответствующих разрядов прямого положительного и прямого отрицательного значений второго операнда устройства соответственно, второй элемент И-НЕ11, второй элемент ИИ-НЕ 12, вход13 переноса из предыдущего разрядапервый и второй триггеры 14,1 и 142результата, выходы 15 и 16 данногоразряда результата вход 17 синхронизации устройства, выход 18 переноса в следующий разряд, входы 19 и 20соответственно прямого и инверсногозначений знака первого операнда.Сумматор работает следующим образом,(аждый разряд сумматора Формирует значения отрицательной суммы (Б,;) и положительного переноса (Р) согласно алгоритма1 при0 при1 при 0 прй а, +Ь; =-1; а+ Ь; Ф 1; а;+ Ь,)0; Б. = аЪ Ч аЬгдеЬ=.Ь Ь иЬ=Ь ЧЬ Р== аЬ Ч сЬ ЧсЬ50Логические выражения для отрицательной суммы и положительного переноса имеют вид где с = з 8 паВторой элемент И-НЕ 11 и второй элемент НИ-Е 12 Аормируют соответственно инверсное положительное и прямое отрицательное значения данного разряда результата:Х. = Б. ЧРПолученные значения .-го разрядарезультата заносятся в триггер 14 результата по сннхроимпульсу с входа 17сумматора. С выхода 15 (с инверсноговыхода Ь-триггера 14.1) и с выхода 16(с прямого выхода Р-триггера 14.2)сумматора снимаются соответственно положительное и отрицательное значения-го разряда результата,При с = 0 сумматор производит сложение модуля (или положительного значения) двоичного числа (а) с числомв избыточной системе счисления (Ь),а с выходом 15 и 6 сумматора выдается положительное значение результата (а+Ь).При с = 1 сумматор производит сло жение отрицательного двоичного числа(а) с числом в избыточноч системесчисления (Ь) а с выходов 15 и 16сумматора выдается отрицательное значение результата, т,е. с выходов 15и 16 выдаются соответственно отрицательное и положительное значения результата (Ь-а),При с = 1 сумматор также производит вычитание из двоичного положительного числа (а) числа в избыточнойсистеме счисления (Ь), а с выходов15 и 16 сумматора выдается положительное значение результата (а-Ь),Формула.изобретенияПараллельный сумматор, содержащийв каждом разряде блок Аормированияотрицательной суммы и блок Аормированин положительного переноса, первый триггер результата, причем вход синхронизации первого триггера результата соедцнен с входом синхро-. низации сумматора, выход первого триггера результата соединен с первым выходом соответствующего разряда результата сумматора, о т л и ч а -ю щ и й с я тем, что с целью упрощения сумматора. каждый его разряд содержит два элемента И-НЕ, два элемента ИЛИ-НЕ, второй триггер результата, блок Аормирования отрицательСоставитель И. ЕсенинаТехред И,Ходанич Корректор В, Гирняк Редактор Е, Папп Заказ 2829 Тираж 5 б 3 Подписное ВНИИПИ Государственного комитета пО изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж, Раушская наб., д. 4/5 Производственно-издательский комбинат "Патент", г.ужгород, ул. Гагарина,101 5 15945 ной суммы содержит элемент Ы-ИЛИ-НЕ, причем вход прямого значения данного разряда первого операнда сумматора соединен с первым входом первой группы элемента И-ИЛИЕ блока Ьор. мирования отрицательной суммы, выход которого соединен с первыми входами первого элемента И-НЕ и первого элемента ИЛИ-НЕ, второй вход первого эле О мента ИЛИ-НЕ соединен с вторым входом первого элемента И-НЕ и входом переноса из предыдущего разряда сумматора, выходы первых элементов И-НЕ и ИЛГ-НЕ соединены с единичными входами соответственно первого и второго триггеров результата, блок формирования положительного переноса содержит элемент И-ИЛИ-НЕ, первый вход .первой группы которого соединен с 20 входом инверсного значения соответствующего разряда первого операнда сумматора и первчм входом второй группы элемента ИП 1-БЕ блока Аормирования отрицател:-ной суммы первый 25 и второй входы второго элемента И-НЕ соединены соответственно с входом инверсного положительного значения соответствующего разряда второго операнда сумматора и .с входом инверсного отрицательного значения соответствующего .разряда второго операнда сумматора, выход второго элемента5 6И-НЕ соединен с вторым входом второй группы элемента И-ИЛИ-НЕ блокафорюрования отрицательной суммы, второй в.".сд первой группы которого соединен с вторым входом первой группы элемента И-ИЛИ-НЕ блока Формирования положительного переноса и выходом второго элемента ИЛИ-НЕ, первый вход которого соединен с входом прямого положительного значения соответствующего разряда второго операнда сумматора и первым входом второй группы элемента И-ИЛИ-НЕ блока Формирования положительного переноса, первый вход третьей группы которого соединен с вторым входом второго элемента ИЛИ-НЕ и входом прямого отрицательного значения соответствующего разряда второго операнда, входы прямого и инверсного значений знака первого операнда сумматора соединены с вторыми входами соответственно второй и третьей групп элемента И-ИПИ-НЕ блока ормирования положительного переноса, выход которого соединен с выходом переноса в сле"дующий разряд сумматора вход синхронизации сумматора соединен с входом синхронизации второго триггера результата, прямой выход которого соединен с вторым выходом соответству-. ющего разряда результата сумматора,

СмотретьЗаявка

4011353, 13.01.1986

ТАГАНРОГСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. В. Д. КАЛМЫКОВА

ТЕЛЕКОВЕЦ ВАЛЕРИЙ АЛЕКСЕЕВИЧ, ТЕЛЕКОВЕЦ МАРИНА ВАЛЕРИЕВНА

МПК / Метки

МПК: G06F 7/49

Метки: параллельный, сумматор

Опубликовано: 23.09.1990

Код ссылки

<a href="https://patents.su/3-1594523-parallelnyjj-summator.html" target="_blank" rel="follow" title="База патентов СССР">Параллельный сумматор</a>

Предыдущий патент: Четырехквадрантный умножитель

Следующий патент: Десятичный сумматор в избыточной системе счисления

Случайный патент: Способ регулирования температуры форм стеклоформующих машин