Патенты опубликованные 23.07.1988

Сумматор кодов фибоначчи

Номер патента: 1411735

Опубликовано: 23.07.1988

Авторы: Лужецкий, Соболева, Стахов, Черняк

МПК: G06F 7/49

Метки: кодов, сумматор, фибоначчи

...+ 1), (3. + 2)-го разрядов суммыЯ Я 1+ ф Ясоответственно,полученным на основе анализа условий,при наличии которых возникает переносв -м разряде суммы,Таким образом 10 з 14117Следовательно, значение 1.-го разряда суммы определяется значениями перечисленных сигналов (точнее наличием каких-либо из них либо отсут 5 ствием). Сумматор кодов фибоначчи позволяет получать сумму кодов Фибоначчи в минимальной форме за один такт,15Формула изобретения Сумматор кодов Фибоначчи, содержащий в каждом разряде первый, второй, третий, четвертый элементы И, первый, 20 второй, третий, четвертый элементы ИЛИ, первый, второй, третий элементы НЕ, причем входы 1-го разряда первого и второго операндов, где 1. = 1,п, и - разрядность операндов, сумматора 25...

Одноразрядный двоичный сумматор

Номер патента: 1411736

Опубликовано: 23.07.1988

Автор: Дьяченко

МПК: G06F 7/50

Метки: двоичный, одноразрядный, сумматор

...выход 11 сигнала генерации переноса, выход 12 сигнала переноса,вход 13 управления режимом работы,В представленной схеме подаваемый 25на вход 6 первый операнд эадан в прямой форме А, подаваемый на вход 7второй операнд задан в инверсной форме В, а подаваемый на вход 8 переносзадан в прямой форме С, в связи счем узел 1 выполнен на псслецовательно включенных элементах РАВНОЗНАЧНОСТЬ 14 и НЕРАВНОЗНАЧНОСТЬ 15, узел2 - на элементе И-НЕ 16, узел 3 - на,элементе ИЛ 1-НЕ 17 узел 5 - на эле 335менте НЕРАВНОЗНАЧНОСТЪ 18.Сумматор работает следующим образом.При подаче на вход 13 сигнала Я=1выполняется операция "А плюс В", гдеоперанды А и В представлены в прямыхкодах. При Я=О сумматор выполняетоперацию "А минус В" также в прямыхкодах. Одноразрядный...

Комбинационный сумматор

Номер патента: 1411737

Опубликовано: 23.07.1988

Авторы: Варшавский, Гольдин, Кондратьев, Цирлин

МПК: G06F 7/50

Метки: комбинационный, сумматор

...выходы р и р схемы оказываются в инертном состоянии, в результате чего открываются.транзисторы 26 и 27Значение О на входе элемента НЕ 39 появляется после того, как открываются транзисторы 3,6 и 8, т,е, после того, как в инертное состояние возвращаются входы а, Ь и р. В результате на выходе элемента НЕ 39, т.е, вы" ходе в, появляется значение 1, схема возвращается в инертное состояние.Таким образом, рабочее состояние выходов з и в суммы данного разряда .появляется только после того, как .все его входы (в том числе и переноса из предыдущего разряда) перейдут из инертного в рабочее состояние. При этом рабочее состояние на выходах(р и р переноса в следующий разряд могут вырабатываться и до этого (на нулевом и единичном рабочих наборах)В...

Цифровой функциональный преобразователь

Номер патента: 1411738

Опубликовано: 23.07.1988

МПК: G06F 7/544

Метки: функциональный, цифровой

...в старший ра 8 последовательных после чего на его вы" ется код 71, а на вхоравнения - коды чисел енство (1) можно У Х 2= Х 1,и работа п равлена на разователя буде бор такого числ наУ ходит л раэ8 последотех пор;венство Описанный процесс прои (п - разрядность регистра вательных приближений) до пока не будет соблюдено р (2). После этого с выхода функционального преобразо но считывать код числа У. цифровогоателя можО ормула из т е я Цифровой функциональный преобразователь, содержащий два регистра, первый умножитель, первый блок памяти значений синуса и косинуса, схему сравнения и регистр последовательных приближений, причем входы первого и второго аргументов преобразователя соединены с информационными входами первого и второго...

Синусно-косинусный преобразователь

Номер патента: 1411739

Опубликовано: 23.07.1988

Авторы: Агизим, Горячева, Карплюк, Крамаренко

МПК: G06F 7/548

Метки: синусно-косинусный

...первого синхронизируюшего импульса на синхронизируюшие входы регистры синуса 1 и косину са 2 запоминают значения аи Ь поэтому на выходах сумматоров синуса 3 и косинуса 4 образуютсяновые числа а и Ь , причем 2а + 1 Ь(а + 1 Ь) ( - с) . После прихода п синхроимпульсов в регистрах оказываются числа а и Ь причемяЗласЕса+ 1 Ь= (а + 1 Ъ) (1 + ск )е(4) Процесс протекает в соответствии с (1) до тех пор, пока не изменится знак числа в регистре 2. Вследствие этого меняется связь между предыдущим и следующим состояниями, т.е.система уравнений (1) заменяется сле- дующей(1 + се ), (6) Так как умножение на положительное число не меняет знаков, то знак ЪЬ+1 совпадает со знаком Ь , поэтому вновь вступает в силу правило. (1), Однако знак Ь,...

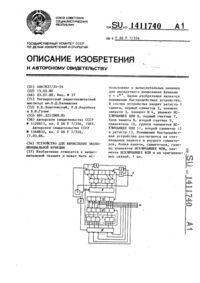

Устройство для вычисления экспоненциальной функции

Номер патента: 1411740

Опубликовано: 23.07.1988

Авторы: Гузик, Золотовский, Коробков

МПК: G06F 7/556

Метки: вычисления, функции, экспоненциальной

...сумматор 12, регистр 13, выход14 устройства.Аргумент х записывается в и-разрядный регистр 1, который представляет собой регистр сдвига. Единичныевыходы всех разрядов регистра 1 (кроме старшего) соединены с входами(п)-разрядного комбинационного сумматора 2. Выходы сумматора 2 .соединены с входами регистра 1 со сдвигомна один разряд в сторону старших разрядов, Выход элемента 3 запрета соединен с входом регистра 1, управляю щнм сдвигом в нем на один разряд всторону старших разрядов, Выход элемента И 4 соединен с входом, управляющим записью сдвинутой суммы изсумматора 2 в регистр 1. Элемент 3запрета и элемент И 4 управляются,сигналом с тактового входа 5 устройства, Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 6, сое-диненный с единичнымивыходами двухстарших...

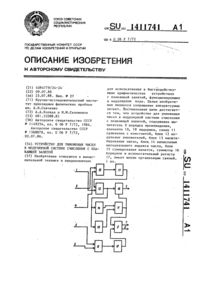

Устройство для умножения чисел в модулярной системе счисления с плавающей запятой

Номер патента: 1411741

Опубликовано: 23.07.1988

МПК: G06F 7/72

Метки: запятой, модулярной, плавающей, системе, счисления, умножения, чисел

...являющегося оценкойдроби А В Я/М, выходит за пределыинтервала-р - 1, р - 1, то число35С 1 Р, В этом случае дробь С /М, гдеС - оценка дроби А В/М, являетсянормализованной и, следовательно,представляет собой мантиссу результата, в противном случае в качествемантиссы результата принимается дробьС/М. При этом в первом случае порядок результата определяется соотношением 4(С) = 1(а) + 4(В), а во втором - соотношением (С) = 1(а) +45+ 4 (В) - 1,Устройство работает следующим образом.На первом такте работы модулярныекоды (с 1,с(,) числителя А мантиссы М(а) и (1"1,) числителя В мантиссы М(В) с входов 3 и 4 поступаютсоответственно на первый и второйвходы блока 12 модульных умножителей,который получает модулярный код(ъ ъ) произведения С = А"В,...

Устройство для сложения и вычитания чисел с плавающей запятой

Номер патента: 1411742

Опубликовано: 23.07.1988

МПК: G06F 7/72

Метки: вычитания, запятой, плавающей, сложения, чисел

...28 интегральных характеристик модулярного кода, который начинает вычисление поправки Амербаева 6(С)и коэффициентов симметрического полиади 5 10 г 8ва и коэффициентов симметрического полиадического кода, При этом поправкаАмербаева с выхода формирователя 28интегральных характеристик модулярного кода через четвертый информационный вход подается в блок 29 формирования признака аддитивного переполнения, где по ней и вычету 1 формируется признак аддитивного переполненияЯ , который передается с выхода, блока29 формирования признака аддитивногопереполнения на первый вход блока35 задержки55 ческого кода числа С. Одновременно сэтим на (Т+7)-м такте модулярные коды числа А с выхода второго элемента24 задержки и 3 с выхода блока...

Микропрограммное устройство управления с контролем переходов

Номер патента: 1411743

Опубликовано: 23.07.1988

Авторы: Календарев, Кряжев, Новоселов

МПК: G06F 11/36

Метки: контролем, микропрограммное, переходов

...вьделяют участки по правилу: кон цом участка является блок, которому предшествует слияние ветвей блок-схемы. Начало следующего участка совпадает с концом предьдущего, Пример вьделенного таким образом участка приведен на фиг. 3, где О -О - опе- рации в операционной части, а Х-Х- проверяемые условия ветвления. Пусть первая микрокоманда участка, выполняющая.операцию О и безусловный переход к следующей, располагается в ячейке памяти микропрограмм с адресом (001) . При вхождении в данный участок этот адрес загружается в регистр 3 начального адреса, где и хранится 40 до окончания участка. Кроме того, сигнатурные анализаторы адресов и условий устанавливаются в начальное состояние 0001.Поскольку различным значениям Х 45 соответствуют различные...

Приоритетное устройство

Номер патента: 1411744

Опубликовано: 23.07.1988

Авторы: Бакалец, Головин, Нусратов, Петросян, Файсканов

МПК: G06F 9/50

Метки: приоритетное

...сигнал свыхода элемента ИЛИ 14 поступаетодновременно на установочные входытриггера 11 запроса и счетчика 5,. который переводит их в исходное состояние, т.е. на выходе счетчика 5устанавливается адрес ячейки блока 4памяти, в. которой записана информация об абоненте, имеющем самый высший приоритет, а на выходе триггера11 запроса устанавливается сигнал,означающий для обслуживающего устройства, что нет прерывания. Активныйсигнал с выхода блока 15 элементовИЛИ поступает на установочный входрегистра 13 запросов, что приводитк его сбросу.Активный сигнал с выхода элемента ИЛИ 17 поступает наустановочный вход регистра 6 текущего приоритета, что приводит к установке на его выходе сигнала, соответствующего самому низшему приоритету,Пока не появится...

Многоканальное устройство для обслуживания запросов

Номер патента: 1411745

Опубликовано: 23.07.1988

Авторы: Ефимов, Зарецкий, Костюченко, Мазаник

МПК: G06F 9/50

Метки: запросов, многоканальное, обслуживания

...фиг.1 представлена структурнаясхема устройства; на фиг,2 - структурная схема блока приоритета.Устройство содержит блок 1 элемен"тов И, группу блоков 2 элементов И,; блок 3 приоритета, элементы ИЛИ 4 и 5,каналы 6, в каждом канале сумматор7, элемент И 8, элемент ИЛИ 9 и элемент И 10, входящие в.блок 3 приори тета матрицу элементов 11 сравнения,группу элементов И,12,блок 13 элементов,И-ИЛИ-НЕ и сумматор 14,информационныевходы 15 устройства, запросные входы16 устройства, вход опроса 17 устрой ства, информационные выходы 18 устУройства выход 19 прерывания устрой, ства, а также группу входов 20,. груп"пу выходов 21 и группу выходов 22, блока 3,Устройство работает следующим об-разом,На сумматоры 7 каналов с входов15 заносятся...

Устройство циклического приоритета

Номер патента: 1411746

Опубликовано: 23.07.1988

Авторы: Маханек, Чернявский, Ярусов

МПК: G06F 9/50

Метки: приоритета, циклического

...И 9 узла 4 будет логический нуль, который закрывает третью схему выбора узла 3 анализа запросов,Таким образом, единичный сигнал будет только на выходе десятого элемента И второй схемы выбора узла 4 анализа, Этот сигнал в соответствии спроложенными связями поступает на выходы первого и третьего элементовИЛИ-НЕ 13 группы, что приводит к появлению кода 1010 =1 О, на адресномвыходе 18 устройства,Формула изобретенияУстройство циклического приоритета, содержащее регистр, информационные входы которого соединены с груп-, пои адресных выходов устройства, о тл и ч а ю щ е е с я тем, что, с целью повышения быстродействия эа счет параллельного анализа запросов, устройство содержит элемент НЕ и два узла анализа запросов, каждый из которых...

Многоканальное устройство переменного приоритета

Номер патента: 1411747

Опубликовано: 23.07.1988

Авторы: Кастерский, Макаров, Штанько

МПК: G06F 9/50

Метки: многоканальное, переменного, приоритета

...каналов. Тогда .элементы И 18 этих каналов открыты и наинформационном входе регистра 1 появляется серия импульсов,с объединенного выхода каналов 10, причем появление первого импульса совпадает с пятым тактом синхронизации на выходе 8.Импульс с объединенного выхода каналов 10 поступает на вход элемента И 5и на единичный вход триггера 3, нотак как триггер 3 находится в нулевом состоянии, элемент И 5 открыт иимпульс проходит на информационныйвход регистра 1,Так как триггер 6 находится в нулевом состоянии, то регистр 1 готовк последовательному приему импульсов,1В следующем такте синхронизации в последний разряд регистра 1 записывает-.ся единица, триггер 3 переходит в единичное .состояние и сигналом с инверсного выхода закрывает элемент...

Сигнатурный анализатор

Номер патента: 1411748

Опубликовано: 23.07.1988

Автор: Иванов

МПК: G06F 11/25

Метки: анализатор, сигнатурный

...изобретений и открытий113035, Москва, Ж, Раушская наб д. 4/5 Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4. Изобретение относится к вычислительной технике и может использоваться в контрольно-испытательной аппаратуре дискретных объектов,5Цель изобретения - уменьшение аппаратных затрат.На чертеже приведена функциональная схема сигнатурного анализатора.Анализатор содержит информационный 1 и тактовый 2 входы, формирователь 3 сигнатур, первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 4, сумматор 5 по модулюдва, триггер 6, второй элемент 15ИСКЛЮЧАЮЩЕЕ ИЛИ 7, элемент И 8 ивыход 9 сигнала ошибки.Анализатор работает следующим образом.В исходном состоянии все последовательные элементы анализатора находятся в нулевом состоянии. В...

Логический анализатор

Номер патента: 1411749

Опубликовано: 23.07.1988

Авторы: Альтерман, Гладштейн, Комаров

МПК: G06F 11/25

Метки: анализатор, логический

...луча осциллографа 11 и дви 11749 4 5 10 15 20 25 30 35 40 45 50 55 жением луча вблизи узлов координатной сетки. Последовательная выдачасигналов управления лучом приводит кпоявлению на экране осциллографа 11очертания соответствующей цифры.Пример формирования двух цифр (код РА)показан на Фиг.5, где Х , У исигналы управления лучом, поступающие соответственно с первого, второго и третьего выходов блока постоянной памяти; Х- сигнал смещения между двумя соседними цифрами, поступающий через резистор 23 с выхода элемента И 22; Х, У - расстояние между соседними узлами координатной сетки,Коды с переключателя 21 и мультиплексора 19 задают ту область блока 16 постоянной памяти, где записаны сигналы управления лучом для отображения...

Устройство для контроля цифровых блоков

Номер патента: 1411750

Опубликовано: 23.07.1988

МПК: G06F 11/16

...переполненияпервого счетчика 6 (тактон) поступает на вход чтения блока 11 памяти ина стробирующий вход блока 7 сравнения, Тем самым сравнивается число,содержащееся в регистре 2 сдвига,с эталонной сигнатурай, находящейсян нулевой ячейке блока 11 памяти.Принесовпадении указанных чисел на выходе несовпадения блока 7 сравненияФормируется сигнал, который поступает на выход 10 сигнала неисправностии на третий вход элемента ИЛИ 17,что приводит устройство в исходноесостояние. При совпадении чисел работа устройства не прерывается асигнал с выхода переполнения первогосчетчика 6, пройдя через элемент 14задержки, поступает на счетный входвторого счетчика 15, тем самым подготанливается к считыванию следующаяячейка блока 11 памяти, так как группа...

Устройство для контроля распределителя импульсов

Номер патента: 1411751

Опубликовано: 23.07.1988

Авторы: Кондратов, Матвеев, Язневич

МПК: G06F 11/16

Метки: импульсов, распределителя

...указывает,на исправностьраспределителя 1 импульсов.Неисправности, которые могут возникнуть при работе распределителяимпульсов,.Неисправностикоторые могут возникнуть при работе распределителяимпульсов, можно разбить на две группы:при наличии сигнала на ожидаемомвыходе имеются сигналы и на другихвыходах; отсутствует сигнал на ожидаемом выходе,В первом случае при возникнсвенииуказанной неисправности при наличиисигнала на выходе мультиплексора 9отсутствует сигнал на выходе блока10 а поэтому появляются сигналы навыходе элемента 3 сложения по модулюдва и на выходе элемента И-НЕ 7, чтоприводит к установке триггера 2, сигнал с которого подается на выход 14сбоя устройства. Отсутствие сигналана инверсном выходе триггера 2 черезэлемент И б...

Устройство для контроля электропитания цвм

Номер патента: 1411752

Опубликовано: 23.07.1988

Автор: Матюшенко

МПК: G06F 11/22

Метки: цвм, электропитания

...группу 5 элемен-.тов регистрации, датчик 6 состояния,шину 7 питания положительной поляр,ности, шину 8 опорного напряжения,положительной полярности, шину 9очистки (сброса) элементов.10 регист. датчика б состояния, Данный режим повышает надежность измерений.Элемент 1 О регистрации (фиг,2)содержит фогоприемники 18, и 18.2,токоограничительный резистор 19, триггер 20 и светодиод 21. Оптическимисвязями 22.1 и 22.2 фотоприемники18.1 и 18.2 воспринимают сигналы светодиодных элементов 16 и 17, Фотоприемники 8. и 18.2 вместе со светодиодными элементами 16 и 17 образуют две оптронные пары и могут бытьреализованы, например, на базе оптопары типа АОТ 23,Устройство работает следующим образом.В исходном состоянии, когда всеконтролируемые...

Устройство для проверки программ на сбоеустойчивость

Номер патента: 1411753

Опубликовано: 23.07.1988

Авторы: Андреев, Конищев, Малица

МПК: G06F 11/26

Метки: проверки, программ, сбоеустойчивость

...на вход 21 запуска, который переводит триггер 3 в единичное состояние. Из единичного перепада на прямом выходе триггера 3 формирователем 5 формируется импульс, который обнуляет счетчики 9, 11 и 16, Единичный уровень с прямого выхода триггера 3 запускает таймер 1 О, поступает на третий вход элемента И,2, 20 на второй вход элемента И 4 и на вторые входы элементов И 1, разрешая прохождение потенциального кода адреса команды с разрядных выходов регистра 26 адреса команды ЦВМ 25 на первые входы схемы 6 сравнения.При совпадении кодов на первых и вторых входах схемы 6 сравнения, последняя выдает сигнал, который проходит через элемент И 2.на выход 24 имитации сбоя, объединяющийся с вы ходом схем аппаратурного контроля ЦВМ 25 (не показан),...

Устройство для контроля логических блоков

Номер патента: 1411754

Опубликовано: 23.07.1988

Автор: Кузьмин

МПК: G06F 11/26

Метки: блоков, логических

...в блок 8 сравнения, на второйвход которого поступают сигналы с регистра 4,Устройство работает в два этапа:при нулевом состоянии триггера и приединичном,Соответственно этому ожиданию реакция состояний блока 7 по выходамконтролируемого блока 1 кодируется"Лог.О" и "Лог,1", Блок 7 логического согласования воспринимает третьесостояние на выходах контролируемогоблока 1 как "Лог,О" или как "Лог.1"в зависимости от состояния триггера10, так как сигнал с выхода триггера10 через элементы блока 11 развязкипоступает на вход блока 7. В качестве элементов развязки используютсярезисторы, сопротивления которых должны быть достаточно большими для того,чтобы не иекажать уровни логическихсигналов на выходах контролируемогоблока 1 и коммутатора б...

Устройство для формирования сигналов прерывания при отладке программ

Номер патента: 1411755

Опубликовано: 23.07.1988

Авторы: Богданова, Будовский, Бурковский, Гольдберг

МПК: G06F 11/28

Метки: отладке, прерывания, программ, сигналов, формирования

...одновременно через мультиплексор 10 на установочныйвход счетчика 8 ичерез элемент 36задержки на второй вход элементаИ 30.В результате н счетчик 8 черезмультиплексор 7 заносится новое значение, соответствующее значению текущего адреса на входе 14 устройстна,которое далее по заданному фронту35 строба адреса увеличивается на +2.После этого значение счетчика 8соответствует адресу следующей команды.При считывании операнда на выходеэлемента 5 присутствует запрещающийпотенциал, блокирующий элементы. И 11и 12, текущие значения счетчика 8 неизменяются и на выходе элемента И 11и соответственно на втором входе элемента И 30 и выходе 13 прерыванияустройства присутствует запрещающийпотенциал. код адреса блока 18 к приходу следующих данных на вход 43...

Устройство адресации памяти

Номер патента: 1411756

Опубликовано: 23.07.1988

МПК: G06F 12/00

...из этих абонентов,5Микропроцессор 1 и блок 2 прямогодоступа к памяти могут нзаимодействовать между собой по принципу захватауправления, каналы прямого доступа кпамяти блока 2 прямого доступа к памя 19ти конкурируют межцу собой согласноприсвоенным уровням приоритета.Согласно изобретению опознаниеактивизирующегося абонента и выбор соответствующей ему области блока 8 15преобразования адреса осуществляетсяс помощью шифратора 5 номера абонента. Шифратор 5 номера абонента осуществляет преобразование И-разрядного кода, отражающего наличие активного абонента, в.М-разрядный код (бинарный) адреса области блока 8 преобразования адреса, принадлежащейэтому абоненту. Например, при нали"чии в устройстве обработки данныхдесяти абонентов (одним из...

Устройство для обмена данными между цвм и видеотерминалом

Номер патента: 1411757

Опубликовано: 23.07.1988

Авторы: Данильченко, Ландык, Морозов, Попадина, Тимофеев

МПК: G06F 13/00

Метки: видеотерминалом, данными, между, обмена, цвм

...14 передается через информационный выход 18 устройства в каналобмена.Если триггер 21 установлен в "1",т.е, счетчиком 19 зарегистрированоболее трех повторяющихся символов,из регистра 10 признака через коммутатор 13 в выходной регистр 14 заносится код признака повторения, который через информационный выход 18устройства передается в канал обмена.Затем. из счетчика 19 через коммутатор13 в выходной регистр 14 заноситсякод числа повторяющихся символов, который также передается в канал обмена.Таким образом, осуществляется сжатие информации: в канал обмена вместопоследовательности кодов повторяющихся символов передаются три кодовыекомбинации: код повторяющегося симво"35ла, код признака повторения и кодчисла повторяющихся символов.Если...

Устройство для сопряжения к абонентов с м вычислительными машинами

Номер патента: 1411758

Опубликовано: 23.07.1988

Авторы: Баранов, Григорьев, Чудов

МПК: G06F 13/00

Метки: абонентов, вычислительными, машинами, сопряжения

...и второгоэлементов И-ИЛИ 46, однако блок 48 приоритета вырабатывает единичный иотенциап только на втором выходе, а следовательно, только на первом выхо" де блока 49 приоритета.С приходом очередных запросов на входы регистра 42 осуществляется дальнейший сдвиг единичных потенциалов ранее записанных запросов с учетом времени их поступления, при этом единичный потенциал формируется только иа первом выходе 17-1 блока 3 приоритета, После поступления первого запроса на вход 11-1 и формирования единичного потенциала на выходе 17-1 на управляющем входе триггера 57, со единенного с выходом элемента ИЛИ 56, Формируется .единичный потенциал и тактовым импульсом генератора 52 производятся установка триггера 57 в единичное состояние и Формирование...

Устройство для сопряжения между абонентами

Номер патента: 1411759

Опубликовано: 23.07.1988

Авторы: Калина, Шалугин, Школяренко

МПК: G06F 13/00

Метки: абонентами, между, сопряжения

...запись байта информации с выхода третьего "регистра 15 в блок 30 микросхем оперативной памяти. По , заднему Фронту этого импульса производится переключение счетчика 32 адреса памяти в следующее состояние, ,а счетчик 5 переключается в нулевоесостояние. После набора следующего информационного байта в.третьем сдвиговом регистре 15 на выходе счетчика 5 опять появляется импульс, производя щий запись очередного байта информации в блок 10 буферной памяти.Одновременно с записью принимаемой информации в блок 10 буферной памяти производится подсчет контрольной последовательности блоком 18. После дешифра.ции Флага закрываюшего на втором выходе блока 11 дешифраторов появляется импульс, сбрасывающий четвер. тый триггер 12 и третий 8 триггеры в...

Устройство для сопряжения эвм с абонентами

Номер патента: 1411760

Опубликовано: 23.07.1988

Авторы: Мельниченко, Степанова, Тараев, Шестакова

МПК: G06F 13/00

Метки: абонентами, сопряжения, эвм

...образом.ЭВМ через элементы 2 - 7 и 18 22 обращается к блоку 8 памяти по первому каналу для записи (режим "Вывод 1) или чтения (режим Ввод") информации независимо от работы абонентов согласно требованиям выполняемой программы по временной диаграмме обмена, приня. ой для конкретной ЭВМ и канала связи (фиг, 5).В то же время абоненты 17, рабо" тающие циклически по своим внутренним временным диаграммам, считывают и записывают информацию в блок 8 памяти по второму каналу обмена в интервале времени, отведенные для каждого абонента в соответствии со стробируюшими сигналами, вырабатываемыми блоком 16 (фиг. 2). Каждый абонент обменивается с блоком 8 памяти по временной диаграмме (фиг, 3). Адреси информация подключаются на входблока 8 памяти...

Устройство управления памятью

Номер патента: 1411761

Опубликовано: 23.07.1988

Авторы: Гвинепадзе, Мыскин, Плюснин, Торгашев, Чугунов

МПК: G06F 13/00

Метки: памятью

...формата с выходов сумматоров 42 и 43 переписываются по синхросигналу с входа 6.4 соответственно. в группу 48 текущих адресов и группу 49 форматов регистровой памяти, т.е. в регистровой памяти подготавливается адрес следующего слова информации, записываемой в ОЗУ из канала. Как видно на диаграмме (фиг,9), прием и запись слова информации из канала осуществляется за 2 цикла работы устройства. В третьем цикле поступает из канала следующее слово информации с сигналом сопровождения, в четвертом осуществля ется его запись в ОЗУ по модифицированному адресу с одновременной подготовкой адреса следующего слова и т,д., пока не будет принято в ОЗУ последнее слово страницы информации .из канала, При этом канал ввода снимает сигнал запроса на ввод...

Устройство для сопряжения эвм с каналами связи

Номер патента: 1411762

Опубликовано: 23.07.1988

Авторы: Малыхин, Шишков, Щербаков

МПК: G06F 13/00

Метки: каналами, связи, сопряжения, эвм

...слово (Нсь г 1 рю Начало слова Н , еслиРазряд содержит "1", если Р НО 1 З о- о 1-1,Разряд содержит "О" если Рних и сигнал Готово . ЭВМ записывает это слово в свою память и запрашивает содержимое другой ячейки ит.д. пока не считает весь необходимый ей массив информации. После этого ЭВМ по шине 14 адреса дает команду "Конец обмена", по которой снимается команда "Начало обмена" и устройство переходит в режим приема, записи информации в блок 7 и перезаписи ее в блок 8, Во время обмена информацией с ЭВМ для информация, поступаемая в это время иэ каналов, принимается и записывается в блок 7. Формула изобретенияУстройство для сопряжения. ЭВМ сканалами связи, содержащее преобразователь биполярного кода в однополяр"алый, входы которого...

Устройство для сопряжения эвм с микропроцессором

Номер патента: 1411763

Опубликовано: 23.07.1988

Авторы: Гаркавенко, Игнатуша, Якименко

МПК: G06F 13/00

Метки: микропроцессором, сопряжения, эвм

...в режим передачи35данных к ЭВМ, а блок 4 приемопередатчиков - в режим приема информации от микропроцессора. Работа этого блока разрешается сигналом "Устройство выбрано". По сигналам "Ввод" 40и А 01 - 03 шифратор 5 выставляетсигналы адресации СБСР 1, СБСР 2, СБ 1СБ 2, МАО СР и сигнал разрешения чтения "Чтение УВВ",При наличии сигналов адресации 45и,Чтение УВВ",происходит чтение информации от микропроцессораЭта информация поступает через блок 4приемопередатчиков по шинам ДО - 7в блок 1 приемопередатчиков, которыйвыставляет эту информацию в каналЭВМ. Одновременно с задержкой относительно сигнала "К ввод Н" дешифратор 2 управляющих сигналов формируетсигнал К СИП Н, который извещаетЭВМ, что информация выставлена в канал.Одновременно с...

Устройство для сопряжения эвм с магистралью локальной сети

Номер патента: 1411764

Опубликовано: 23.07.1988

Авторы: Иванов, Петросов, Сирбиладзе

МПК: G06F 13/14

Метки: локальной, магистралью, сети, сопряжения, эвм

...образом,После того как ведущая ЭВМ 1 заняла магистраль, выполняется выборка иосуществление связи с ведомой ЭВМ 1.Выборка ведомой ЭВМ 1 осуществляетсяпередачей от ведущей ЭВМ 1 по шине 5строба, длительность которого определяет номер ведомой ЭВМ. Указанныйстроб дешифруется в той ЭВМ 1 , скоторой ведущей ЭВМ 1 необходимо выполнить обмен, ПрОцедура заключаетсяв следующем,Ведущая ЭВМ 1 выдает в устройство4 информацию о длине строба генерации в виде двоичного кода. Эта информация поступает на входы элементовИ группы 23, открытых в этот моментвыходным сигналом дешифратора 17.С выходов элементов И группы 23 информация о длине строба параллельнымкодом через группу 33 элементов ИЛИпоступает на входы счетчика 39. Ука-,занный выходной сигнал...