Устройство для формирования сигналов прерывания при отладке программ

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1411755

Авторы: Богданова, Будовский, Бурковский, Гольдберг

Текст

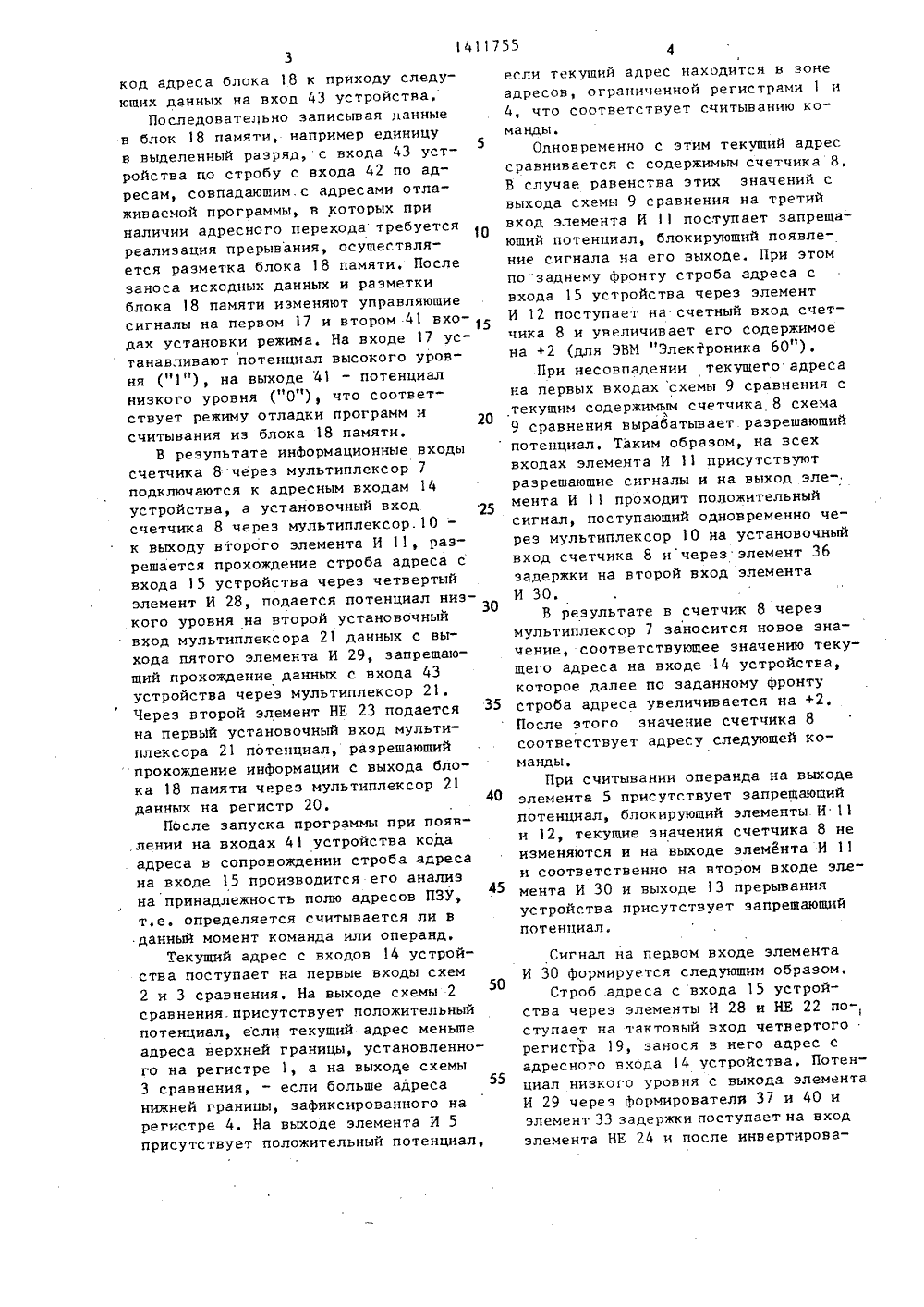

,80 11755 51)4 С ОС ПИСАНИЕ ИЗОБРЕТЕНИВТОРСНОМУ СВИДЕТЕЛЬСТВУ иистносится к в и может быть АРСТВЕННЫЙ НОМИТЕТ СССРЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ(56) Авторское свидетельство СССРУ 962945, кл. С 06 Р 11/28, 1980.Авторское свидетельство СССРВ 1348841, кл. С 06 Р 11/28, 1986,(54) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯСИГНАЛОВ ПРЕРЫВАНИЯ ПРИ ОТЛАДКЕПРОГРАММ(57) Изобретение оьлительной техникеиспользовано при отладке программ специализированных систем реальноговремени. Целью изобретения являетсясокращение времени отладки программ.Устройство для формирования сигналовпрерывания при отладке программ содержит четыре регистра 1,4,6 и 20;три схемы 2,3.и 9 сравнения; шестьэлементов И 5,11,12 и 28 - 30; мультиплексор 7 адреса; два счетчика 19и 8; мультиплексор 10 записи; блок18 памяти, мультиплексор 21 данных;четыре элемента НЕ 22 - 25; два элемента ИЛИ-НЕ; шесть элементов 3136 задержки; четыре формирователя37 - 40 длительности. 1 ил.Изобретение относится к вычислительной технике, может быть использовано при отладке программ специализированных систем (СЦВС) реального времени и является усовершенствованием устройства по авт. св. У 1348841.Цель изобретения - сокращение времени отладки программ.На чертеже представлена схема устройства для формирования сигналов прерывания при отладке программ,Устройство содержит первый регистр 1, первую 2 и вторую 3 схемы . сравнения, второй регистр 4, первый элемент И 5, четвертый регистр б, мультиплексор 7 адреса, второй счетчик 8, третью схему 9 сравнения, мультиплексор 10 записи, второй 11 и шестой 12 элементы И, второй выход 13 прерывания, адресный вход 14, вход 15 строба адреса, вход 16 на" чальной установки, первый вход 17 установки режима, блок 18 памяти, первый счетчик 19, третий регистр 20, мультиплексор 21 данных, первый 22, второй 23, третий 24 и четвертый 25 элементы НЕ, первый 26 и второй 27 элементы ИЛИ-НЕ, третий 28, четвертый 29 и пятый 30 элементы И, первый 31, второй 32, третий ЗЗ, четвертый 34, пятый 35 и шестой 36 элементы задержки, первый 37, второй 38, .третий 39 и четвертый 40 формирователи длительности, второй вход 14 .установки режима, вход 42 строба данных, вход 43 даннык и первый выход 44 прерывания.Работа устройства начинается с установки исходных данных в региСтры 1,4 и 6 и счетчик 19 и разметки блока 18 памяти. На регистрах 1 и 4 устанавливаются верхняя и нижняя граница области памяти ЭВИв отведен-, .ной для хранения команд, на регистре б - начальный адрес отлаживаемой программы, а на счетчике 19 - начальный адрес блока 18. Загрузка резисторов 1,4 и 6 может выполняться с лицевой панели устройства или в простейшем варианте они могут быть выполнены в виде тумблерных наборников на лицевой панели устройства.В режиме загрузки исходных данных на первом выходе 17 установки режима устанавливается на уровень логического "0", а на втором входе 41 установки режима - уровень логической 2"1", что соответствует режиму записи в блок 18 и вводу начального адреса программы в счетчик 8.С входа 17 устройства на управляющие входы мультиплексоров 7 и 10 поступает управляющий потенциал, соответствующий вводу начального адреса с регистра 6 через мультиплексор 7 в счетчик 8 под управлением сигнала, поступающего с входа 16 устройства через мультиплексор 10 на установочный вход счетчика 8, Одновременно сигнал с входа 16 устанавливает счетчик 19 в начальное (нулевое) состояние. На входы 43 и 42 устройства подаются от внешнего устройства соответственно данные для записи в блок 18 памяти и сопровождаюший их строб данных. Строб данных через элемент И 29 проходит на уста" новочный вход мультиплексора 21, разрешая прохождение данных с входа 43 устройства через мультиплексор 21 на вход регистра 20, Кроме того, ,сигнал с выхода элемента И 29 после формирования по длительности формирователем 37 через второй элемент ИЛИНЕ 27 поступает на тактовый вход регистра 20, осуществляя занос в регистр данных с входа 43 устройства.Сигнал с выхода формирователя 37после задержки на элементе 33 необходимый для обеспечения записи дан-.нык в регистр 20, формируется по длительности на формирователе 40 и через элемент НЕ 24 поступает отрицательным сигналом на режимный вход записи блока 18. Одновременно сигнал 40с выхода формирователя 40 после за" держки на четвертом элементе 35 задержки на время, определяемое требованиями временной диаграммы блока 18 памяти, через первый элемент ИЛИ-НЕ 26 .отрицательным сигналом поступает на вход опроса блока 18 памяти. В результате сигнальв на входах опроса и записи обеспечивают запись данных с регистра 20 по адресу, установленному на счетчике 19., При этом сигнал с выхода элемента 35 задержки после задержки на четвертом элементе 34 задержки на время, необходимое для записи информации в блок 18 памяти, через четвертый элемент НЕ 25 поступает на счетный вход счетчика 19, увеличивая его содерилмоевв ввна 1 , таким образом подготавливая1411755если текущий адрес находится в зонеадресов, ограниченной регистрами 1 ичто соответствует считыванию команды.Одновременно с этим текущий адрессравнивается с содержимым счетчика 8В случае равенства этих значений свыхода схемы 9 сравнения на третийвход элемента И 11 поступает запреща-ющий потенциал, блокирующий появление сигнала ча его выходе. При этомпо"заднему фронту строба адреса свхода 15 устройства через элементИ 12 поступает на счетный вход счетчика 8 и увеличивает его содержимоена +2 (для ЭВИ "Электроника 60").При несовпадении текущего адресана первь 1 х входах схемы 9 сравнения стекущим содержимым счетчика 8 схемаЪ9 сравнения вырабатывает разрешающийпотенциал, Таким образом, на всехвходах элемента И 11 присутствуютразрешающие сигналы и на выход эле"мента И 11 проходит положительныйсигнал, поступающий одновременно через мультиплексор 10 на установочныйвход счетчика 8 ичерез элемент 36задержки на второй вход элементаИ 30.В результате н счетчик 8 черезмультиплексор 7 заносится новое значение, соответствующее значению текущего адреса на входе 14 устройстна,которое далее по заданному фронту35 строба адреса увеличивается на +2.После этого значение счетчика 8соответствует адресу следующей команды.При считывании операнда на выходеэлемента 5 присутствует запрещающийпотенциал, блокирующий элементы. И 11и 12, текущие значения счетчика 8 неизменяются и на выходе элемента И 11и соответственно на втором входе элемента И 30 и выходе 13 прерыванияустройства присутствует запрещающийпотенциал. код адреса блока 18 к приходу следующих данных на вход 43 устройства,Последовательно записывая данные в блок 18 памяти, например единицу в выделенный разряд, с входа 43 устройства цо стробу с входа 42 по адресам, совпадаюшим.с адресами отлаживаемой программы, в которых при наличии адресного перехода требуется реализация прерывания, осуществляется разметка блока 18 памяти. После заноса исходных данных и разметки блока 18 памяти изменяют управляющие сигналы на первом 17 и втором 41 входах установки режима, На входе 17 ус тананливают потенциал высокого уровня ("1"), на выходе 41 - потенциал низкого уровня ("0"), что соответствует режиму отладки программ и считывания из блока 18 памяти.В результате информационные входы счетчика 8 через мультиплексор 7 подключаются к адресным входам 14 устройстна, а установочный вход счетчика 8 через мультиплексор.10 - к выходу второго элемента И 11, разрешается прохождение строба адреса с входа 15 устройства через четвертый элемент И 28, подается потенциал низкого уровня на второй установочный вход мультиплексора 21 данных с выхода пятого элемента И 29, запрещающий прохождение данных с входа 43 устройства через мультиплексор 21, Через второй элемент НЕ 23 подается на первый установочный вход мультиплексора 21 потенциал, разрешающий прохождение информации с выхода блока 18 памяти через мультиплексор 21 данных на регистр 20.ПОсле запуска программы при появ.лений на входах 41 устройства кода адреса в сопровождении строба адреса на входе 15 производится его анализ на принадлежность полю адресов ПЗУ, т.е. определяется считывается ли в данный момент команда или операнд,Текущий адрес с входов 14 устройства поступает на первые входы схем 2 и 3 сравнения, На выходе схемы 2 сравнения. присутствует положительный потенциал, если текущий адрес меньше адреса верхней границы, установленного на регистре 1, а на выходе схемы 3 сравнения, - если больше адреса нижней границы, зафиксированного на регистре 4. На выходе элемента И 5 присутствует положительный потенциал,Сигнал на первом входе элемента И 30 формируется следующим образом,Строб .адреса с входа 15 устройства через элементы И 28 и НЕ 22 по 1 ступает на тактонь 1 й вход четвертого регистра 19, занося в него адрес с адресного входа 14 устройства. Потенциал низкого уровня с выхода элемента И 29 через формирователи 37 и 40 и элемент 33 задержки поступает на вход элемента НЕ 24 и после иннертирова1411755 вания информации из блока 18 памятина первый вход элемента И 30. формула изобретения Составитель И, игаловТехред М,Дидык Корректор В, ГирнякЬ Редактор П, Гереши Заказ ЗббЗ/45 Тираж 704 ПодписноеВНИИПИ Государственного комитета СССРпо делам изобретений и открытий113035, Москва, Ж, Раушская наб д, 4/5 Производственно-полиграФическое предприятие, г, Ужгород, ул. Проектная, 4 ния передается на вход записи блока 18 памяти.Положительный сигнал с выхода элемента И 28 задерживается на эле 5 менте 3 задержки на время, необхо,димое для записи в счетчик 19 адреса с входа 14 устройства, и после Формирования по длительности на Формирователе 38 через элемент ИЛИ-НЕ 2 б отрицательным импульсом поступает ,на вход опроса блока 18 памяти, Сочетание потенциала высокого уровня на входе записи и отрицательного сигнала на входе опроса блока 18 па,мяти соответствует режиму считывания информации иэ блока 18 памяти на ,первый информационный вход мульти"плексора 21. Так как на первом установочном входе мультиплексора 21 в ,режиме считывания присутствует разрешающий потенциал, информация проходит через мультиплексор 21 на вход регистра 20. При этом сигнал с выхода элемента И 28 задер б кивается элементом 32 задержки на Время, необходимое для считывания ин 1 рормации из блока 18 памяти, Формиру,ется по длительности наформироватеЙе 39 и через элемент ИЛИ-НЕ 27 поступает на тактовый вход регистра. 20, обеспечивая занос в него информации чз блока 18 памяти.Если по адресу, присутствующему на адресном входе 14 устройства, из35 определенного разряда блока 18 памя 1 ги в регистр 20 и далее на первый ход элемента И 30 поступает и" (занесенная по указанному адресу в режиме разметки блока 18 памяти), то , Ори появлении сигнала на втором входе элемента И 30 на цыходе 44 устройства появляется сигнал прерывания.При, этом элемент 36 задержки обес.печивает задержку сигнала ча втором :Зходе элемента И 30 на время считыУстройство для формирования сигналов прерывания при отладке программ по авт. св, В 1348841, а т л и ч аю ш е е с я тем, что, с целью сокращения времени отладки программ, в устройство введены четвертый регистр, второй счетчик, третья схема сравнения, шестой элемент И, мультиплексор адреса и мультиплексор записи, причем выход четвертого регистра соединен с первым информационным входом мультиплексора адреса, адресный вход устройства соединен с входом первого сравниваемого числа, третьей схемы сравнения и с вторым информационным входом мультиплексора адреса, выход которого соединен с информационным входом второго счетчика, первый вход установки режима устройства соединен с управляющими входами мультиплексора адреса и мультиплексора записи, выход которого соединен с установочным входом второго счетчика, выход которого соединен с входом второго сравниваемого числа третьей схемы сравнения, выход которой соединен с третьим входом второго элемента И, выход второго элемента И является вторым выходом прерывания устройства и соединен с первым информационным входом мультиплексора записи, вход начальной установки устройства соединен с вторыминформационным входом мультиплексора записи, выход первого элемента И соединен с первым входом шестого элемента И, выход ко" торого соединен со счетным входом второго счетчика, вход строба адреса устройства соединен с вторь 1 м входом шестого элемента И.

СмотретьЗаявка

4095628, 24.07.1986

ПРЕДПРИЯТИЕ ПЯ Г-4152

БУРКОВСКИЙ ИГОРЬ ВЛАДИМИРОВИЧ, БУДОВСКИЙ ЯКОВ МОИСЕЕВИЧ, БОГДАНОВА КИРА ВИКТОРОВНА, ГОЛЬДБЕРГ ИКАР ВЕНИАМИНОВИЧ

МПК / Метки

МПК: G06F 11/28

Метки: отладке, прерывания, программ, сигналов, формирования

Опубликовано: 23.07.1988

Код ссылки

<a href="https://patents.su/4-1411755-ustrojjstvo-dlya-formirovaniya-signalov-preryvaniya-pri-otladke-programm.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для формирования сигналов прерывания при отладке программ</a>

Предыдущий патент: Устройство для контроля логических блоков

Следующий патент: Устройство адресации памяти

Случайный патент: Способ сгущения суспензий