Устройство для сопряжения эвм с микропроцессором

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1411763

Авторы: Гаркавенко, Игнатуша, Якименко

Текст

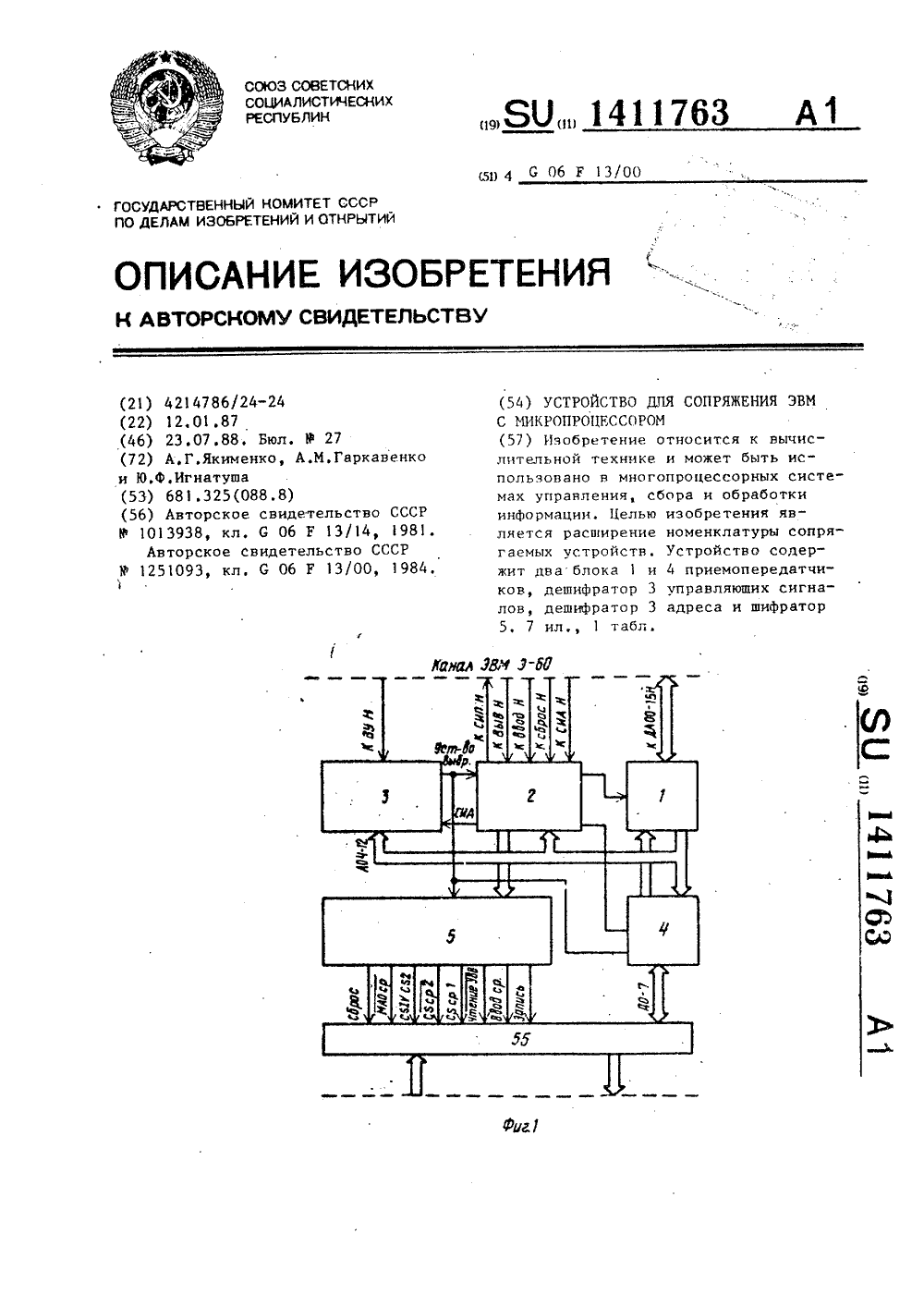

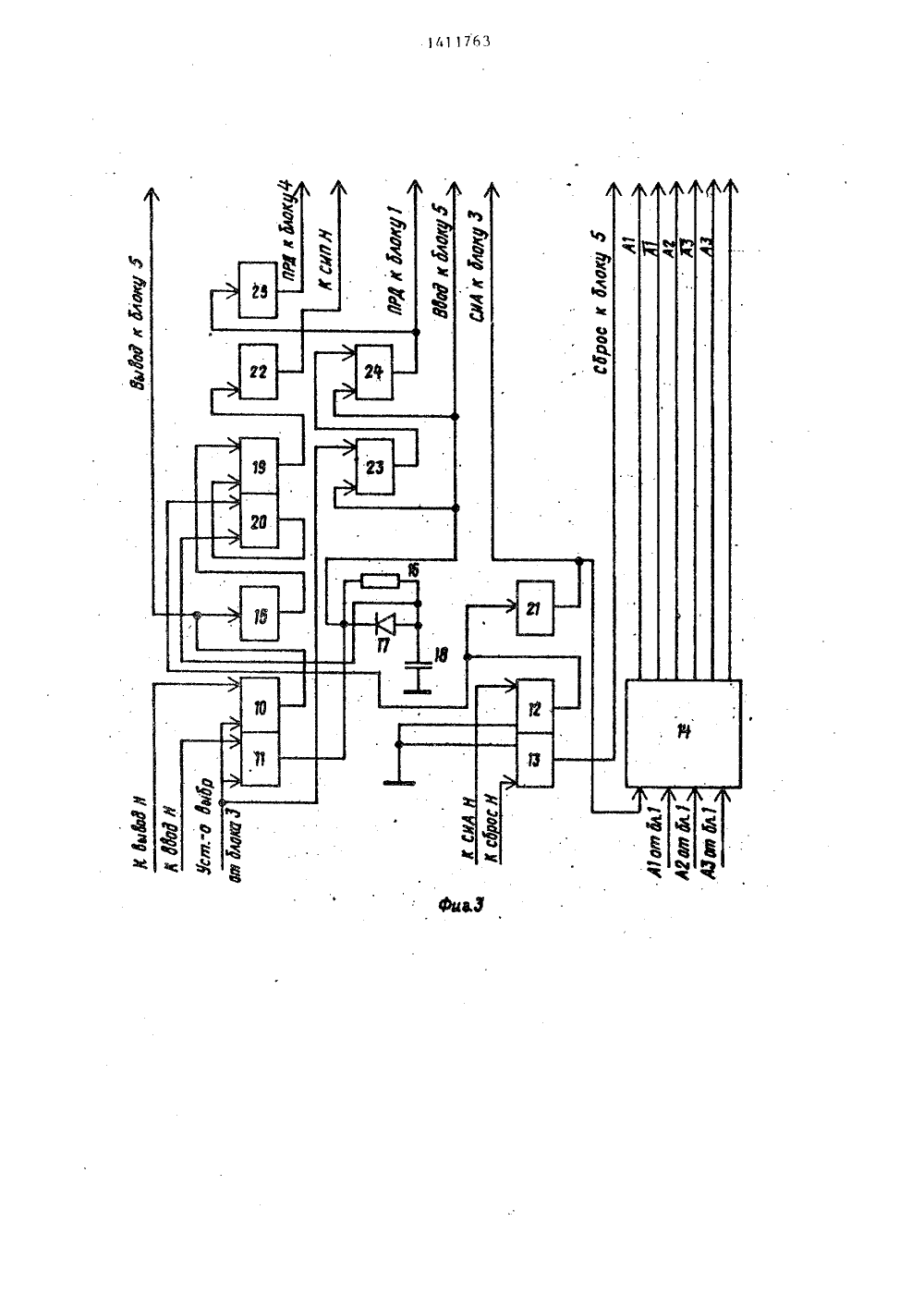

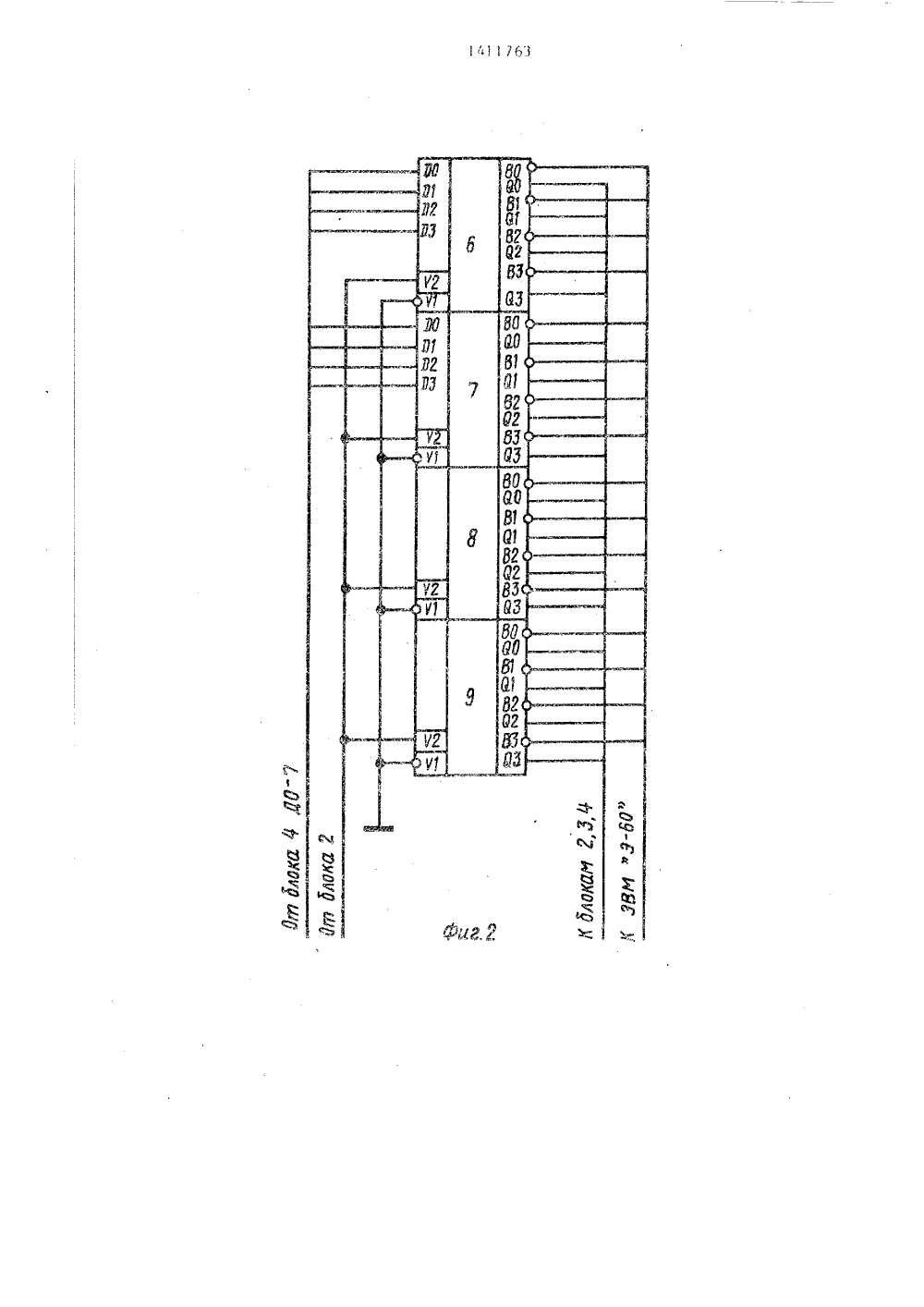

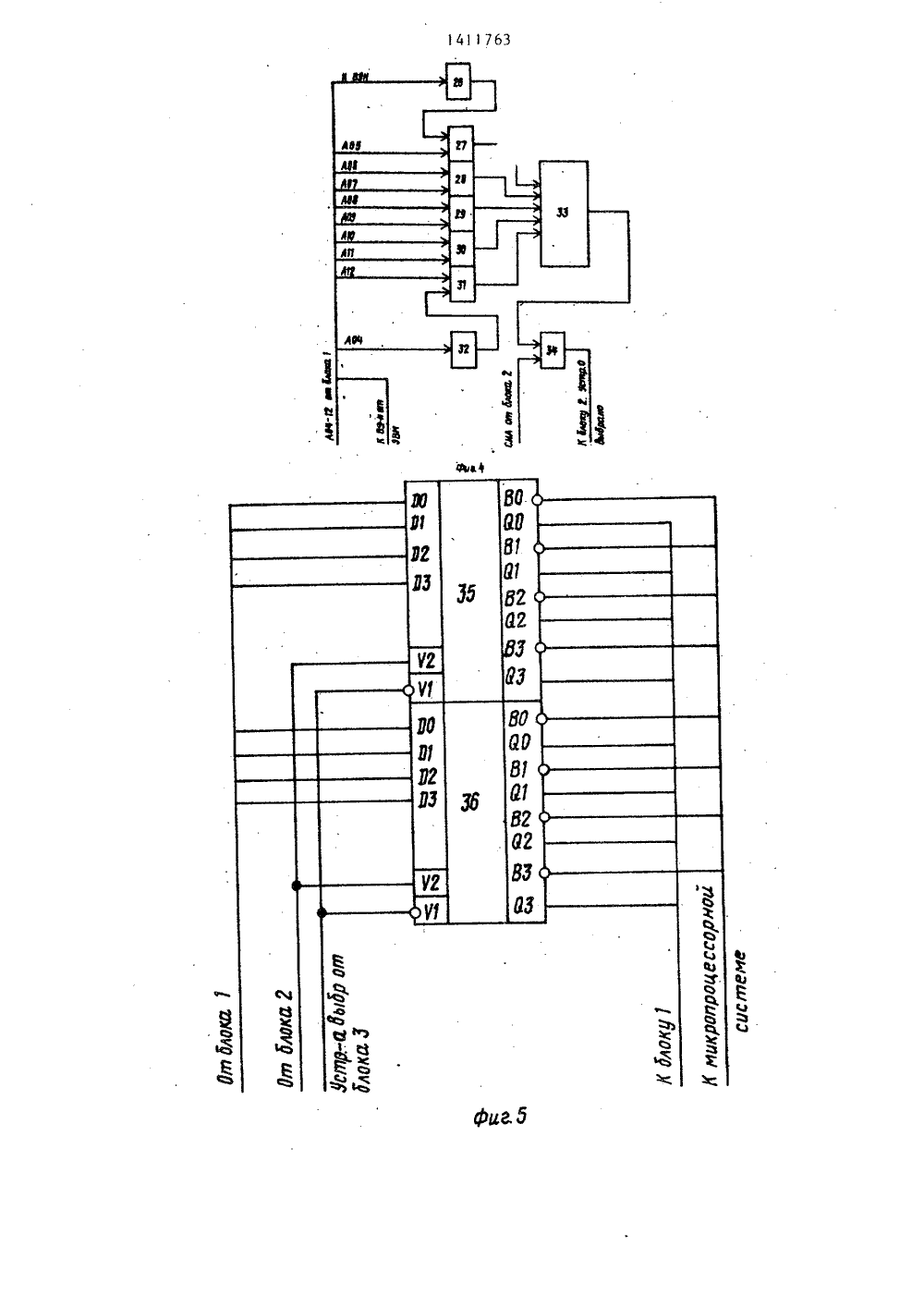

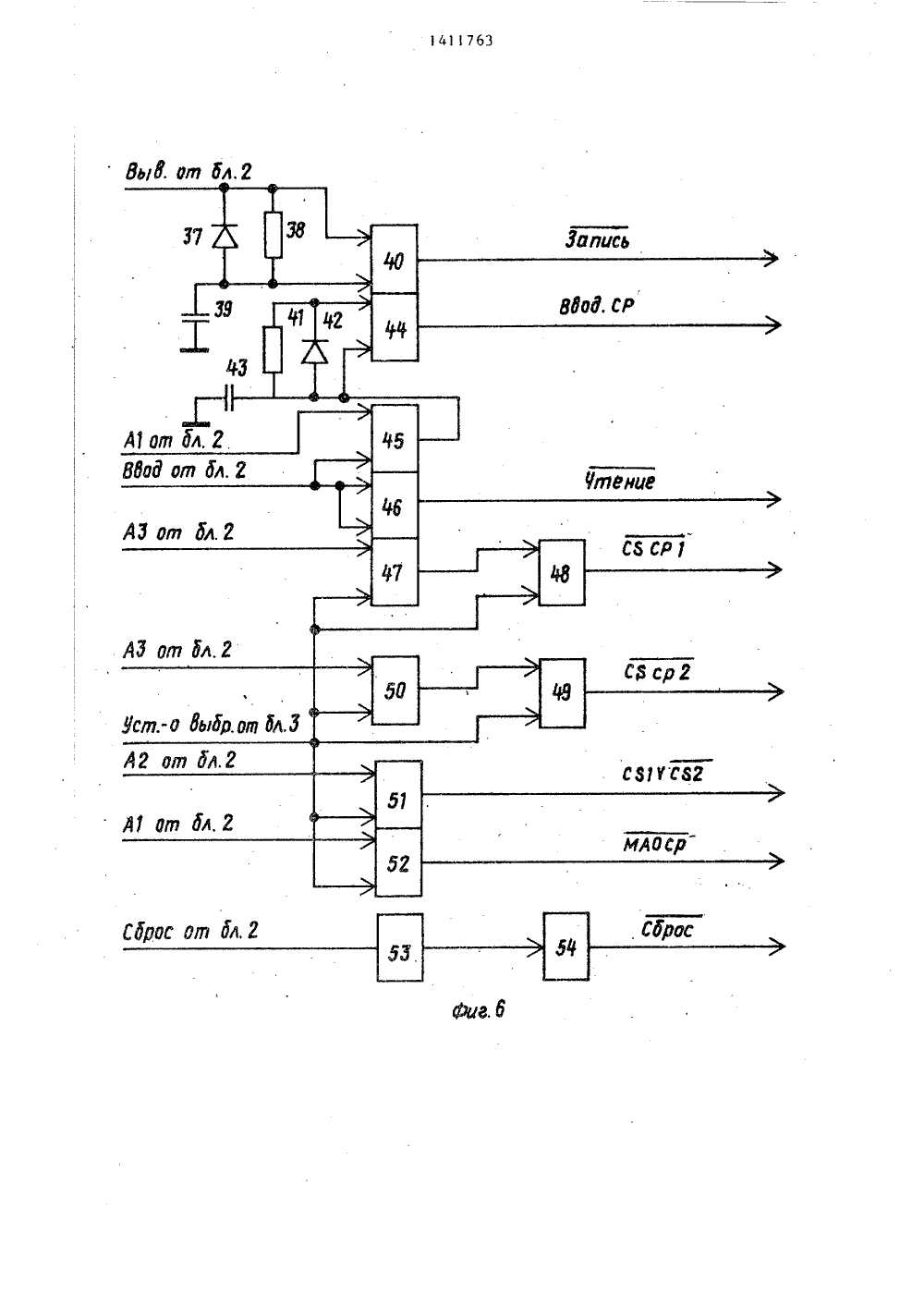

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХ 191 11 163 СПУБЛИК л) 4 С 06 Р 13/ САНИЕ ИЗОБРЕТОРСКОМУ СВИДЕТЕЛЬСТВУ Я СОПРЯЖЕНИЯ ЭВМ к вычис рных систработкиния явтуры сопря во содер- передатчиших сигнаши ратор Гадал 38 м ОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ(56) Авторское свидетельство СССРВ 101 3938, кл. С 06 Р 3/14, 1981.Авторское свидетельство СССРУ 1251093, кл. С 06 Р 13/00,984,(54) УСТРОЙСТВО ДЛЯС МИКРОПРОЦЕССОРОМ(57) Изобретение относитслительной технике и можетпользовано в многопроцессмах управления, сбора и оинформации, Целью изобретляется расширение номенклгаемых устройств. Устройсжит два блока 1 и 4 приемков, дешифратор 3 управляюлов, дешифратор 3 адреса5. 7 ил 1 табл,1411763к микропроцессору, но они не выбраны. Выбираются приемо-передатчикисигналом Устройство выбрано". В режим приема информации от микропро 5 цессора приемопередатчики переводятся сигналом ПРД.Шифратор 5 (фиг. 6) формируетсигналы, управляющие обменом информации, и содержит диод 37, резистор38, конденсатор 39, элемент И-НЕ 40,резистор 41, диод 42, конденсатор 43,элементы И-НЕ 44 - 52, ждущий мультивибратор 53 и элемент НЕ 54, Переченьи. назначение сигналов интерфейса приведены в таблице,Обмен информацией между ЭВМ и мик 1 ропроцессором осуществляется байтамис опросом готовности. Показанный на1 Фиг, 1 блок 55 связи в состав устройства не входит. Сигнал Назначение МДО-МД 7 Информация"Ввод СР"СЯСР 1 Подтверждает что инФормация принята ЭВМ СБСР 2-С 81 чСЯ 2 МАО СР"Сброс" разом. Изобретение относится к вычислительной технике и может быть использовано в многопроцессорных системах управления, сбора и обработки информации.Цель изобретения - расширение номенклатуры сопрягаемых устройств,На Фиг, 1 приведена структурная схема устройства для сопряжения ЭВМ с микропроцессором; на фиг. 2 - схема первого блока приемопередатчиков на Фиг. 3 - схема дешифратора управляющих сигналов; на Фиг. 4 - схема дешифратара адреса; на фиг. 5 - схема второго блока приемопередатчиков нафиг, 6 - схема шифратора; на фиг. 7 - временные диаграммы работь устройства в режимах ввода и выводаУстройство содержит первый блок приемопередатчиков, дешифратор 2 управляющих сигналов, дешифратор 3 адреса, второй блок 4 приемопередатчиков и шифратор 5.Первый блок 1 приемопередатчиков (Фиг. 2) предназначен для приема или передачи информации в канал ЭВМ и состоит из четырех многоканальных приемопередатчиков 6 - 9. Эти приемопередатчики находятся в режиме приема информации от ЭВМ (режим Выл 3 О вод"), В режим выдачи информации в ЭВМ из микропроцессора приемопередатчики переводятся сигналом ПРД.Дешифратор 2 управляющих сигналов (фиг. 3) производит дешифрацию команд 35 и Формирует соответствующие управляющие сигналы. Дешифратор содержит элементы ИЛИ-НЕ 10 - 13, регистр 14, элемент НЕ 15, резистор 16, диод 17, конденсатор 18, элементы И-НЕ 19 и 40 20, НЕ 21, И-НЕ 22 - 24 и НЕ 25.Дешифратор 3 адреса (фиг, 4) производит дешифрацию адресов при обмене информацией и содержит элементы НЕ 26, И 27 - 31, НЕ 32 и И-НЕ 33 45 и Э-триггер 34, На входы дешифратора поступают адресные сигналы А 04 12, канальный сигнал К ВУ Н и сигнал синхронизации СИА, При совпадении поступающего адреса с адресом уст ройства сопряжения дешифратор выставляет сигнал "устройство выбрано".Второй блок 4 (Фиг, 5) приемо- передатчиков предназначен для приема или передачи информации в канал мик ропроцессора и состоит из двух магистральных нриемопередатчиков 35 и 36. Эти приемопередатчики находятся в режиме передачи информации Сигнализирует микропроцессору, что на шинахМДО-МД 7 находится информация При чтении информации из микропроцессора пе" реводит приемопередатчики блока связи в режим передачи информа- ции Адресуют один из микропроцессоров, с. которым в данный момент обменивается информацией ЭВМ Выборка в блоке связиприемопередатчика данных или приемопередатчика служебного байта Сбрасывает внешние уст;ройства Устройство работает следующим об 141173Устройство обеспечивает работув режимах Вв од и Вывод" .В режиме Ввод (временная диаграмма, фиг. 7) информация передается иэ микропроцессора в ЭВМ. 5Порядок выполнения операций следующий. ЭВМ в адресной части передает по линиям К ДА (00 - 15) Н вблок 1 (фиг. 1) приемопередатчиковадрес устройства сопряжения, а такжесигнал К ВУ Н в дешифратор 3 адреса,Дешифратор 3 адреса дешифрирует принятую информацию (А 04 - 12) и выраба.тывает сигнал "Устройство выбрано",через 150 нс после выдачи адреса вырабатывается сигнал К СИА Н, по переднему фронту которого сигнал "Устройство выбрано" запоминается в дешифраторе 3 адреса на время действиясигнала К СИА Н, а в дешифраторе 2управляющих сигналов запоминаютсязначения сигналов А 01 - 03, Послеэтого ЭВМ снимает информацию с линийК ДА (00 - 15)Н, очищает линиюК ВУ Н и выставляет в дешифратор 2управляющих сигналов сигнал"К ввод Н", сигнализируя о том, чтоЭВМ готова принять информацию от"К ввод Н", "Устройство выбрано",формирует сигналы "Ввод", АО - 03и ПРД, который переводит блок 1 приемопередатчиков в режим передачи35данных к ЭВМ, а блок 4 приемопередатчиков - в режим приема информации от микропроцессора. Работа этого блока разрешается сигналом "Устройство выбрано". По сигналам "Ввод" 40и А 01 - 03 шифратор 5 выставляетсигналы адресации СБСР 1, СБСР 2, СБ 1СБ 2, МАО СР и сигнал разрешения чтения "Чтение УВВ",При наличии сигналов адресации 45и,Чтение УВВ",происходит чтение информации от микропроцессораЭта информация поступает через блок 4приемопередатчиков по шинам ДО - 7в блок 1 приемопередатчиков, которыйвыставляет эту информацию в каналЭВМ. Одновременно с задержкой относительно сигнала "К ввод Н" дешифратор 2 управляющих сигналов формируетсигнал К СИП Н, который извещаетЭВМ, что информация выставлена в канал.Одновременно с задержкой относительно сигнала "К ввод Н" шифратор 5 63формирует сигнал "Ввод СР", извещающий микропроцессор, что информацияпринята ЭВМ. ЭВМ принимает сигналК СИП Н, принимает данные с каналаи снимает сигнал К ввод". Дешифратор 2 управляющих сигналов снимаетсигнал К СИП Н, завершая передачуданных, ЭВМ по заднему фронтуК СИП Н снимает сигнал К СИА Н, завершая канальный цикл "Ввод.В режиме Вывод (временные диаграммы, фиг. 7) информация передается.из ЭВМ в микропроцессор.ЭВМ выставляет на линии К ДА(00 - 15) Н адрес устройства сопряжения и сигнал К ВУ Н. Дешифратор 3(фиг, 1) адреса дешифрирует информацию и вырабатывает сигнал "Устройство выбрано". Через 150 нс после выдачи адреса ЭВМ вырабатывает сигналК СИА Н, по переднему фронту которого запоминаются значения сигналовАО - 03 и "Устройство выбрано",который разрешает работу дешифратора 2 управляющих сигналов и блока 4.приемопередатчиков данных,ЭВМ снимает адрес, очищает линиюК ВУ Н, после чего помешает данныена линии К ДА (00 - 07) и через100 нс выдает сигнал К вывод . Дешифратор 2 управляющих сигналов, приняв сигналы К СИА Н, К вывод, Устройство выбрано", формирует сигналы"Вывод", АО - 03 и ПРД. Сигнал ПРДпереводит блок 1 приемопередатчиковв режим приема данных из ЭВМ, а блок4 приемопередатчиков - в режим передачи данных в микропроцессор, По сигналам "Вывод" и АО - 3 шифратор 5выставляет сигналы адресации С СР 1,С СР 2, С 1 С 2, МАО СР и сигнал "Запись УВВ", который, извещает блок 55связи, что на шинах МДО - 7 находит-,ся информация.При наличии сигналов адресации и"Запись УВВ" происходит запись информации в микропроцессор. Дешифратор 2 управляющих сигналов посылаетв ЭВМ сигнал К СИП Н, означающий,что данные приняты устройством длясопряжения, ЭВМ, получив сигналГК СИП Н, очищает через 150 нс линию"К вывод", а через 250 нс после получения сигнала К СИП Н ЭВМ снимаетданные с линий К ДА (00 - 07) Н.Устройство для сопряжения снимаетсигнал К СИП Н, а ЭВМ снимает сигнал К СИА Н, завершая тем самымцикл вывода51411В предлагаемом устройстве обмен между ЭВМ и микропроцессором происходит по инициативе ЭВМ. Обмен начинается с анализа служебного байта, в котором содержится информация, чтоВ микропроцессор готов передавать или принимать информацию, Проанализировав его, ЭВМ переходит в режим приема либо в режим выдачи информации, 10 Формула изобретенияУстройство для сопряжения ЭВМ с .микропроцессором, содержащее дешифратор адреса, дешифратор управляющих сигналов, первый блок приемопередатчиков, причем информационный вход дешифратора адреса является входом устройства для подключения к выходу выборки ЭВ 1, группа информационныхlвходов-выходов первого блока приемо- передатчиков образует группу входов- выходов устройства для подключения к группе информационных и адресных входов-выходов ЭВМ, первый, второй, тре- рб тий и четвертый информационные входы и первый выход дешифратора управляющих сигналов являются входами и выходом устройства для подключения соответственно к выходам ввода, вы- З 0 вода, установки, синхронизации и к входу синхронизации ЭВМ, при этом группа старших разрядов информационного выхода первого блока приемопередатчиков соединена с группой информа 35 ционных входов дешифраторов управляющих сигналов, группа младших разрядов информационного выхода первого блока приемопередатчиков соединена с группой информационных входов дешиф 763 ратора адреса, второй и третий выходы дешифратора управляющих сигналовсоединены соответственно-с входом ре"жима работы первого блока приемопередатчиков и синхровходом дешифратораадреса, о т л и ч а ю ш е е с я тем,что, с целью расширения номенклатуры сопрягаемых устройств, в неговведены шифратор и второй блок приемопередатчиков, причем первый - восьмой выходы шифратора являются выходами устройства для подключения соответственно к входам сброса, выборки, первому, второму и третьему адресным входам, входам чтения, подтверждения, записи микропроцессора,группа информационных входов-выходов второго блока приемопередатчиков образует группу, входов-выходовустройства для подключения к группеинформационных входов-выходов микропроцессора, при этом группа информационных выходов второго блока приемопередатчиков соединена с группойинформационных входов первого блокаприемопередатчиков, группа информационных выходов которого соединенас группой информационных входов вто"рого блока приемопередатчиков, вход.режима работы которого соединен счетвертым выходом дешифратора управляющих сигналов, разрешающий входкоторого соединен с выходом дешифратора адреса, с разрешающим входомвторого блока приемопередатчиков, сразрешающим входом шифратора, группаинформационных входов которого соединена с группой выходов дешифратора управляющих сигналов.1 41 1 163 Ии Аанюиг Упд Утюг Гежии ниИ" РЮМР 8 УИпЮ Жабий Составитель С. ПесталРедактор П. Гереши Техред М,Дидык Корректор С. Черни Заказ Эоб 3/45 Тираж 704 Подписное ВПИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская наб., д, 4/5

СмотретьЗаявка

4214786, 12.01.1987

ПРЕДПРИЯТИЕ ПЯ Р-6668

ЯКИМЕНКО АЛЕКСАНДР ГРИГОРЬЕВИЧ, ГАРКАВЕНКО АНАТОЛИЙ МИХАЙЛОВИЧ, ИГНАТУША ЮРИЙ ФИЛИПОВИЧ

МПК / Метки

МПК: G06F 13/00

Метки: микропроцессором, сопряжения, эвм

Опубликовано: 23.07.1988

Код ссылки

<a href="https://patents.su/9-1411763-ustrojjstvo-dlya-sopryazheniya-ehvm-s-mikroprocessorom.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для сопряжения эвм с микропроцессором</a>

Предыдущий патент: Устройство для сопряжения эвм с каналами связи

Следующий патент: Устройство для сопряжения эвм с магистралью локальной сети

Случайный патент: Способ изготовления сцинтилляционного детектора