Патенты с меткой «счисления»

Устройство для суммирования в избыточной системе счисления

Номер патента: 1290314

Опубликовано: 15.02.1987

Авторы: Евстигнеев, Евстигнеева

МПК: G06F 7/72

Метки: избыточной, системе, суммирования, счисления

...образуя группы 48-52 и 45-47.90314 4 г + 2 поступает на информационные входы соответствующих мультиплексоров (15- 17-1). Одновременно с шифраторами работают формирователь 10 сигналов переноса и блок 11 местного управления. Первый (10) формирует сигналы переноса Т. в старший г-й1разряд (-1, О, +1), а второй (11) на основе собственных сигналов переносас блока 10 и сигналов переноса т.;, с младшего г-го разряда формирует на своих выходах сигналы, управляющие выдачей на выходы мультиплексоров, (15-17-1) соответствующих результатов (см. табл.). 5 10 15 Формула изобретения Устройство для суммирования в избыточной системе счисления, содержащее группу из в матричных сумматоров по модулю Р, (3 =1,в,Р..ф , н основания системы остаточных...

Устройство для вычисления элементарных функций в модулярной системе счисления

Номер патента: 1291977

Опубликовано: 23.02.1987

МПК: G06F 7/544, G06F 7/72

Метки: вычисления, модулярной, системе, счисления, функций, элементарных

..., который черезинформационный вход группы мультиплексоров 15 поступает в регистр 19.На третьем такте блок 20, складывая содержимое регистров 8 и 19,находит величину М А + А Х посад ,гтупающую во входной регистр блока 21. 25На первый и второй входы блока 16 умноженйя с выходов групп мультиплексоров 12 и 13 поступают соответственно величины М и Х , подаваемые на информационный вход группы мультиплек- З 0соров 12 через вход 4 константы устройства и информационный вход группымультиплексоров 13 с выхода регистра9, блок 16 умножения находит модулярный код величины М Х , запоминаемой1в регистре 8.Из блока 7 памяти поступает константа А з, в управляющем регистре18 формируется управляющее слово садресом "3", а регистр 19 обнуляется.На четвертом...

Преобразователь позиционного кода из одной системы счисления в другую

Номер патента: 1302438

Опубликовано: 07.04.1987

Автор: Лебедев

МПК: H03M 7/12

Метки: другую, кода, одной, позиционного, системы, счисления

...числа в шестнадцатиричное и обратно В этом случае Б = 10, К = 16, ш = 2. В качестве шестнадцатиричных цифр используются двухразрядные десятичные числа 00, 0115.При переводе числа из десятичной системы счисления в шестнадцатиричную на вход 10 подается логический "О.". При этом константа, на которую производит умножение умножитель 7, равна 10, а работать умножитель 7 и сумма-тор 8 будут в шестнадцатиричной системе счисления.Перевод десятичного числа, например, 3875 осуществляется следующим образом.На выходах 4 элементов первой строки матрицы появятся деСятичные коды 02, 04, и 02. На выходе 5 последнего элемента первой строки матрицы поя- вится десятичный код 03,шестнадцати- ричной цифры числа шестнадцатиричных единиц содержащихся...

Устройство для преобразования чисел из позиционной системы счисления в модулярный код

Номер патента: 1305870

Опубликовано: 23.04.1987

Авторы: Акулинчев, Хлевной, Швецов

МПК: H03M 7/18

Метки: код, модулярный, позиционной, преобразования, системы, счисления, чисел

...счисления в системуостаточных классов по произвольномумодулю. Элемент 19 задержки имеетвремя задержки 5 Т- среднеевремя переходных кроцессов в каждомотдельном функциональном элементеустройства , для 1 прощения понимания принципа работы устройства предполагают у всех элементов одинаковое . Счетчики 20 и 21 считают отединицы до ш+1 и и соответственно.Узлы 22 и 23 памяти содержат соответственно коды младших 10, Р - Ри старших (Р - Р ) модулей в порядке возрастания,Используется следующий принципработы,Преобразуемое число А, взятое изодиапазона К " П Р преобразуется1:1по модулю Р = 1,п, называемому старшим модулем, и после получения+каждого остатка 1 А 1 Р, он, в свою очередь, преобразуется по модулям РЭ1,н , которые называются младшими...

Устройство для сложения чисел с переменным основанием системы счисления

Номер патента: 1310809

Опубликовано: 15.05.1987

МПК: G06F 7/50, H03K 23/00

Метки: основанием, переменным, системы, сложения, счисления, чисел

...4 записывают результатсуммирования накопителя с числомА+Р, триггер 61 переключается в состояние "0", мультиплексоры 2 вновьначинают пропускать на выходы информацию со своих первых входов, процесс заполнения емкости памяти устройства с постоянным приращением,равным числу А, восстанавливается средняя частота заполнения двоичногонакопителя равнат А (2 Р. тАМ где Г - частота следования тактовыхтимпульсов.В частном случае при Р = О значение модуля равно величине емкости 4 п-разрядного устройства с модулем4 В двоично-десятичной системе счисления на вход 9 подан сигнал "1", коммутаторы 5, 5, блокируют сиг3 1310 нал, формируемый на их вторых входах, и пропускают сигналы, поступающие на их первые входы с выходов 2323...

Устройство для вычисления экспоненциальной функции в модулярной системе счисления

Номер патента: 1317433

Опубликовано: 15.06.1987

Авторы: Коляда, Кравцов, Селянинов, Чернявский

МПК: G06F 7/544, G06F 7/72

Метки: вычисления, модулярной, системе, счисления, функции, экспоненциальной

...с одновременной записью во входной регистр 5 через информационный вход информации с выхода второго элемента 13 задержки.Содержимое Ы группы из Ь младших 35 разрядов входного регистра 5 подаетсяна адресный вход блока 10 памяти для хранения констант, куда поступает 40также содержимое ) второго счетчика8, Из блока 10 памяти для храненияконстант считывается модулярный кодочередной константы У (см. (3.Блок 15 модульных умножителей выполняет операцию модульного умноженияоперандов, поступающих на его входыс вйходов блока 10 памяти для хранения констант и блока 11 мультиплексоров соответственно. Если управляющийсигнал 6 = О, то на выход блока 11мультиплексоров с первого информационного входа проходит величина М,поступающая с входа 4 константы...

Устройство для вычисления квадратного корня числа в модулярной системе счисления

Номер патента: 1317434

Опубликовано: 15.06.1987

Авторы: Амербаев, Коляда, Кравцов, Селянинов

МПК: G06F 7/552, G06F 7/72

Метки: вычисления, квадратного, корня, модулярной, системе, счисления, числа

...аргумента, номер которого определяется унитарным кодом,поступающим с выхода кольцевого счетчика 13 на выход 27 устройства. Вычисленное значение квадратного корняснимается с выхода блока 19 модульных сумматоров на выход 24 устройства, В случае завершения работы устройства по вычислению функции квадратного корня от всех входных аргументов соответствующий сигнал появляется на выходе 25 устройства,На первом такте работы устройства в первый регистр блока 9 регист 13 ров с входа 1 аргумента устройства поступает модулярный код числителя А значения А/р Маргумента, который также поступает на второй информационный вход блока 6 мультиплексоров, на управляющий вход которого поступает сигнал о =1, вслед 9 ствие чего с выхода блока 6...

Устройство для вычисления функций в модулярной системе счисления

Номер патента: 1322268

Опубликовано: 07.07.1987

Автор: Коляда

МПК: G06F 7/544, G06F 7/72

Метки: вычисления, модулярной, системе, счисления, функций

...(его значение н данный момент несущественно) с выхода сумматора 12 через второй информационный вход груп13222 В ходе третьего цикла (такты с де сятого по четырнадцатый) наряду с выполнением описанных действий в связи с выполнением третьего функционального значения в десятом такте сумматор 2, складывая содержимое регист 50 ра 18 с выходной величиной блока 7 элементов ИЛИ (на нулевом такте каждого цикла она равна нулю), получает модулярный код числа С (Х)У, который через второй информационный вход 55 группы мультиплексоров 16 передается в блок 17 масштабирования (ввидуб =о =О), умножитель 13 находит модулярный код произведения чисел С, (Х) пы мультиплексоров 16 передается в блок 17 масштабирования чисел.В ходе тактов с пятого по...

Устройство для сложения чисел в модулярной системе счисления

Номер патента: 1322278

Опубликовано: 07.07.1987

МПК: G06F 7/72

Метки: модулярной, системе, сложения, счисления, чисел

...регистра 23 сдвига принимает единичное значение. На втором такте рассматриваемой операции на управляющий вход блока 4 мультиплексоров устройства с четвертого выхода блока 7 управления подается сигнал б =1, поэтому содержимое второго входного регистра 13 (модулярный код числа+ В) через второй информационный вход блока 14 мультиплексоров устройства подается в блок 15 вычисления интервального13222индекса числа ггля вычисления машинного интервального индекса Т( В) числа В, молулярный код (, 7, ф 1 к.) с выхода сумматора-вычитателя 1 О подается на первый вход формирователягтег ральных характеристик модулярного кода, который начинает вычисление поправки Амербаева(С) и знака числа С. Одновременно с этим на втором такте операции модулярные...

Устройство для нормализации чисел в модулярной системе счисления

Номер патента: 1332317

Опубликовано: 23.08.1987

МПК: G06F 7/72

Метки: модулярной, нормализации, системе, счисления, чисел

...регистра 8.На (Т+4)-м такте работы устройства шифратор 10 по входному коду,Если для всех 1=1,2чвыполняется условие -р-Е+21(А(р, а при 1=ч данное условие не выполняется, то в качестве мантиссы )ц(А) и порядка ч(А) исходного числа принимаются соответственно величины А( и ч, при,этом исходное число связано с нормализованным соотношением, А=и(А) шРассмотрим как работает устройство для нормализации чисел в модулярной системе счисления.. На первом такте работы устройства модулярный код (Ц, се,., и,) числа с входа 2 устройства подается на информационные входы блоков 3.1, 3-,23 хранения констант. На выходе блока 3. хранения констант формируется набор констант) ( )р (Ч о Ь), фф эЧ, Ь (Формулы (1), (3) и фиг. 2), который передается в...

Устройство для умножения чисел в модулярной системе счисления

Номер патента: 1352483

Опубликовано: 15.11.1987

Авторы: Коляда, Ревинский, Селянинов, Чернявский

МПК: G06F 7/72

Метки: модулярной, системе, счисления, умножения, чисел

...информационный вход первого блока 14 мультиплексоров поступает в первый блок 19 вычисления интервального индекса числа Где в течение Очередных Т так О тов, считая текущий, в соответствии с формулой (3) будет вычислен машинный интервальный индекс 1(В) числа В, модулярньй код (,",л,) подается также на третий адресный вход блока 15 памяти, на второй и первый входы разрешения выдачи которого с второго и первоГО выходов 631 оеа 8 поступают11 3.М соответственно сигнаы д,= Ои = "1", В результате 1.а первом и (150 +1)-ом выходах блока 5 памяти сформируются соответственно наборы вычеК) в согокупности передаются на трет.й вход блока 3 вычисленияинтервального идакса произведения,на второй вход которого подается модулярный код числа с выхода...

Арифметическое устройство в остаточной системе счисления

Номер патента: 1354190

Опубликовано: 23.11.1987

Автор: Коляда

МПК: G06F 7/72

Метки: арифметическое, остаточной, системе, счисления

...В случае, когда на первом такте А =0 операция определения знака числа А является многотактной, на каждом такте инверсное значение 0, младшего разряда регистра 12 подается на счетный вход счетчика 16, и так как содержимые сдвиговых регистров ежетактно сдвигаются на один разряд влево, то на всех тактах операции определения знакаь 13541 числа А за исключением первого содержимого счетчика 1 б увеличивается на. единицу. Благодаря этому на (1+2)-м такте операции блок 20 масштабировал ния начинает формирование оценки А, для 0=О, 1Ь. После (Т+2)-го такте содержимое регистра 13 становится ненулевым, вследствие чегоподаваемая с выхода элемента ИЛИ-НЕ 18, на управляющий вход блока 25 мультиплексоров принимает нулевое значение, поэтому на выход...

Устройство для извлечения квадратного корня с перестраиваемым основанием системы счисления

Номер патента: 1363204

Опубликовано: 30.12.1987

Автор: Глазачев

МПК: G06F 7/552

Метки: извлечения, квадратного, корня, основанием, перестраиваемым, системы, счисления

...подаются на входы двухмладших разрядов всех блоков 7 суммирования и на коммутатор 8, На аналогичные входы остальных разрядов блоков 7 суммирования с выходов регистров 9, 10 подаются цифры Ри 0 дляполучения дополнительного кода отрицательного приращения М, После первого такта в регистре 1 записаны всенули, поэтому на выходах дешифраторов блока 3 сигналов нет, В первомтакте в блоках ,1-7.(Р) в соответствии с диаграммой извлечения происходит суммирование в используемойсистеме счисления двух старших разрядов подкоренного выражения в видедополнения с положительными значениями углов первого такта 01,04, 45( Р), ( Р), выр аб атываемых в блоке6 в виде констант, Полученные суммыв виде двух Р-ичных чисел, поразрядных суьщ и...

Устройство для сложения в избыточной системе счисления

Номер патента: 1365077

Опубликовано: 07.01.1988

Авторы: Золотовский, Коробков

МПК: G06F 7/49

Метки: избыточной, системе, сложения, счисления

...формирователя признаков, где д = 2,и, соединены с первым информационным входом (д+1)-го восьмиразрядного формирователя, выход признака суммы меньше нуля первого восьмираэрядного формирователя признаков соединен с выходом признака суммы меньше нуля устройства, первый, второй и третий выходы номера старшего разряда, отличного от нуля, первого восьмиразрядного формирователя признаков соединены соответственно с первым, вторым и третьим выходами номера старшего разряда, отличного от нуля, устройства, первый, второй и третий выходы номера разряда, отличного от нуля, -го восьмиразрядного формирователя признаков соединены соответственно с вторым, третьим и четвертым информационными входами (д+1)-го восьмиразрядного формирователя,...

Устройство для умножения чисел в модулярной системе счисления

Номер патента: 1368878

Опубликовано: 23.01.1988

Авторы: Амербаев, Коляда, Селянинов, Чернявский

МПК: G06F 7/72

Метки: модулярной, системе, счисления, умножения, чисел

...случае11 ервый элемент 15 задержки осуществляет задержку на (Т+Те +5) тактов. 8878 2вается константа У, =/Х,/ ше/тп;,Х У; 50,1 ш;-1 1=11-1,Блок 18 вычисления интервальногоиндекса числа служит для определенияпо входному модулярному коду (М,от,Е) ЧИСЛа А, ГдЕ М; =/А/а МаШИНного интервального индекса числа поформулее- /М е, от, /тп1 (А) = +,1 ) передается на вход блока19 суммирования вычетов, которые втечение очередных Т тактов, считаятекущий, вычисляют соответственновеличины 1(С) и 1 (формулы (1)и (3),На (Т+Т+5)-м такте работы величины 1(С) с выхода блока 18 вычисления интервального индекса числа ил(С) с выхода блока 17 суммирования вычетов поступают на входы схемы 21 сравнения с константой, 15На (Т+Т +6)-м такте работы величины 1(С) с...

Преобразователь кода дробного числа из одной системы счисления в другую

Номер патента: 1378064

Опубликовано: 28.02.1988

Автор: Лебедев

МПК: H03M 7/12

Метки: дробного, другую, кода, одной, системы, счисления, числа

...разрядов, представляющие циАры восьмиричной дроби и триады, т.е.исключить из тетради старший бит он всегда равен нулю), например, внешним монтажем при подключении выходов 4 масштабирующих сумматоров 1 первого столбца матрици к разрядным выходам 11 преобразователя, а затем в получившейся дроби снять разбивкудвоичных разрядов на триады, что является чисто формальной операцией. Таким образом, на выходах 4 масштабирувщих сумматоров 1 первого столбца матрицы появляются кодовые комбинации 0100, 0101, 0110, и после исключения старших разрядов тетрад на разрядных выходах 11 преобразователя получается кодовая комбинация 100101110, которая представляет девять разрядов двоичной дроби, приближающей исходнув дробь 0,59. Действительно, Ою...

Устройство для сложения в избыточной двоичной системе счисления

Номер патента: 1381487

Опубликовано: 15.03.1988

Автор: Гаврилин

МПК: G06F 7/49

Метки: двоичной, избыточной, системе, сложения, счисления

...со старших разрядов, на входы 1-4 устройства, при этом на выходах 10 и 11 в той же последовательности от старших разрядов к младшим формируются разряды результата в той же системе счисления., Возможны два варианта подключения операндов к устройству, приведенные в табл. 2, при этом работа устройства идентична для обоих случаев подключения, поэтому далее рассматривается второй вариант.где М, Мр, Ур, УР" ХР ХР двоичные цифры операндов;двоичная цифра промежуточной суммыр-го разрядацифра переноса вр-й разряд. В формулах (1) и (2) переменныеправых частей имеют одинаковый вес,они поступают на входы блоков 8 и 9.Переменные П1 в левой части (1) иМ , в левой части (2) имеют удвоенный вес, на что указывает множитель2. Для согласования веса...

Устройство для сложения и вычитания чисел в избыточной минимальной системе счисления

Номер патента: 1381489

Опубликовано: 15.03.1988

МПК: G06F 7/49

Метки: вычитания, избыточной, минимальной, системе, сложения, счисления, чисел

...выражению4)(г)-г)=фг);элемент И 33 по выражению(17(г)-47(г)=4(г);элемент И 20 по выражениюс(г)-фг) =фг)+фг)Вход 28 является входной шинойг-го разряда первого слагаемого илиуменьшаемого.Вход 30 является входной шинойуправления. При организации суммирования на нее подается логическая единица.Входы 22 - 26 являются входами 40для г-го, (г)-го, (г)-го, (г)го и (г)-го разрядов вычитаемого,Вход 22 служит также для подачи г-горазряда второго слагаемого на триггер9 в режиме суммирования45Вход 27 является сбросовой шинойи служит для обнуления триггеров 1и 9,Вход 31 является входом сигналапереноса из (г+5)-го разряда.50Выход 16 служит входом переносав (г)-й разряд при операции развертки (4) вычитаемого,Выход 29 служит входом переносав (г)-й разряд...

Сумматор в знакоразрядной позиционно-остаточной системе счисления

Номер патента: 1383349

Опубликовано: 23.03.1988

Авторы: Алексеев, Бондаренко, Евстигнеев, Куракин, Силаев

Метки: знакоразрядной, позиционно-остаточной, системе, сумматор, счисления

...180 элементы ИЛИ, седьмой элемент НЕ 181, пятый 182, шестой 183 и седьмой 184 элементы И, восьмой 185 и девятый 186 элементы НЕ,восьмой 187,девятый 188, десятый.189 и одиннадцатый 190 элементы И, пятый элемент ИЛИ 191, двенадцатый 192, тринадцатый 193, четырнадцатый 194, пятнадцатый 195 и шестнадцатый 196.элементы И, шестой элемент ИЛИ 197, семнадцатый 198, восемнадцатый 199, девятнадцатый 200,двадцатый 201, двадцать первый 202,двадцать второй 203 и двадцать третий 204. элементы И, седьмой элементИЛИ 205, двадцать четвертый 206,двадцать пятый 207 и двадцать шестой 208 элементы И, восьмой элемент ИЛИ 209, двадцать седьмой элемент И 210,девятый элемент ИЛИ 211, двадцать восьмой 212, двадцать девятый 213, тридцатый 214,тридцать первый 215,...

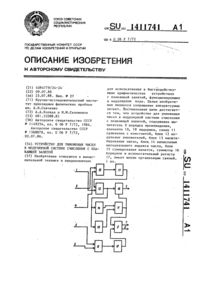

Устройство для умножения чисел в модулярной системе счисления с плавающей запятой

Номер патента: 1411741

Опубликовано: 23.07.1988

МПК: G06F 7/72

Метки: запятой, модулярной, плавающей, системе, счисления, умножения, чисел

...являющегося оценкойдроби А В Я/М, выходит за пределыинтервала-р - 1, р - 1, то число35С 1 Р, В этом случае дробь С /М, гдеС - оценка дроби А В/М, являетсянормализованной и, следовательно,представляет собой мантиссу результата, в противном случае в качествемантиссы результата принимается дробьС/М. При этом в первом случае порядок результата определяется соотношением 4(С) = 1(а) + 4(В), а во втором - соотношением (С) = 1(а) +45+ 4 (В) - 1,Устройство работает следующим образом.На первом такте работы модулярныекоды (с 1,с(,) числителя А мантиссы М(а) и (1"1,) числителя В мантиссы М(В) с входов 3 и 4 поступаютсоответственно на первый и второйвходы блока 12 модульных умножителей,который получает модулярный код(ъ ъ) произведения С = А"В,...

Устройство для сложения в избыточной системе счисления

Номер патента: 1422232

Опубликовано: 07.09.1988

Авторы: Золотовский, Коробков

МПК: G06F 7/49

Метки: избыточной, системе, сложения, счисления

...расширение функциональных возможностей за счет , возможности вычитания чисел.На чертеже представлена функциональ; ная схема одного разряда устроства.Устройство содержит входы 1 - 3 сла, гаемых, входы 4 и 5 переноса, двоичный , сумматор 6, элемент И , формирователь 8 : суммы, блок 9 формирования переноса, выходы 10 и 11 переноса в следующий разряд, регистр 12, выходы 13 - 15 суммы, вход 16 знакового разряда очередного сла; гаемого, входы 17 и 18 второго и младшего разрядов очередного слагаемого, вход 19 переноса из предыдущего разряда устройства, вход 20управления сложением, элементы НЕ 21 - 25, элементы ИЛИ 26 - 28, элементы И 29 - 37, выход 38 переноса в следующий разряд устройства (выходы 10, 11 и 38 не обозначены). Рассмотрим...

Арифметическое устройство в модулярной системе счисления

Номер патента: 1432517

Опубликовано: 23.10.1988

Авторы: Коляда, Селянинов, Чернявский

МПК: G06F 7/72

Метки: арифметическое, модулярной, системе, счисления

...синхронизации с второго По девятый соединены соответственно с управляющим входом блока вычисления интервального индекса произведения, с управляющим входом узла формирова 40 Ния результатов умножения, с выходом сигнала готовности устройства, с управляющими входами мультиплексоров первой группы, с первым и вторым вхоцами разрешения выдачи первого блока хранения констант, с управляющими входами мультиплексоров третьей группы, с управляющими входами мультиплексоров второй группы, о т л и ч аю щ е е с я тем, что, с целью расширения области применения,за счет об 50 работки операндов, представленных в форме с плавающей запятой, оно содержит узел обработки операндов, узел контроля аддитивного переполнения, Второй блок вычисления интервального...

Сумматор избыточной минимальной системы счисления

Номер патента: 1539768

Опубликовано: 30.01.1990

МПК: G06F 7/49

Метки: избыточной, минимальной, системы, сумматор, счисления

...и одного нулевогосигналов сигнал суммы равен единице,а сигнал переноса - нулю.При поступлении на вход сумматорасигналов переноса из (+2) или (1++3)-го разрядов сигнал суммы данногоразряда равен. единице, а сигнал переноса при этом равен нулю.При поступлении на вход первогоразряда сумматора двух еДиничных разрядов сигнал суммы этого разряда равен нулю, а сигнал переноса во второйразряд равен единице.При поступлении на вход первогоразряда единичного сигнала слагаемого и одного нулевого сигнал суммыданного разряда равен единице, асигнал переноса во второй разряд приэтом не возникает,При поступлении на вход первогоразряда сигнала переноса из четвертого разряда сигнал суммы данного разряда равен единице, а сигнал переноса равен нулю.При...

Преобразователь чисел из кода системы счисления в остаточных классах в двоичный код

Номер патента: 1541783

Опубликовано: 07.02.1990

Авторы: Исмаилов, Хаспулатов

МПК: H03M 7/18

Метки: двоичный, классах, код, кода, остаточных, системы, счисления, чисел

...счетчика 6 увеличивается на "1" причем оно Равно 1.1 р-где 1 номеРциклав Ча а вход ЭА блока 7 подается число с выхода счетчика 6, на вход ЭВ - остаток модуля Рв. После Фронта С 2 через время достаточное55 для последовательной записи в регистр 2, передачи информации через мультиплексоры 3 и 5, выборки из блока 7,. следует Фронт СЗ, по которому вычитатель 4 выполняет действиеНакапливающий сумматор8 прибавляет к числу, которое содержит число с выхода Я блока 7,Через время работы накапливающегосумматора 8 (значительно большее,чем время срабатывания вычитателя 4);цикл заканчивается,Формула. изобретения Преобразователь чисел из кода системы счисления в остаточных классахв двоичный код, содержащий регистр,вычитатель по совокупности...

Генератор последовательности избыточной системы счисления

Номер патента: 1543397

Опубликовано: 15.02.1990

Авторы: Гриб, Дудкин, Яковенко

МПК: G06F 1/02

Метки: генератор, избыточной, последовательности, системы, счисления

...соединен с информационным вхо" дом (р+1)-.го регистра первой группы, выходы регистров с (1 с+) -го по (21 с+ +1)-й первой группы соединены соответственно с входами слагаемых первого сумматора, выход второго сумматора 5 15 20 25 30 35 40 45 50 соединен с вторым входом первого блока элементов ИЛИ, выход 11-го регистра второй группы (М . 1 с+П, П= 4, при 1 с = 1, Пс+ при 1 с 2) соединен с информационным входом 04+)го регистра второй группы, выход перзого регистра второй группы соединенс входом первого слагаемого второгосумматора и является выходом значениямассы генератора, первый тактовыйвход которого соединен с входами разрешения записи регистров перной группы, второй и третий тактовые входыгенератора соединены соответственнос...

Устройство для сложения в избыточной двоичной системе счисления

Номер патента: 1587494

Опубликовано: 23.08.1990

Авторы: Арцатбанов, Гречишников, Телековец

МПК: G06F 7/49

Метки: двоичной, избыточной, системе, сложения, счисления

...первые П-входы первого и второго П-триггеровблока формирования результата являются соответственно первым и вторымвходами признака блока формирования результата, С-входы первого ивторого П-триггеров подключены квходу синхронизации блока формирования результата, и; инверсные выходыявляются соответственно первым ивторым выходами блока формированиярезультата, а вторые П-входы первого и второго П-триггеров блока формирования результата подключены квторому входу признака "1" блока формирования результата. Последний содержит две группы по три элементаИ-НЕ, причем первые входы элементовИ-НЕ первой и второй групп подключены к первым входам первых элементовИ-НЕ соответственно первого и второго П-триггеров, второй вход первогоэлемента И-НЕ первой...

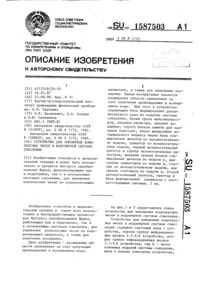

Устройство для умножения комплексных чисел в модулярной системе счисления

Номер патента: 1587503

Опубликовано: 23.08.1990

Авторы: Василевич, Коляда, Селянинов

МПК: G06F 7/72

Метки: комплексных, модулярной, системе, счисления, умножения, чисел

...номер1 константы И с первого выхода элемента 10 задержки поступает на третьиадресные входы блоков 11.1-11,1 с-,1памяти. В блоке 5 осуществляется формирование дополнительного кода15 ( / - М,/ /- Ы,",/ ) числа (-Аф),который с выхода блока 5 через первую группу информационных входовблока б поступает на входной регистр7, В регистре 8 посредством блока 920формируется модулярный код (ос(,ффЫ) числа А ; из блока памяти 11,считывается набор константЧ; ( о(;, ос" 1) = ( К, (о, Ы 1)1"1 о о/ 1)(формулы 1 и 2), При этом первая компонента данного набора К (осо 1)с первого выхода блока 11. памятипередается на -й вход блока 14 суммирования вычетов по вспомогательному модулю, а 3-я компонента набора-В ( Ы. , о 1 ) Ц = 2 3 . . ., ц + 1 )поступает на х...

Десятичный сумматор в избыточной системе счисления

Номер патента: 1594524

Опубликовано: 23.09.1990

МПК: G06F 7/49

Метки: десятичный, избыточной, системе, сумматор, счисления

...величина Р. Еечетырехразрядный код образуется навыходах элементов ИЛИ 21, 23-25,Сложение этой величины с промежуточным результатом осуществляется в блоке 4 Аормироваиия конечного результата, состоящем из одноразрядныхсумматоров 1-20, Тем самым в блоках 3 и 4 (коррекции и Аормирования .конечного результата) реализуетсятретий шаг алгоритма.Входы и выходы положительного иотрицательного переносов используются для связи между разрядами в параллельном многоразрядном десятичномсумматоре в избыточной зцакоразрядной системе счисления,Рассмотрим пример сложений десятичных знакоразрядных чисел по выше приведенному алгоритму. Значенияоперандов в обычном десятичном представлении равны Х = 26345, а У =- 18094,В знакоразрядном представлении их...

Последовательный сумматор в избыточной двоичной системе счисления

Номер патента: 1619251

Опубликовано: 07.01.1991

Автор: Телековец

МПК: G06F 7/49

Метки: двоичной, избыточной, последовательный, системе, сумматор, счисления

...имеет вид1 (.( 1+г (г (г 1 (.гили,Элемент ИСКЛИЧАИЦЕЕ ИЛИ 24 Аармирует значение положительной суммыЛогические выражения для результата имеют видЕ =ЯЧЯР+г (+(В табл. 2 приведен пример сложения чисел А О, 1110 и В=О, 1010 в устройстве (2=1,10=0,10).Формула и з о б р е т енияПоследовательный сумматор в избыточной двоичной системе счисления, содержащий блоки Аормирования положительной и отрицательной сумм, блок формирования результата и два элемента задержки, причем входы блока Аормирования отрицательной суммы соединены с первым и вторым входами сумматора, а выход подключен к входу первого элемента задержки, выход которого соединен с первым входом блока Аормирования положительной суммь(, выход кото- рога подключен к входу второго элемента...

Устройство для перевода числа, представленного в системе остаточных классов, в полиадическую систему счисления

Номер патента: 1619403

Опубликовано: 07.01.1991

Авторы: Гладченко, Журавлев, Ирхин, Краснобаев, Куцый, Панков, Фоменко

МПК: H03M 7/18

Метки: классов, остаточных, перевода, полиадическую, представленного, системе, систему, счисления, числа

...будут в том случае, когда остатки в соответствующих регистрах 1-1 и 1-(и+2) будут равны нулю. Каждой матрицей элементов И 23 выполняется действие (,-,)шос 1 р, причем К=0 , =О. Каждый элемент ИЛИ 3 групп и блок 22 элементов ИЛИ выполняет действие: (О(,-0 шос 1 р х( в -) аи т,д, Эле 1 (1)мент И 1 О определяет результат (а, -Я)шос 1 р , а матрица элементовьфИ 20 определяет результат (а . -Я) шос 1 Р . Блок 21 элементов ИЛИ определяет РХРРх(а, ,-Я)Рф фРассмотрим работу устройства (Ьиг.1) для двух случаев. Первый случай - при А= 1,Р, а второй при А=О и А=Р, В .первом случае устройство работает следующим образом. Код числа А, для которого нужно получить двоичный позиционный код (расширение по модулю р + =Р) поступает на регистры 1-. (1=1...