Устройство для вычисления экспоненциальной функции в модулярной системе счисления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1317433

Авторы: Коляда, Кравцов, Селянинов, Чернявский

Текст

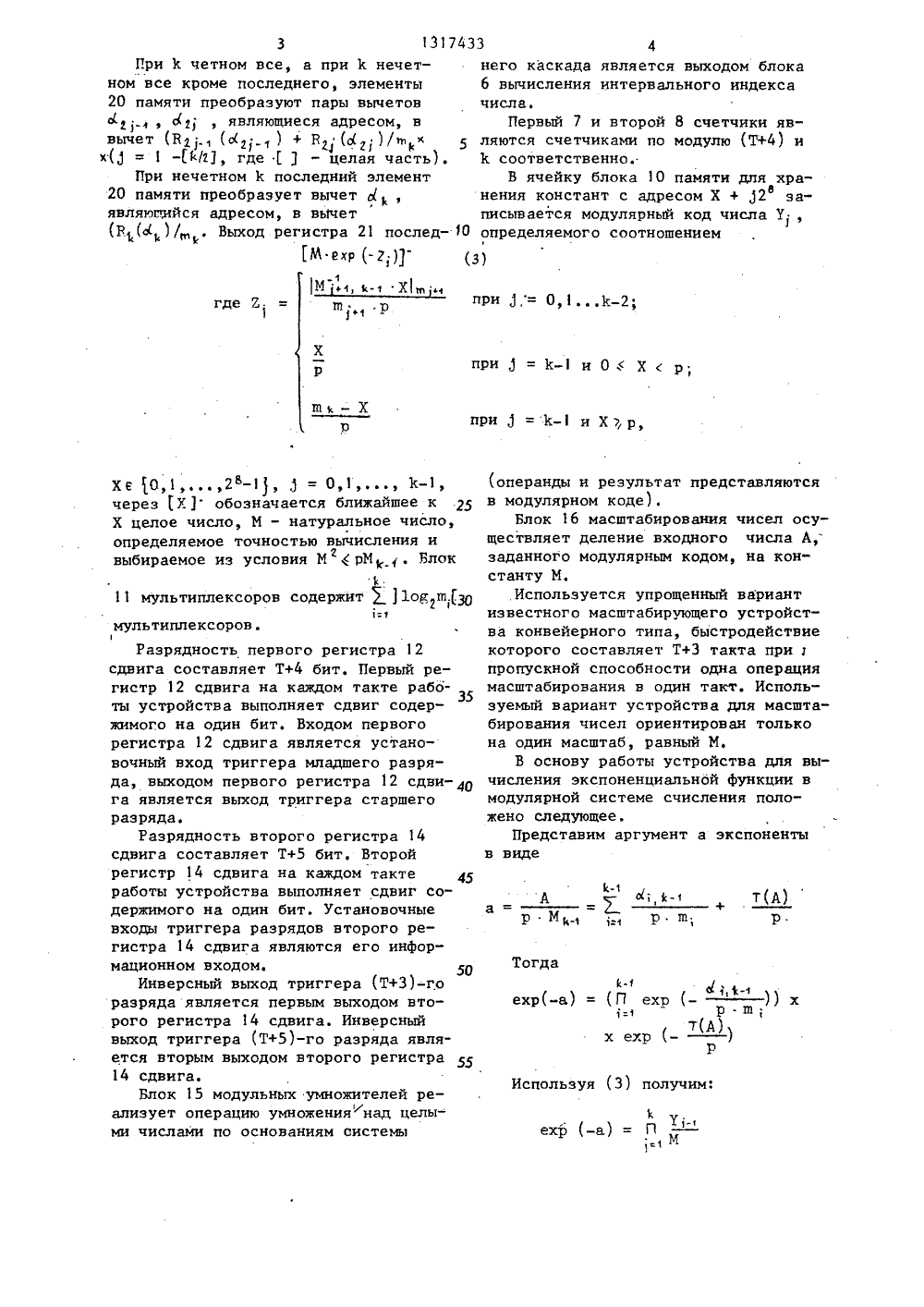

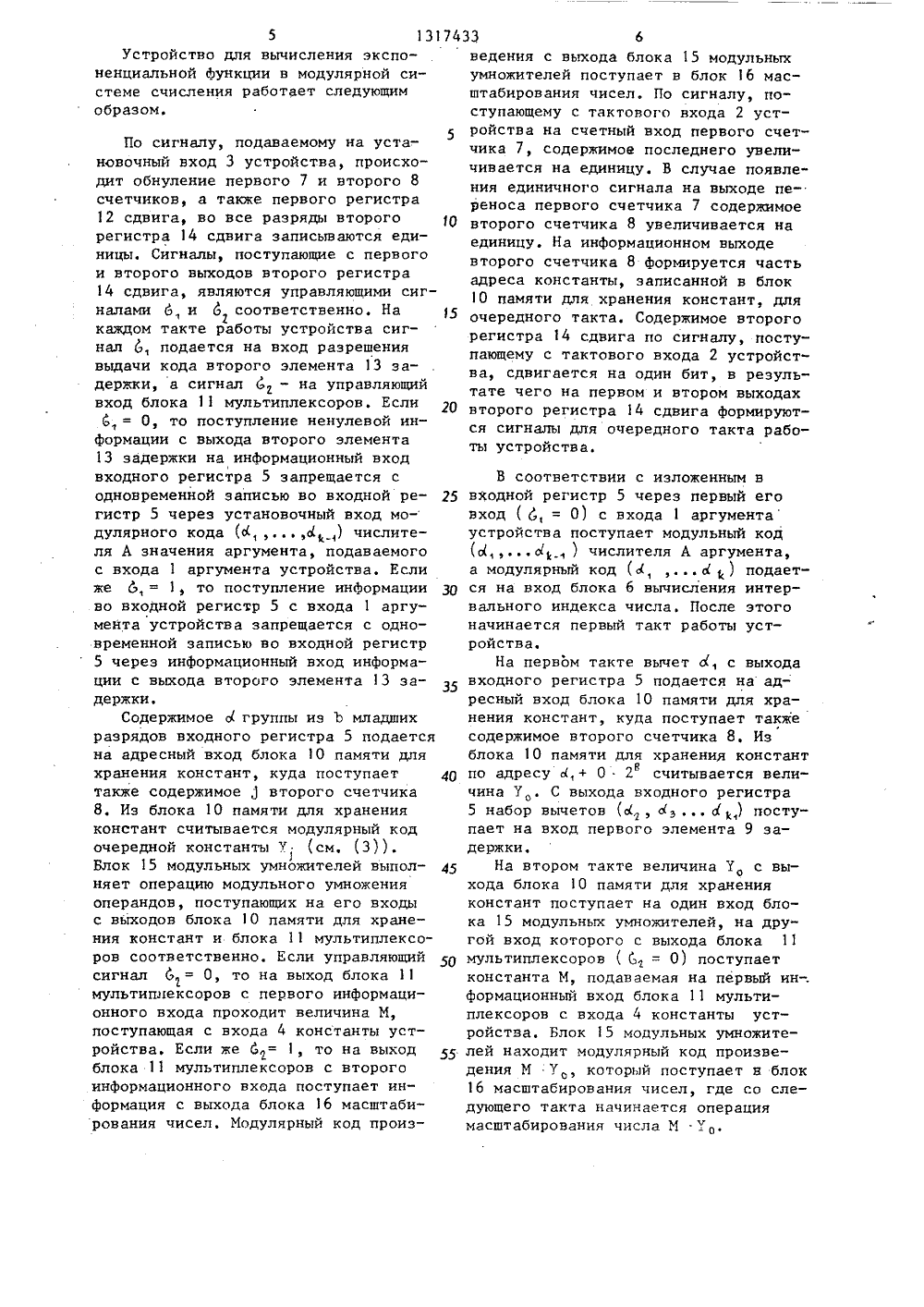

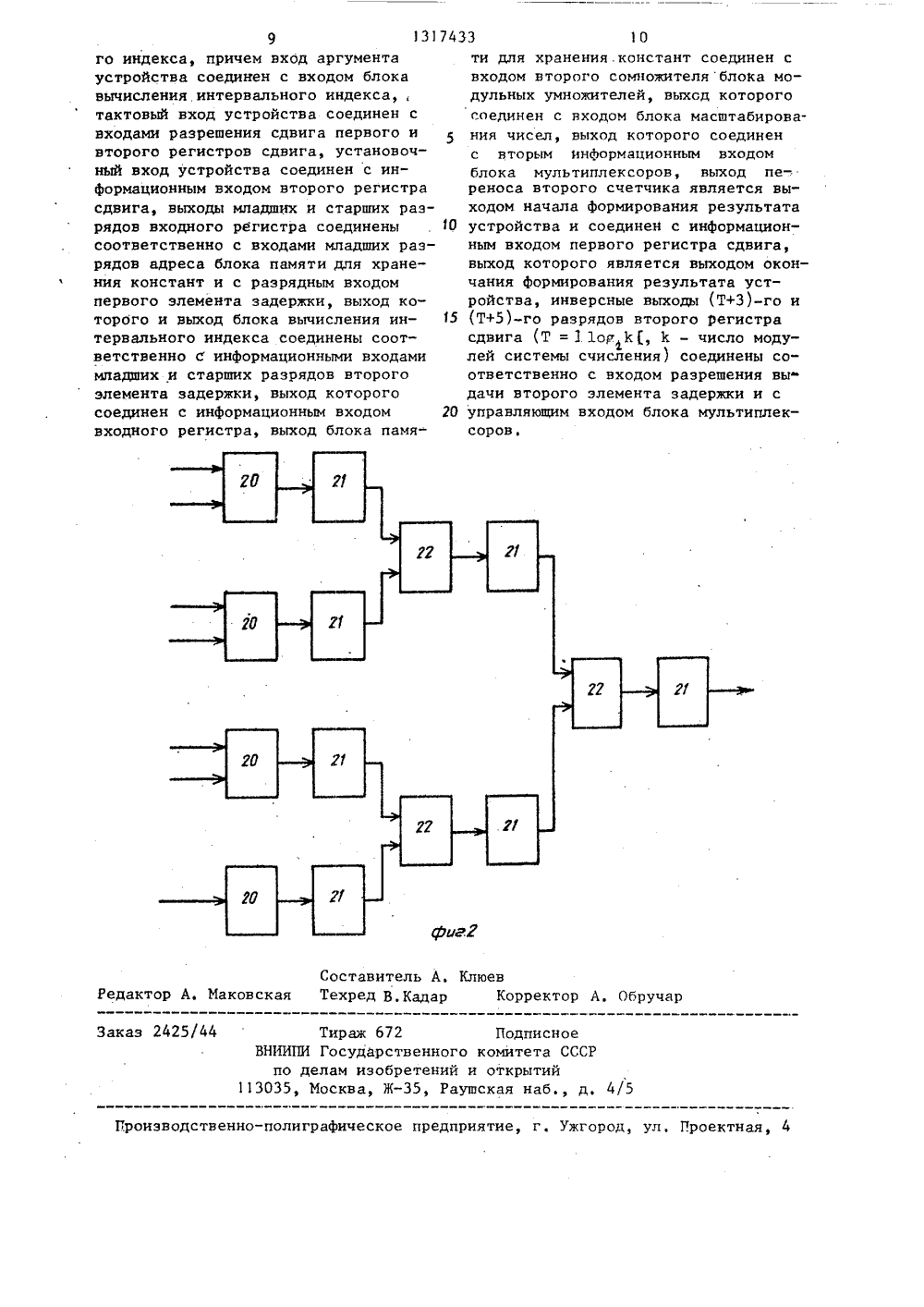

(511 4 О 06 У 7/5 ПИСАНИЕ ИЗОБРЕТ г1,ЕТЕЛЬСТВУ К АВТОРСКОМ 2 ский инс проблем вател чески оматикиалькой фунсчисленияповьппенииая цельройство,5, счетКравцов,ернявский В. К Ф, етельство СССР Р 7/544, 1977. ельство СССР Р 7/544, 7/72,ВЫЧИСЛЕНИЯ ЗКСКЦИИ В МОДУЛЯРНОЙ тся к вычисентировано н ОСУДАРСТВЕННЫЙ КОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТ(54) УСТРОЙСТВО ДЛЯПОНЕНЦИАЛЬНОЙ ФУНСИСТЕМЕ СЧИСЛЕНИЯ(57) Изобретение олительной технике и использование в быстродействующихспециализированных вычислителях, системах цифровой обработки сигналови в различных системах автдля вычисления зкспоненцикции в модулярной системеЦель изобретения состоит вбыстродействия. Поставленндостигается тем, что в устсодержащее входной регистрчики 7, 8, блок 10 памяти для хранения констант, блок 11 мультиплексоров, регистр 12 сдвига, блок 15 модульных умножителей и блок 16 масштбирования, введены элементы эадержк9. 13. регистр 14 сдвига и блок 6вычисления интервального индекса с соответствующтми связями.2 ил.Блок вычисления интервального ин декса числа 6 по входному модулярному коду ( Ы с) некоторогочисла А осуществляет Формированиевычета за Т тактов Т(А) д Е;(;1 В; (с(.; ) при 1=1,2 Кгп; при 1 = К 1 13174Изобретение относится к вычислительной технике и ориентировано наиспользование в быстродействующихспециализированных вычислителях, системах цифровой обработки сигналов иразличных системах автоматики для вычисления экспоненциальной функции отаргументов, представленных в модулярной системе счисления.Целью изобретения является ловы- Юшение быстродействия.На фиг. 1 приведена структурнаясхема предлагаемого устройства длявычисления экспоненциальной функциив модулярной системе счисления; на 15фиг. 2 - схема блока вычисления интервального индекса (для К = 7, К -число модулей системы счисления).Устройство для вычисления экспоненциальной функции в модулярной системе счисления (фиг. 1) содержитвход 1 аргумента, тактовый вход 2,установочный вход 3, вход 4 константы устройства, входной регистр 5,блок 6 вычисления интервального индекса числа, первый счетчик 7, второй счетчик 8, первый элемент 9 задержки, блок 10 памяти для храненияконстант, блок 11 мультиплексоров,первый регистр 12 сдвига, второй элемент 1,3 задержки; второй регистр 14сдвига, блок 15 модульных умножителей, блок 16 масштабирования чисел,выход 17 окончания формирования результата устройства, выход 18 результата устройства и выход 19 началаформирования результата устройства.. Блок 6 вычисления интервальногоиндекса числа (фиг, 2) содержит элементы 20 памяти, регистры 21 и сумматоры 22 по модулю,Вход 1 аргумента устройства подключен к входу входного регистра 5,предназначенного для приема модулярного кода по попарно взаимно простымоснованиям шш),(с( о) исходного числа А из множества Р =0,1,р М - 1.с(; = 1 А ),; (1. = 1,2 К),причем ш 7, 2 р + К, р - фиксирован 50ное натуральное число; М 1 = П ш,;через 1 Х 1 обозначен наименьший неотФрицательный вычет,Разрядность входного регистра 5составляет (К - 1)Ь бит, где Ь - раз рядность вычетов по наибольшему измодулей выбранной модулярной системысчисления. Информационный вход входного регистра 5 соединен с выходом 33 2второго элемента 13 задержки. Выход группы из Ъ младших разрядов входного регистра 5 подключен к адресному входу блока 10 памяти для хранения констант. Выходы остальных (К) групп из д разрядов подключены к входу первого элемента 9 задержки.Первый элемент 9 задержки представляет собой цепочку из Тпоследовательно соединенных регистров, где Т1 оя К , через 1 Х ( обозначается наименьшее целое число не меньшее Х. Вход первого из регистров является входом первого элемента 9 задержки, Разрядность регистров, входящих в состав первого элемента 9 задержки, составляет (К)Ъ бит. Выход последнего регистра первого элемента 9 задержки является его выходом.Второй элемент 13 задержки представляет собой цепочку из четырех последовательно соединенных регистров, вход первого из которых является входом второго элемента 13 задержки. Разрядность регистров, входящих в состав второго элемента 13 задержки, составляет (К)Ъ бит. Входы первых (К),групп и вход старшей (К)-й группы из Ъ разрядов первого регистра являются входом элемента 13 задержки.Выход последнего регистра второго элемента 13 задержки является его, выходом. Вход разрешения выдачи кода последнего регистра второго элемента 13 задержки является его входом разрешения выдачи кода. Блок 6. вычисления интервального индекса числа имеет Т-каскадную конвейерную структуру.3 1317433 4При Е четном все, а при 1 нечет- него каскада является выходом блока ном все кроме последнего, элементы 6 вычисления интервального индекса 20 памяти преобразуют пары вычетов числа.являющиеся адресом, в Первый 7 и второй 8 счетчики яввычет (Н ., (с ) + В(с )/х 5 ляются счетчиками по модулю (Т+4) и(х =-11 сй 3, где1 - целая часть). Е соответственно.При нечетном Е последний элемент В ячейку блока 10 памяти для хра памяти преобразует вычет Ы 1 кения констант с адресом Х + 12 зав являюсщйся адресом, в вычет писывается модулярный код числа УЭ (Р 1,(Ыь)/), . Выход регистра 21 послед определяемого соотношениемГм ехр (-г,) М ) 1) 3 с Хп И при ,= 0,1 К; где Е 1;., М Хе 0,12-1) = 0,1 Х,через 1,Хобозначается ближайшее к .25Х целое число, М - натуральное число,определяемое точностью вычисления ивыбираемое из условия М 4 рМ. Блок211 мультиплексоров содержит,) 11 оКш.30 мультиплексоров1Разрядность первого регистра 12 сдвига составляет Т+4 бит. Первый регистр 12 сдвига на каждом такте работы устройства выполняет сдвиг содержимого на один бит. Входом первого регистра 12 сдвига является установочный вход триггера младшего разряда, выходом первого регистра 12 сдви га является выход триггера старшего разряда.Разрядность второго регистра 14 сдвига составляет Т+5 бит. Второй регистр 14 сдвига на каждом такте 45 работы устройства выполняет сдвиг содержимого на один бит. Установочные входы триггера разрядов второго регистра 14 сдвига являются его информационном входом. 50Инверсный выход триггера (Т+3)-го разряда является первым выходом второго регистра 14 сдвига. Инверсный выход триггера (Т+5)-го разряда является вторым выходом второго регистра 14 сдвига.Блок 15 модульных умножителей реализует операцию умножениянад целыми числами по основаниям аистемы(операнды и результат представляются в модулярном коде).Блок 16 масштабирования чисел осуществляет деление входного числа А,- заданного модулярным кодом, на кон" станту М.Используется упрощенный вариант известного масштабирующего устройства конвейерного типа, быстродействие которого составляет Т+3 такта при 1 пропускной способности одна операция масштабирования в один такт. Используемый вариант устройства для масштабирования чисел ориентирован только на один масштаб, равный М.В основу работы устройства для вычисления экспоненциальнбй функции в модулярной системе счисления положено следующее.Представим аргумент а экспоненты в видеПо сигналу, подаваемому на установочный вход 3 устройства, происходит обнуление первого 7 и второго 8 счетчиков, а также первого регистра 12 сдвига, во все разряды второго регистра 14 сдвига записываются единицы, Сигналы, поступающие с первого и второго выходов второго регистра14 сдвига, являются управляющими сигналами 6 и д соответственно. Накаждом такте работы устройства сигнал Ь, подается на вход разрешениявыдачи кода второго элемента 13 за 5 держки, а сигнал 4 - на управляющий вход блока 11 мультиплексоров. Если- О, то поступление ненулевой информации с выхода второго элемента 13 задержки на информационный вход входного регистра 5 запрещается с одновременной записью во входной регистр 5 через установочный вход модулярного кода (М,Ы ,) числителя А значения аргумента, подаваемого 20 25 с входа 1 аргумента устройства. Если же Ь, = 1, то поступление информации во входной регистр 5 с входа 1 аргумента устройства запрещается с одновременной записью во входной регистр 5 через информационный вход информации с выхода второго элемента 13 задержки.Содержимое Ы группы из Ь младших 35 разрядов входного регистра 5 подаетсяна адресный вход блока 10 памяти для хранения констант, куда поступает 40также содержимое ) второго счетчика8, Из блока 10 памяти для храненияконстант считывается модулярный кодочередной константы У (см. (3.Блок 15 модульных умножителей выполняет операцию модульного умноженияоперандов, поступающих на его входыс вйходов блока 10 памяти для хранения констант и блока 11 мультиплексоров соответственно. Если управляющийсигнал 6 = О, то на выход блока 11мультиплексоров с первого информационного входа проходит величина М,поступающая с входа 4 константы устройства. Если же б= 1, то на выходблока 11 мультиплексоров с второгоинформационного входа поступает информация с выхода блока 16 масштабирования чисел, Модулярный код произ 5 13174Устройство для вычисления экспоненциальной функции в модулярной системе счисления работает следующим образом,33 6ведения с выхода блока 15 модульных умножителей поступает в блок 16 масштабирования чисел. По сигналу, поступающему с тактового входа 2 устройства на счетный вход первого счетчика 7, содержимое последнего увеличивается на единицу. В случае появления единичного сигнала на выходе переноса первого счетчика 7 содержимое второго счетчика 8 увеличивается на единицу, На информационном выходе второго счетчика 8 формируется часть адреса константы, записанной в блок 10 памяти для хранения констант, для очередного такта. Содержимое второго регистра 14 сдвига по сигналу, поступающему с тактового входа 2 устройства, сдвигается на один бит, в результате чего на первом и втором выходах второго регистра 14 сдвига формируются сигналы для очередного такта работы устройства. В соответствии с изложенным ввходной регистр 5 через первый еговход ( , = 0) с входа 1 аргументаустройства поступает модульный код(Ыс, ) числителя А аргумента,а модулярный код (А, ,с ) подается на вход блока 6 вычисления интервального индекса числа. После этогоначинается первый такт работы устройства.На первом такте вычет о(, с выходавходного регистра 5 подается на адресный вход блока 10 памяти для хранения констант, куда поступает такжесодержимое второго счетчика 8. Изблока 10 памяти для хранения константпо адресу Ы+ 0 2 считывается веливчина У,. С выхода входного регистра5 набор вычетов (Ы, сэс(,) поступает на вход первого элемента 9 задержки,На втором такте величина У с выхода блока 1 О памяти для храненияконстант поступает на один вход блока 15 модульных умножителей, на другой вход которого с выхода блока 11мультиплексоров ( 6 = 0) поступаетконстанта М, подаваемая на первый ин-.формационный вход блока 11 мультиплексоров с входа 4 константы устройства. Блок 15 модульных умножителей находит модулярный код произведения М У, который поступает н блок16 масштабирования чисел, где со следующего такта начинается операциямасштабирования числа М .Уо.1317437По истечении Т-го такта работы устройства на выходе блока 6 вычисления интервального индекса числа форлмируется вычет Г(А), который на следу. ющем такте записывается в старшую группу из Ь разрядов первого регистра второго элемента 13 задержки, в остальные 1-2 группы из Ь разрядов которого с выхода первого элемента 9 задержки поступает выбор вычетов ( Ы , 1 О Ыз, с -1) .На (Т+4)-м такте управляющий сигнал ,= 1, вследствие чего с выхода второго элемента 13 задержки в входной регистр 5 поступает набор выче тов (с, Ыс 1 Т(А. На выходе переноса первого счетчика 7 появляется единичный сигнал, вследствие чего содержимое второго счетчика 8 становится равным единице. 20 На (Т+5)-м такте блок 16 масштабирования чисел на своем выходе формирует модулярный код величины УВычет Ы с выхода входного регистра5 подается на адресный вход блока 1 Оаамяти для хранения констант, навход которого поступает также содержимое второго счетчика 8. Из блока10 памяти для хранения констант поадресу Ы+ 1"2 ф считывается величинаУ . С второго выхода входного регистлра 5 набор вычетов (с(з, а., Т(Апоступает на вход первого элемента 9задержки,35На (Т+6)-м такте работы устройства величина У с выхода блока 10памяти для хранения констант поступает на один вход блока 15 модульныхумножителей, на другой вход которого 40с выхода блока 11 мультиплексоров( М = 1) подается величина У , по.ступающая на второй информационныйвход блока 11 мультиплексоров с выхода блока 16 масштабирования чисел.Блок 15 модульных умножителей находит модулярный код произведения У хх У, который поступает в блок 16масштабирования чисел, где со следующего такта начинается операция масштабирования указанных чисел,На следующих тактах работы устройства выполняются действия, аналогичные описанным вьппе. По окончанииК (Т+4) тактов на выходе переносавторого счетчика 8 появляется единичный сигнал, поступающий на третийвыход 19 устройства, что означаетокончание вычисления значения экспо 3 8ненциальной функции от аргумента, которое снимается с выхода блока 16 масштабирования чисел на следующем такте.Элагодаря конвейерной структуре в предлагаемом устройстве одновременно может происходить вычисление экспоненциальной функции от Т+4 аргументов. При этом появление единичного сигнала .на выходе 19 устройства означает начало появления на выходе 18 устройства вычисленныхзначений экспоненциальной функции и возможность начала вычислений для новых Т+4 аргументов.Появление единичного сигнала на выходе 17 устройства означает завершение вычисления значений экспоненциальной функции от Т+4 аргументов.При работе устройства в конвейер- ном режиме из расчета на одно функциональное значение быстродействие устройства составляет Е тактов,Формула изобретенияУстройство для вычисления экспоненциальной функции в модулярной системе счисления, содержащее входной регистр, блок памяти для хранения констант, первый регистр сдвига, первый и второй счетчики, блок мультиплексоров, блок модульных умножите-:. лей и блок масштабирования чисел, причем вход аргумента устройства соединен с установочным входом входного регистра, тактовый вход устройства соединен со счетным входом первого счетчика, вход обнуления которого соединен с входом обнуления второго счетчика, с входом обнуления первого регистра сдвига и с установочнЫм входом устройства, вход константы которого соединен с первым информационным входом блока мультиплексоров, выход которого соединен с входом первого сомножителя блока модульных умножителей, выход блока масштабирования является выходом результата устройства, информационный выход второго счетчика соединен с входами старших разрядов адреса блока памяти для хранения констант, выход первого счетчика соединен со счетным входом второго счетчика, о т л и ч а ю - щ е е с я тем, что, с целью повышения быстродействия, в него введены два элемента задержки, второй регистр сдвига и блок вычисления интервально1317433 го индекса, причем вход аргументаустройства соединен с входом блокавычисления интервального индексатактовый вход устройства соединен свходами разрешения сдвига первого ивторого регистров сдвига, установочный вход устройства соединен с информационным входом второго регистрасдвига, выходы младших и старших разрядов входного регистра соединенысоответственно с входами младших разрядов адреса блока памяти для хранения констант и с разрядным входомпервого элемента задержки, выход которого и выход блока вычисления интервального индекса соединены соответственно с информационными входамимладших и старших разрядов второгоэлемента задержки, выход которогосоединен с информационным входомвходного регистра, выход блока памяСоставитель А. Клювская Техред В.Кадар А. Ма орректор А. Обруч еда Тираж 672 ПодписноеГосударственного комитета СССРлам изобретений и открытийосква, Ж, Раушская наб д. 113035 олиграфическое предприятие, г, Уж Гроиэводственн Проектная,аказ 2425/44ВНИИПИ ти для хранения. констант соединен свходом второго сомножителя блока модульных умножителей, выход которогосоединен с входом блока масштабирования чисел, выход которого соединенс вторым информационным входомблока мультиплексоров, выход пе-.реноса второго счетчика является выходом начала формирования результата 10 устройства и соединен с информационным входом первого регистра сдвига,выход которого является выходом окончания формирования результата устройства, инверсные выходы (Т+3)-го и 15 (Т+5)-го разрядов второго регистрасдвига (Т =,1 1 ор Е , Е - число модулей системы счисления) соединены соответственно с входом разрешения выдачи второго элемента задержки и с 20 управляющим входом блока мультиплексоров.

СмотретьЗаявка

3995603, 22.11.1985

НАУЧНО-ИССЛЕДОВАТЕЛЬСКИЙ ИНСТИТУТ ПРИКЛАДНЫХ ФИЗИЧЕСКИХ ПРОБЛЕМ ИМ. А. Н. СЕВЧЕНКО

КОЛЯДА АНДРЕЙ АЛЕКСЕЕВИЧ, КРАВЦОВ ВИКТОР КОНСТАНТИНОВИЧ, СЕЛЯНИНОВ МИХАИЛ ЮРЬЕВИЧ, ЧЕРНЯВСКИЙ АЛЕКСАНДР ФЕДОРОВИЧ

МПК / Метки

МПК: G06F 7/544, G06F 7/72

Метки: вычисления, модулярной, системе, счисления, функции, экспоненциальной

Опубликовано: 15.06.1987

Код ссылки

<a href="https://patents.su/6-1317433-ustrojjstvo-dlya-vychisleniya-ehksponencialnojj-funkcii-v-modulyarnojj-sisteme-schisleniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления экспоненциальной функции в модулярной системе счисления</a>

Предыдущий патент: Устройство для деления

Следующий патент: Устройство для вычисления квадратного корня числа в модулярной системе счисления

Случайный патент: Термос