Устройство для вычисления элементарных функций в модулярной системе счисления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

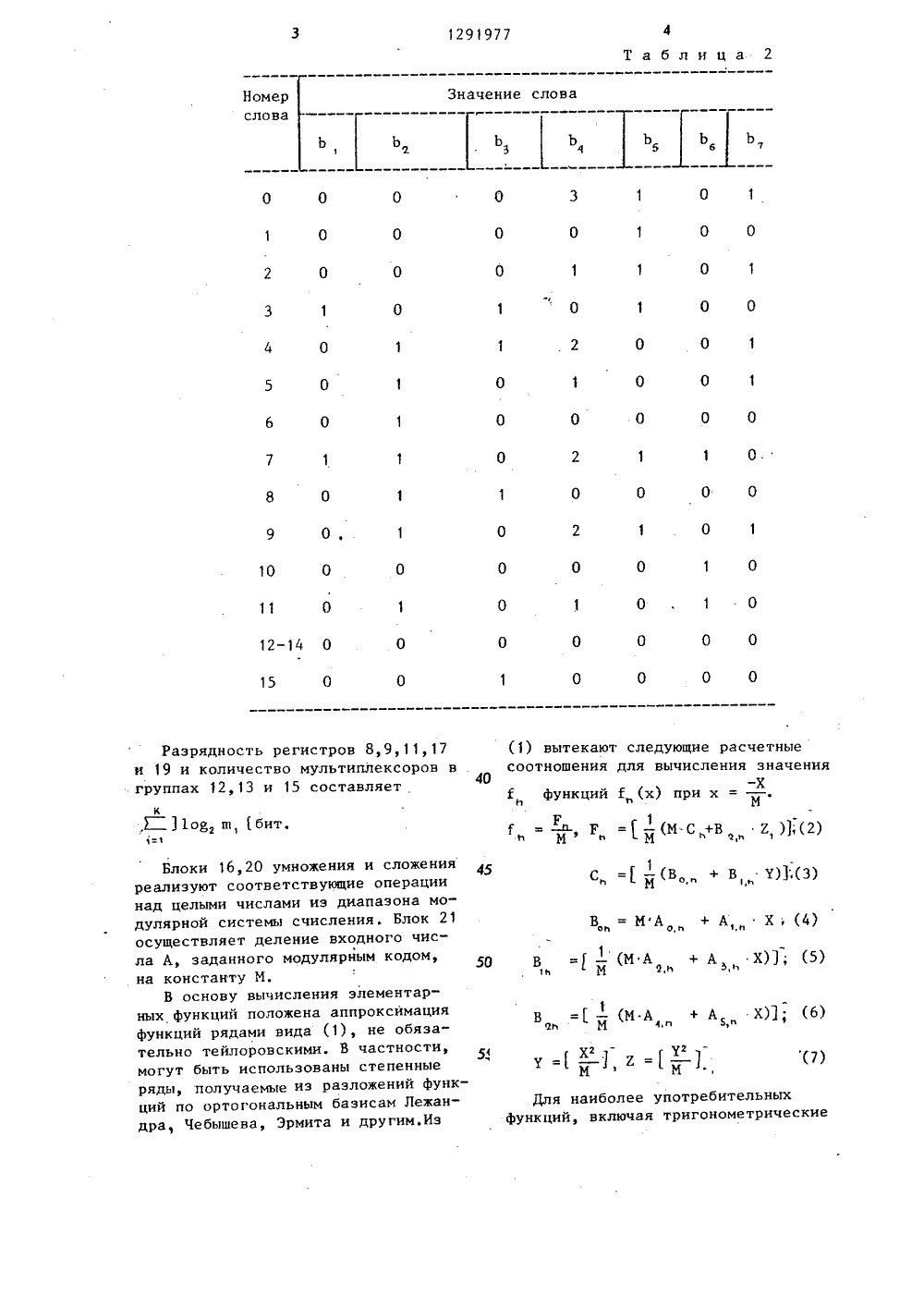

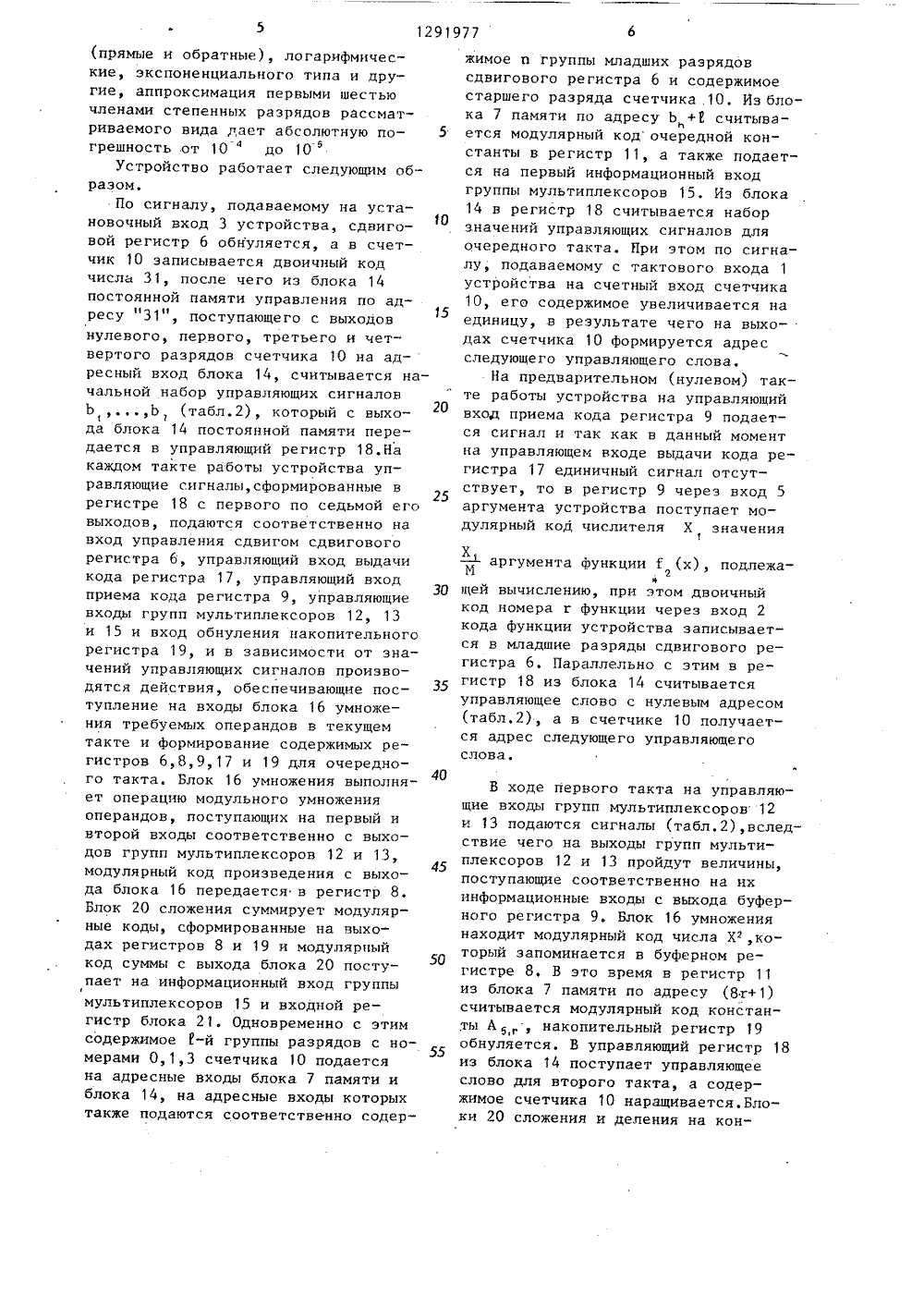

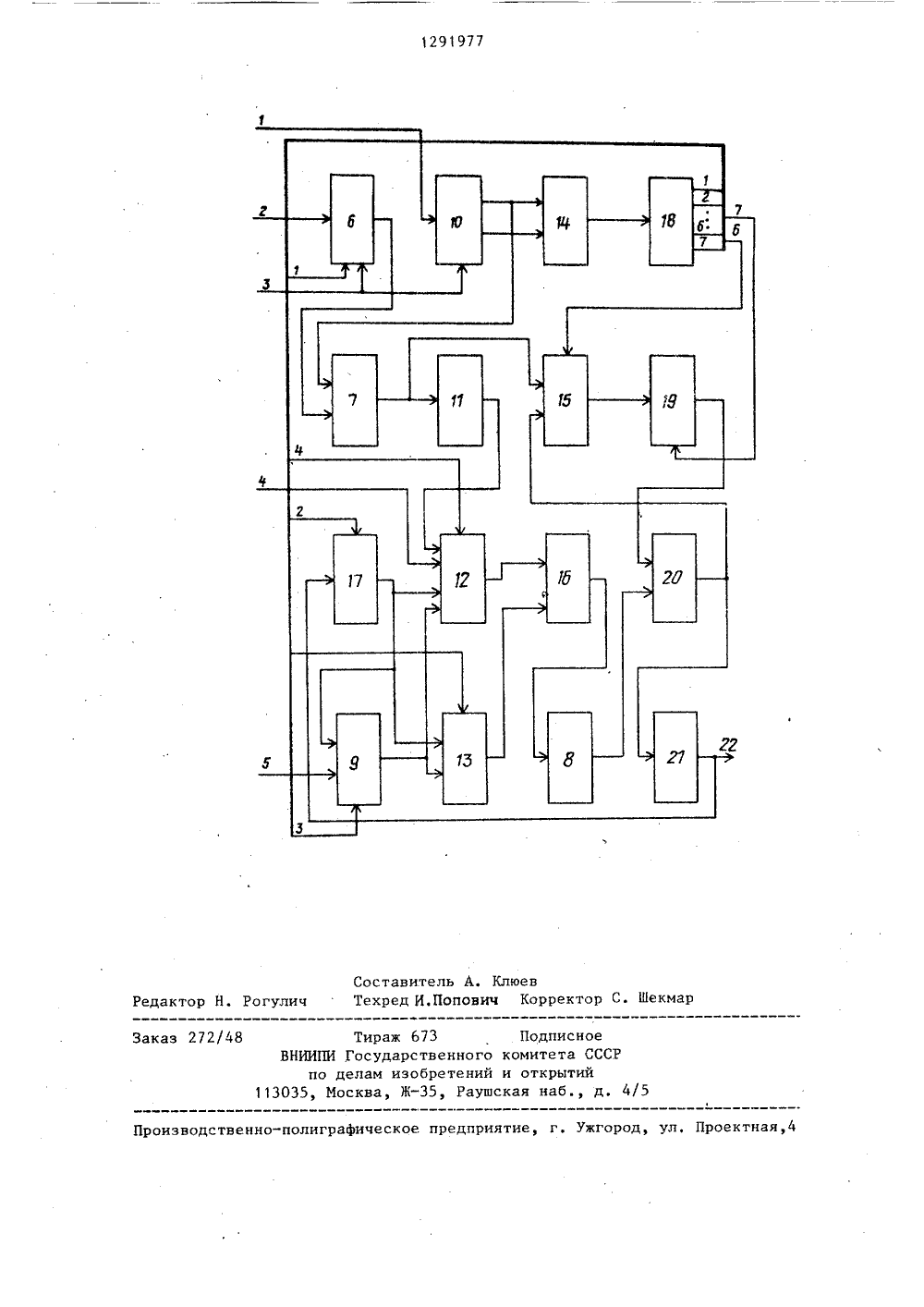

(50 4 ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ О ТЕЛЬСТВУ(71) Научно-исследовательский институт прикладных физических проблем им. А.Н. Севченко(56) Авторское свидетельство СССР У 1103225, кл. С 06 Р 7/544, 1980.Авторское свидетельство СССР Ф 983707, кл. С 06 Р 7/544, 1981, (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЭЛЕМЕНТАРНЫХ ФУНКЦИЙ В МОДУЛЯРНОЙ СИСТЕМЕ СЧИСЛЕНИЯ(57) Изобретение относится к вычислительной технике и ориентировано на использование в быстродействующих специализированных системах цифроботки ния различных (тригонометри экспоненциаль аргументов, п лярной систем ретения состо действия. Пос тся тем, чтоее сдвиговыйля хранения жения, наколожения,остоянт блок гистр кон нительный такт, бло регистр,1 ых регист управлен м а и блок ия, содержи три буфер ной памят деления н регистр иров с соо2 табл. управляющии мультиплексо ми связями.1 констан р ппь ветств Н АВТОРСКОМУ ИЗОБРЕТЕН И сигналов для вычислеэлементарных функций еских, логарифмических ого типа и других) от едставленных в моду- счисления. Цель изобт в повышении быстроавленная цель достигаустройство, содержа- регистр, блок памяти онстант, счетчик, ре1 129Изобретение относится к вычислительной технике и ориентировано наиспользование в быстродействующихспециализированных системах цифровой обработки сигналов для вычисления различных элементарных функций(тригонометрических, логарифмических,экспоненциального типа и других) отаргументов, изменяющихся в интервале- 1, 1( и представленных в модулярной системе счисления.Цель изобретения - повышение быстродействия.На чертеже представлена схемаустройства для вычисления элементарных функций в модулярной системесчисления,Устройство для вычисления элементарных функций в модулярной системе счисления содержит тактовыйвход 1 устройства, вход 2 кода задания функции устройства, установочный вход 3 устройства, вход 4 константы устройства, вход 5 аргумента1устройства, сдвиговый регистр 6,блок 7 памяти для хранения констант,первый и второй буферные регистры8 и 9, счетчик 10, регистр 11 констант, первую и вторую группы мультиплексоров 12 и 13, блок 14 постоянной памяти, третью группу мультиплексоров 15, блок 16 умножения,третий буферный регистр 17, управляющий регистр 18, накопительный регис; р 19, блок 20 сложения, блок 21деления на константу и выход 22 устройства,Разрядность сдвигового регистра6 составляет 2 31 од, Я бит,где И -число функций, вычисляемых устройством, через 3 хобозначается наименьшее целое число, не меньшее х.Регистр 6 выполняет циклическийсдвиг содержимого на 31.ов И бит,осуществляя тем самым перестановкуместами содержимых младших и старших разрядов. Модуль счета счетчика10 равен тридцати двум.Блок 7 памяти для хранения кон 5 ф 1 ая й стант обладает емкостью 2кслов разрядностью11 од т, бит,1-1ш 11 ш,.,ш, - основания модулярной системы счисления, 1 - число оснований, причем ш2 р+к(р - фиксированное натуральное число),4 сЕ. ,В ячейки блока 7 памяти с адресами1977 28 п, 8 и+1,,8 п+7 записываются модулярные коды констант, относящихся к и-й иэ вычисляемых устройством функций (и 6 0, 1 И)Правило формирования содержимого блока 7 задается табл.1. Таблица 1 10 Хранимая констанАдрес ячейки та 8 и 8 п+1 А5,М 8 п+2208 и+3 М А АМ А 8 и+4 25 8 и+5 8 и+6;В В табл.1 через А . обозначаетА;ся числитель дроби а. = в -" в , предМставляющей собой приближение д-гокоэффициента усеченного степенногоряда, аппроксимирующего и-ю функцию 5Г(х) - Е а, . х,а, х е,1;:о40 А Е П =-рМ ,-рМ +1рм, (1) М А (р Ы,А макс /А. (,Макс К Максч 1 Блок 14 постоянной памяти управления имеет, емкость восьмиразрядных слов и служит для формирования в соответствии с табл.2 наборов значений управляющих сигналов Ь , Ь Ь К 45 где М, = ш 1,М - йатуральное число, определяющее точность вычисления и выбираемое изусловия501291977 Таблица 2 Номер слова Значение слова 1 7 О 0 1 0 0 1 0 1 3 0 0 0 2 0 0 1 10 0 0 0 О 0 0 0 О О 0 0 0 0 10 0 0 0 0 0 0 0 12-14 015 О О 0 0 0 О К(7) 3 1 4 0 5 0 6 0 7 1 8 0 9 О,Разрядность регистров 8,9,11,17и 19 и количество мультиплексоров вгруппах 12, 13 и 15 составляет Блоки 16,20 умножения и сложения реализуют соответствующие операции над целыми числами иэ диапазона модулярной системы счисления. Блок 21 осуществляет деление входного числа А, заданного модулярным кодом, на константу М.В основу вычисления элементарных функций положена аппроксимация функций рядами вида (1), не обязательно тейлоровскими. В частности, могут быть использованы степенные ряды, получаемые иэ разложений функций по ортогональным базисам Лежандра, Чебышева, Эрмита и другим,Из 0 0 О 1 0 0 0 1 О 1 0 О 1 0 0 1 1 0 1 0 0 0 0 0(1) вытекают следующие расчетныесоотношения для вычисления значения-ХЕ функций Е (х) при хь МГ= , Г=- (М С +В Е, ;(2)Р 11 В,= МА + А,Х (4)В =1 - (МА + А Х); (5) В = - (МА + А Х); (6) Для наиболее употребительных функций, включая тригонометрические(прямые и обратные), логарифмические, экспоненциального типа и другие, аппроксимация первыми шестью членами степенных разрядов рассматриваемого вида дает абсолютную по грешность от 10до 10Устройство работает следующим образом.По сигналу, подаваемому на установочный вход 3 устройства, сдвиговой регистр 6 обнуляется, а в счетчик 10 записывается двоичный код числа 31, после чего из блока 14 постоянной памяти управления по адресу "31", поступающего с выходов нулевого, первого, третьего и четвертого разрядов счетчика 10 на адресный вход блока 14, считывается начальной набор управляющих сигналов Ь Ь, (табл.2), который с выхо 20 да блока 14 постоянной памяти передается в управляющий регистр 18,На каждом такте работы устройства управляющие сигналы, сформированные в регистре 18 с первого по седьмой его выходов, подаются соответственно на вход управления сдвигом сдвигового регистра 6, управляющий вход выдачи кода регистра 17, управляющий вход приема кода регистра 9, управляющие входы групп мультиплексоров 12, 13 и 15 и вход обнуления накопительного регистра 19, и в зависимости от значений управляющих сигналов производятся действия, обеспечивающие поступление на входы блока 16 умножения требуемых операндов в текущем такте и формирование содержимых регистров 6,8,9,17 и 19 для очередного такта. Блок 16 умножения выполня 40 ет операцию модульного умножения операндов, поступающих на первый и второй входы соответственно с выходов групп мультиплексоров 12 и 13,45 модулярный код произведения с выхода блока 16 передается в регистр 8. Блок 20 сложения суммирует модулярные коды, сформированные на выходах регистров 8 и 19 и модулярный код суммы с выхода блока 20 посту 50 пает на информационный вход группы мультиплексоров 15 и входной регистр блока 21. Одновременно с этим содержимое 1-й группы разрядов с но 55 мерами 0,1,3 счетчика 1 О подается на адресные входы блока 7 памяти и блока 14, на адресные входы которых также подаются соответственно содержимое и группы младших разрядов сдвигового регистра 6 и содержимое старшего разряда счетчика .10, Из блока 7 памяти по адресу Ь+1 считывается модулярный кодочередной константы в регистр 11, а также подается на первый информационный вход группы мультиплексоров 15. Из блока 14 в регистр 18 считывается набор значений управляющих сигналов для очередного такта. При этом по сигналу, подаваемому с тактового входа 1 устройства на счетный вход счетчика 10, его содержимое увеличивается на единицу, в результате чЕго на выходах счетчика 10 Формируется адрес следующего управляющего слова.На предварительном (нулевом) такте работы устройства на управляющий вход приема кода регистра 9 подается сигнал и так как в данный момент на управляющем входе выдачи кода регистра 17 единичный сигнал отсутствует, то в регистр 9 через вход 5 аргумента устройства поступает модулярный код числителя Х значенияХв - аргумента Функции Й (х) подлежа- М гнщей вычислению, при этом двоичный код номера г Функции через вход 2 кода функции устройства записывается в младшие разряды сдвигового регистра 6. Параллельно с этим в регистр 18 из блока 14 считывается управляющее слово с нулевым адресом (табл.2), а в счетчике 10 получается адрес следующего управляющего слова.В ходе первого такта на управляющие входы групп мультиплексоров 12 и 13 подаются сигналы (табл.2),вследствие чего на выходы групп мультиплексоров 12 и 13 пройдут величины, поступающие соответственно на их информационные входы с выхода буферного регистра 9. Блок 16 умножения находит модулярный код числа Х,который запоминается в буферном регистре 8. В это время в регистр 11 из блокапамяти по адресу (8 т+ 1) считывается модулярный код константы А, накопительный регистр 19 обнуляется. В управляющий регистр 18 из блока 14 поступает управляющее слово для второго такта, а содержимое счетчика 10 наращивается.Блоки 20 сложения и деления на кон 1291977станту 21 на данном такте полезнойработы не выполняют,На втором такте на выходы группмультиплексоров 12 и 13 пройдут соответственно содержимые регистра 11 5и. регистра 9, блок 16 умножения получит модулярный код величиныАХ 1, который запоминается врегистре 8. Предыдущее содержимое регистра 8 в блоке 20 складывается с содержимым (в данныймомент нулевым) регистра 19, модулярный код величины Х с выхода бло 1ка 20 сложения передается в блок 21.Наряду с указанными действиями навтором такте из блока 7 памяти по адресу (8 г+2) считывается модулярныйкод величины М А, , который черезинформационный вход группы мультиплексоров 15 поступает в регистр 19.На третьем такте блок 20, складывая содержимое регистров 8 и 19,находит величину М А + А Х посад ,гтупающую во входной регистр блока 21. 25На первый и второй входы блока 16 умноженйя с выходов групп мультиплексоров 12 и 13 поступают соответственно величины М и Х , подаваемые на информационный вход группы мультиплек- З 0соров 12 через вход 4 константы устройства и информационный вход группымультиплексоров 13 с выхода регистра9, блок 16 умножения находит модулярный код величины М Х , запоминаемой1в регистре 8.Из блока 7 памяти поступает константа А з, в управляющем регистре18 формируется управляющее слово садресом "3", а регистр 19 обнуляется.На четвертом такте блок 20 сложения формирует величину М Х передаваемую в блок 21, блок 16 умножения получает модулярный код числа 45А Х из блока 7 памяти по адресу 8 г считывается константа М Акоторая записывается в регистр 11 ичерез информационный вход группымультиплексоров 15 проходит на его. выход и записывается в регистр 19,а в регистр 18 из блока 14 передается управляющее слово с адресом "0"В регистре б осуществляется обменсодержимым групп младших и старшихразрядов, при этом в группу младшихразрядов через вход 2 кода функцииустройства поступает двоичный кодномера Б функции 1, (х),вычисление которой совмещается с вычислениемфункции Е(х), а в регистр 9 черезвход 5 аргумента устройства принимает-ся модулярный код числителя Х соот 2ветствующего значения аргумента - .МНа последующих четырех тактах работы устройства (с пятого по восьмой) для функции Г(х) повторяются операции, выполненные на тактах с первого по четвертый для функции Г(х).В результате на тактах с пятого по восьмой в блок 21 соответственно поступают величины М А + А1, г З,г личие от четвертого такта на восьмом такте после перестановки местами содержимых групп младших и старших разрядов сдвигового регистра б в него через вход 2 кода функции устройства новая информация не поступает, соответственно прекращается поступление новой информации и через вход 5 аргумента устройства. На восьмом такте из блока 7 памяти по адресу 8 8+4 считывается константа М А, з, которая через информационный вход группы мультиплексоров 15 передается в регистр 19, из блока 14 в регистр 18 поступает управляющее слово с адресом "4", а на первом выходе счетчика 10 после наращивания его содержимого на единицу формируется код числа "5". Так как выполнение в блоке 21 операции занимает шесть тактов, то, начиная с восьмого такта, с выхода блока 21 в буферный регистр 17 начинают поступать обработанные .значения входных величин блока 21 в порядке их поступления на вход, В частности, на восьмом такте в регистр 17 поступает модулярный код величины У в соответствии с формулой (7).На девятом такте модулярный код числа У, из регистра 17 пересылается в регистр 9 и через информацион,ный вход группы мультиплексоров 12 и через информационный вход группы мультиплексоров 13 поступает на входы блока 16 умножения, который находит величину У запоминаемую в регистре 8, предыдущее содержимое регистра 8 в блоке 20 складывается с содержимым накопительного регистра 19 и полученная сумма М А,з+ А Х передается в блок 21. В регистре 18Формируется управляющее слово с адресом "5", регистр 19 обнуляется, а в буферный регистр 9 с выхода блока 21 поступает модулярный код числа В, в соответствии с Формулой (6).На десятом такте с выхоца блока 20 сложения в блок 21 поступает величина У блок 16 умножения находит произведение чисел М, В, , поданных на информационный вход группы мультиплексоров 12 и информационный вход группы мультиплексоров 13 соответственно. Из блока 7 памяти по адресу 8 г+6 считывается константа Азапоминаемая в регистре 11, в регистр 18 записывается шестое управляющее слово, регистр 19 обнуляется, а в буферный регистр 17 с выхода блока 21 поступает модулярный код числа Х .На одиннадцатом такте в блок 21 поступает величина МВв регистре 8 формируется модулярньш код произведения А, Х получаемый блоком 16, иэ блока 7 памяти по адресу (8:г+7) считывается константа М:АО,1которая через информационный вход группы мультиплексоров 1 5 передается в регистр 1 9, а в регистр 1 8 эаписыв а е тс я управляющее слово с адресом " 7 " . При этом после увеличения н а единицу содержимого счетчика 1 0 на первом е го выходе формируется дв оичный к од числа " 4 " .Н а двенадцатом такте блок 2 0 сложе ни я определяет модуля р ный код числа В ,в соответствии с формулой ( 4 ) , который с выхода блока 2 0 через информационный вход группы мультиплек с оров 1 5 поступает в накопительный регистр 1 9 . На первый и второй входы блэк а 1 6 умножения через и нф о рмационный вход группы мул ьтипле к соро в 1 2 и информационный вход группы мультиплексоров 1 8 с выходов буферных регистров 1 7 и 9 подаются соотв е т с тв е нно величины В , , и У , в ре 1 зультате чего их произведение получают в регистре 8. В регистр 17 поступает модулярный код числа У, в соответствии с формулой (7), в сдвиговом регистре 6 осуществляется обмен содержимыми групп младших и старших разрядов, в регистр 18 из блока 14 считывается управляющее слово с адресом "4".На последующих четырех тактах действия, выполненные на тактах с Формула изобретения Устройство для вычисления элементарных Функций в модулярной системе девятого по двенадцатый, повторяются,в результате чего в блок 21 поступают величины В, + В , У УМВз а по истечение шестнадцатого 5 такта в буферный регистр 17 с выхода блока 21 поступает модулярный кодчисла 2, в соответствии с формулой(7), Кроме того, на шестнадцатом такте в регистре 18 сформируется управ1 11ляющее слово с адресом "8На семнадцатом такте блок 20 сложения заканчивает вычисление величины В + В, У, поступающей вблок 21, модулярный код числа 2 изрегистра 17 пересылается в регистр9, а в регистр 17 поступают величины В.На восемнадцатом такте блок 16умножения получает произведение 20В 1, 2 запоминаемые в регистре 8,а регистр 19 обнуляется.В ходе девятнадцатого такта в накопительный регистр 19 при помощиблока 20 сложения и группы мультиплексоров 15 пересылается содержимоерегистра 8. При этом в регистр 17 свыхода блока 21 поступает величинаСв соответствии с формулой (3).30 На двенадцатом 1 акте величина С,умножается на константу М, а на двадцать первом такте полученное произведение блоком 20 сложения суммируется с содержимым накопительного регистра 19. В результате в блок 21 35поступает величина М С + В, 2с 1После выполнения указанных действийдля функции Г э(х) по истечение двадцать пятого такта в блок 21 поступает величина МС + В2,.На двадцать седьмом и тридцатьпервом тактах блок 21 завершает формирование величин Й и Й в соответствии с формулой (2). Модулярные ко ды искомых величин в укаэанных тактах снимаются с выхода 22 устройства, и на этом процесс вычисленияфункций в заданных точках заканчивается.Начиная с двадцать пятого такта,в предлагаемом устройстве можно начать вычисление новой пары значенийодной и той же или двух различныхфункций.счисления, содержащее сдвиговый регистр, блок памяти для хранения констант, счетчик, регистр констант, блок умножения, накопительный регистр, блок сложения, три буферных 5 регистра и блок постоянной памяти управления, причем вход кода задания функции устройства соединен с входами младших разрядов сдвигового регистра, вход обнуления которого соединен с установочным входом счетчика и является установочным входом устройства, выход блока памяти для хранения констант соединен с информационным входом регистра констант, выход блока умножения соединен с информационным входом первого буферного регистра, выход наполнительного регистра соединен с входом первого слагаемого блока сложения, вход аргумента устройства соединен с установочным входом второго буферного регистра, о т л и ч а ю щ е е с ятем, что, с целью повышения быстродействия, оно содержит блок деления на Константу, управляющий регистр и три группы мультиплексоров, причем тактовый вход устройства соединен со счетным входом счетчика, разрядный выход которого соединен с адрес 30 ным входом блока постоянной памяти управления, выход которого соединен с информационным входом управляющего регистра, с первого по седьмой выходы которого подключены соответствен- З 5 но к входу управления сдвигом сдвигового регистра, управляющему входу выдачи кода третьего буферного регистра, управляющему входу приема кода второго буферного регистра,уп 40 равляющим входам мультиплексоровпервой, второй, третьей групп и входу обнуления накопительного регистра, информационный вход третьего буферного регистра подключен к выходублока деления на константу, выход которого является выходом устройства,выход регистра констант, вход константы устройства, выходы третьегои второго буферных регистров соединены соответственно с информационными входами с первого по четвертыймультиплексоров первой группы, выходы которых соединены с входом первого сомножителя блока умножения, входвторого сомножителя которого соединен с выходами мультиплексоров второй группы, первый и второй информационные входы которых соединены соответственно с выходами третьего ивторого буферных регистров, выходтретьего буферного регистра соединенс информационным входом второго буферного регистра, выход первого буферного регистра соединен с входомвторого слагаемого блока сложения,выход которого соединен с входом блока деления на константу, вход блокапамяти для хранения констант и выходблока сложения соединены соответственно с первыми и вторыми информационными входами мультиплексоровтретьей группы, выходы которых соединены с информационным входом накопительного регистра, старшие и младшие разряды адресного входа блокапамяти для хранения констант соединены соответственно с выходами младших разрядов регистра сдвига и с выходами младших разрядов счетчика.г1291977 Составитель А. КлюевТехред И.Попович Коррек С. Шек едак Рогул аказ 272/48 3 В п 13035, 4 осква, Ж, Ра Проектная,4 зводственно-полиграфическое предприят жгород,Тираж Госуда елам и ственнообретен Подписн о комитета й и открыти шская наб.,

СмотретьЗаявка

3912158, 14.06.1985

НАУЧНО-ИССЛЕДОВАТЕЛЬСКИЙ ИНСТИТУТ ПРИКЛАДНЫХ ФИЗИЧЕСКИХ ПРОБЛЕМ ИМ. А. Н. СЕВЧЕНКО

КОЛЯДА АНДРЕЙ АЛЕКСЕЕВИЧ, СЕЛЯНИНОВ МИХАИЛ ЮРЬЕВИЧ

МПК / Метки

МПК: G06F 7/544, G06F 7/72

Метки: вычисления, модулярной, системе, счисления, функций, элементарных

Опубликовано: 23.02.1987

Код ссылки

<a href="https://patents.su/8-1291977-ustrojjstvo-dlya-vychisleniya-ehlementarnykh-funkcijj-v-modulyarnojj-sisteme-schisleniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления элементарных функций в модулярной системе счисления</a>

Предыдущий патент: Функциональный генератор и функциональный генератор

Следующий патент: Вычислительное устройство

Случайный патент: Коросниматель