Устройство для вычисления функций в модулярной системе счисления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1322268

Автор: Коляда

Текст

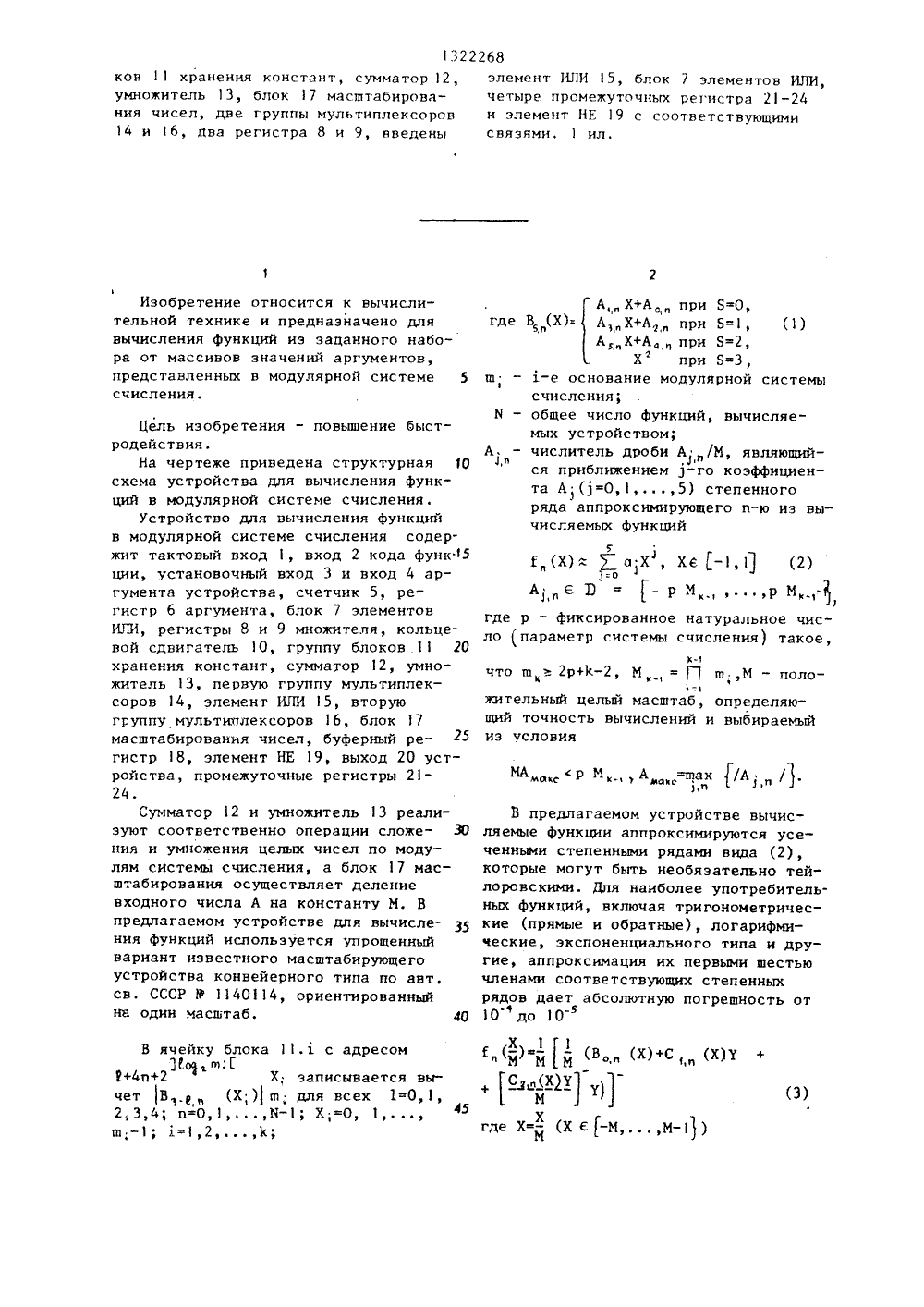

% О 1) 1 504 С 06 Р 7 544 7 ОПИСАНИЕ ИЗОБРЕТЕНИЯН АВТОРСКОМУ СВИДЕТЕЛЬСТВУ кий инстпроблем ГОСУДАРСТВЕННЫЙ КОМИТЕТ ССС ГЮ ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫ(56) Авторское свидетельство СССРУ 983707, кл. С 06 Г 7/544, 1980.Авторское свидетельство СССРР 1278839, кл. 6 06 Р 7/544, 1985.(54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ В МОДУЛЯРНОЙ СИСТЕМЕ СЧИСЛЕНИЯ(57) Изобретение относится к вычислительной технике и предназначено длявычисления функций из заданного набора от массивов значений аргументов,представленных в модулярной системесчисления. Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем, чтов устройство, содержащее счетчик 5,кольцевой сдвнгатель 10, группу бло(3) ковхранения констант, сумматор 12,умножитель 13, блок 7 масштабирования чисел, две группы мультиплексоров14 и 6, два регистра 8 и 9, введены Изобретение относится к вычислительной технике и предназначено для вычисления функций иэ заданного набора от массивов значений аргументов, представленных в модулярной системе 5 счисления. Цель изобретения - повышение быстродействия.На чертеже приведена структурная 10 схема устройства для вычисления функций в модулярной системе счисления.устройство для вычисления функций в модулярной системе счисления содержит тактовый вход 1, вход 2 кода функ 5 ции, установочный вход 3 и вход 4 аргумента устройства, счетчик 5, регистр 6 аргумента, блок 7 элементов ИЛИ, регистры 8 и 9 множителя, кольцевой сдвигатель 1 О, группу блоков 11 20 хранения констант, сумматор 12, умно- житель 13, первую группу мультиплексоров 14, элемент ИЛИ 5, вторую группу мультиплексоров 16, блок 7 масштабирования чисел, буферный регистр 8, элемент НЕ 19, выход 20 устройства, промежуточные регистры 2 в 24.Сумматор 12 и умножитель 13 реализуют соответственно операции сложе- ЗО ния и умножения целых чисел по модулям системы счисления, а блок 17 масштабирования осуществляет деление входного числа А на константу М. В предлагаемом устройстве для вычисления функций используется упрощенный вариант известного масштабирующего устройства конвейерного типа по авт, св. СССР Р 1140114, ориентированный нв один масштаб. 40 В ячейку блока 11.д с адресомо, щ;1+4 п+2 Х; записывается вычет В(Х;)ш; для всех 1=0 р 1, т - 1; 1 р 2 р,1 с; элемент ИЛИ 15, блок 7 элементов ИЛИ,четыре промежуточных регистра 21-24и элемент НЕ 9 с соответствующимисвязями, 1 ил,А Х+Аа и при Б=Ор где В (Х)= А Х+Агм при 8=1 рАХ+А, м при 8=2,Х при Б 3, ш - 1-е основание модулярной системы 1счисления; М - общее число функций, вычисляемых устройством; А, - числитель дроби А /Мр являющий.,м 1,и ся приближением 1-го коэффициента А (3 0,1. 5) степенного ряда аппроксимирующего и-ю из вычисляемых функций й(Х) - 2 а Х, Хь -1, 1 (2)А2 Г - р м,р м.; где р - фиксированное натуральное число (параметр системы счисления) такое,к-что тпъ 2 р+с, М, = Л т,М - положительный целый масштаб, определяющий точность вычислений и выбираемый из условия В предлагаемом устройстве вычисляемые функции аппроксимируются усеченными степенными рядами вида (2), которые могут быть необязательно тейлоровскими. Для наиболее употребительных функций, включая тригонометрические (прямые и обратные), логарифмические, экспоненциального типа и другие, аппроксимация их первыми шестью членами соответствующих степенных рядов дает абсолютную погрешность от 10 до 1 О м(М) М М (Вон (Х)+С(Х) +Х 1 Г 1(4)Устройство для вычисления функций в моцулярной системе счисленияработаеч следующим образом.Для приведения устройства в исходное состояние н кольцевой сдвигатель1 О посредством установочного входа 3 10устройства записывается двоичный кодединицы и после этого начинается циклический процесс формирования требуемой последовательности функциональных значений. В пределах каждого цик ла длиной в пять тактов выполняетсяодин и тот же набор действий.На всех тактах сумматор 12 осущест.вляет сложение по основаниям системысчисления величин, поступающих с выхода блока 7 элементов ИЛИ и буферного регистра 18, а умножитель 13 находит модулярный код произведения чисел, поступающих с выходов блока 17масштабирования и группы мультиплексоров 14. При этом модулярный кодсуммы с выхода сумматора 12 подаетсяв первый промежуточный регистр 21 ина нторой информационный вход группь 11 мультиплексорон 16, а модулярный код 30произведения запоминается в буферном регистре 18,Полезную работу сумматор 12 выполняет на нулевом, первом и четвертом, а умножитель 13 - на нулевом,втором и четвертом тактах циклов (такты циклов нумеруются, начиная с нуля),На каждом такте работы устройства содержимое счетчика 5, подается на младшие разряды адресного входа блоков 4011 хранения константы, а на старшиеразряды их адресных входов с выходарегистра 6 аргумента подается записанный в нем модулярный код некоторого числа Х Ри из блока 11.счи.45тывается 1.-я цифра модулярного кодачисла В (Х). Модулярный код это 3,-1, иго числа с выхода блоков 11 поступает на информационный вход второгопромежуточного регистра 22 и перный 50информационный вход группы мультиплексоров 16,На всех тактах управляющие сигналы (7 - б , сформированные н разрядах с нулевого по четвертый кольцево го сдвига теля 1 О, непосредственно иличерез логические элементы 15 и 19 подаются на управляющие входы соотнетстнующих блоков: Г, - на управляющие входы приема кода счетчика 5, регистра 6 и первый вход элемента ИЛИ 15;на входы разрешению приема регистров 21 и 23 и выдачи регистра 24; о - на селекторный вход группы мультиплексоров 14;- на управляющие входы приема кода регистров 8 и 9 и вход элемента НЕ 19; б - на входы разрешения приема регистров 22 и 24 и выдачи регистра 23 и второй вход элемента ИЛИ 15, После этого по сигналу, подаваемому через тактовый вход 1 устройства на счетные входы счетчика 5 и сдвигателя 10, содержимое первого из них увеличивается на единицу, а второго - сдвигается на один разряд в сторону старших разрядон.Согласно изложенному выше на начальном (нулевом) такте работы устройства в счетчик 5 посредством входа 2 кода функции устройства записывается двоичный код числа 4 п, а в регистр 6 через вход 4 аргумента устройства принимается модулярный код (ХХ Х) числа Х, определяющего требуемое значение Х/М аргумента Х функции, На последующих трех тактах (с первого по четвертый) блоки 11 хранения констант формируют соответ- ственно модулярные коды величин Х В (Х), В, (Х) и В (Х) (см.(1 и, так как на селекторный вход группы мультиплексоров 16 с выхода элемента ИЛИ 15 в первом, втором и третьем тактах поступает нулевой сигнал, то модулярные коды первых трех из указанных величин через первый информационный вход группы мультиплексоров 16 пройдут на ее выход и поступят во входной регистр блока 17 масштабирования. На четвертом такте б =1, поэтому модулярный код величийы В (Х) с выходов блоков 11 хранения констант поступит в регистр 22, при этом прежнее содержимое регистра 22 пересылается в регистр 24, а содержимое регистра 23 через первый вход элементов ИЛИ 7 подается на второй вход сумматора 12, на перный вход которого подается содержимое буферного регистра 18, Результат суммирования (его значение н данный момент несущественно) с выхода сумматора 12 через второй информационный вход груп13222 В ходе третьего цикла (такты с де сятого по четырнадцатый) наряду с выполнением описанных действий в связи с выполнением третьего функционального значения в десятом такте сумматор 2, складывая содержимое регист 50 ра 18 с выходной величиной блока 7 элементов ИЛИ (на нулевом такте каждого цикла она равна нулю), получает модулярный код числа С (Х)У, который через второй информационный вход 55 группы мультиплексоров 16 передается в блок 17 масштабирования (ввидуб =о =О), умножитель 13 находит модулярный код произведения чисел С, (Х) пы мультиплексоров 16 передается в блок 17 масштабирования чисел.В ходе тактов с пятого по девятьп, составляющих второй цикл работы устройства, описанные действия повторяются для второго элемента последовательности функциональных значений, подлежащих вычислению. Начиная с восьмого такта, с выхода блока 17 масштабирования чисел начнут поступать про- О масштабированные значения входных величин блока в порядке поступления последних на вход. В частности на восьмом такте на выходе блока 17 сформируется модулярный код величины У 15 (см.(4, который подается на второй вход умножителя 13 и ввиду о =1 записывается в регистр 8 с одновременной пересылкой прежнего его содержимого в регистр 8. 20 В девятом такте на второй вход умножителя 13 с выхода блока 17 поступает величина С (Х) (см, (4 и, так как в данный момент на селекторный 25 вход группы мультиплексоров 14 подается сигнал б =О, то на первый вход умножителя 3 через информационный вход группы мультиплексоров 14 поступит содержимое регистра 8. 30Умножитель 13 получает модулярный код произведения С (Х)У, который. за 3,1)поминается в буферном регистре 18 (на управляющий вход приема кода регистра 18 с выхода элемента НЕ 19 подает ся сигнал б=1). Одновременно с этим на девятом такте в регистр 22 с выхода блоков 1 хранения констант передается величина вида (1) при Б =3, необходимая для вычисления второго 40 функционального значения, а прежнее содержимое регистра 22 пересылается в регистр 24. 6 86(см, (4) ) и Х, запоминаемый в ре -гистре 18,В одиннадцатом такте сигнал (, =1,в результате чего величина Во (Х) нзО,лрегистра 24 через второй вход элементов ИЛИ 7 пройдет на выход и поступитна вход сумматора 12, на другой входкоторого с выхода буферного регистра18 подается величина С, (Х)У, сумматор 12 находит модулярный код числаВ (Х)+С,(Х)У, который поступает в0,лрегистр 2 1 с одновременной и ер е сылкой е го пр ежн е го содержимого в регис тр 2 3 , На тринадцатом такте в регис тр 8 с выхода блока 1 7 передаетсяпрома сштаби ро в ан н ое значение квадратааргумента второй функции, а к од числаУ и з регистра 8 пересылается в регнс т р 9 ( 17 = 1 ) .В ходе четвертого цикла работыустройства ( так ты с пятнадцатого подевятнадцатый) наряду с действиями ,выполняемыми в св я зн с выполнениемвторого , третьего и четвертого функциональных значений осуществляетсяследующееНа семнадцатом такте с выхода блока 1 7 на вход умножителя 1 3поступает модуля рный код в еличиныС(Х) УМ (на другой вход умножителя 13"черезинформационный вход группы мультиплексоров 14 (б =1) подается содержимое регистра 9, умножитель 13 получает модулярный код произведения- в вУ, который запоминается вбуферном регистре 18, где он хранится в теченне следующего такта (на восемнадцатом такте запись в регистр18 ввиду С =О запрещена),На девятнадцатом такте при записив регистр 22 новой информации содержимое регистра 23 через первый входэлементов ИЛИ 7 подается на вход сумматора 12, а на другой его вход подается содержимое буферного регистра18, Код, получаемый сумматором 12 через второй информационный вход группы мультиплексоров 16, передается вблок 17 масштабирования чисел, который по истечении двадцать пятого такта завершит вычисление первого элемента заданной последовательностифункциональных значений (см. (3,при этом модулярный код искомого значения числителя дроби (3) снимаетсяс выхода 22 устройства, модулярный1322268 Составитель А,КлюевТехред Л.Олийнык Корректор Л. Пилипенко Редактор П,Гереши Заказ 2865/45 Тираж 672 ПодписноеВНИИПИ Государственного комитета СССРпо делам изобретений и открытий113035, Москва, Ж, Раушская наб.,д.4/5 Производственно-полиграфическое предприятие,г,ужгород,ул.Проектная,4 код-фуцкцо;гьцо ц;чгця1 11) снимается с выхда 22 ус грой - стна по истечении (155)-го такга. Формула изобретения Устройство для Вычисления функций в модулярцой системе счисления, содержащее счетчик, кол невой спвигатель, группу блоков храцеция констант, сумматор, умцожитель, блок мас штабирования чисел, две группы мультиплексоров, два регистра множителя, регистр аргумента и буферный регистр, причем тактовый вход устройства сое - динен со счетным входом счетчика,раз ряды выхода которого соединены смладшими разрядами адресного входа блоков хранения констант группы, выход первого регистра множителя соединен с информационным входом второго д) регистра множителя, выход которого соединен с первыми информационными входами мультиплексоров первой группы, выходы которых соединены с входом первого сомножителя умножителя, 25выход которого соединен с информационным входом буферного регистра,выход которого соединен с входом первого слагаемого сумматора, выходыблоков хранения констант группы соединены с первыми информационными входами соответствующих мультиплексороввторой группы, выход блока масштабирования чисел является выходом устройства, о т л и ч а ю щ е е с я тем,что, с целью повышения быстродействия,оно содержит элемент ИЛИ, блок элементов ИЛИ, четыре промежуточных регистра и элемент НЕ, причем тактовыйвход устройства соединен с входом 40разрешения сдвига кольцевого сдвигателя, информационный вход которогосоединен с установочным входом устройства, входы кода функции и аргумента которого соединены соответственно с информационными входами счетчика и регистра аргумента, разрядывыхода которого соединены соответственно со старшими разрядами адресного входа блоков хранения констант 50 группы, выход сумматора соединен совторыми ицформациоццымц входами нультцплексоров второй группы и с ццформационным входом первого громежуточного регистра, выходы мультицекоров второй группы соединены с входомблока масштабирования чисел, выходкоторого соединен с входом второго сомножителя умцожителя и с информационным входом первого регистра множителя, выходкоторого соединен с вторыми информационными входами мультиплексоров первойгруппы, выходы блоков хранения констант группы соединены с информационным входом второго промежуточного регистра, выходы первого и второго промежуточных регистров соединены соответственно с информационными входамитретьего и четвертого промежуточныхрегистров, выходы которых соединенысоответственно с первым и вторым входами блока элементов ИЛИ, выход которого соединен с входом второго слагаемого сумматора, разряды выходакольцевого сдвигателя соединены соответственно с первым входом элементаИЛИ, с входом разрешения приема первого промежуточного регистра, с управляющим входом мультиплексоров первой группы, с входом элемента НЕ и свторым входом элемента ИЛИ, выход которого соединен с управляющим входоммультиплексоров второй группы, входыразрешения приема регистра аргументаи счетчика соединены с первым входомэлемента ИЛИ, второй вход которогосоединен с входами разрешения приемавторого и четвертого промежуточныхрегистров и с входом разрешения выдачи третьего промежуточного регистра,вход разрешения приема которого соединен с входом разрешения приема первого промежуточного регистра и с входом разрешения выдачи четвертого промежуточного регистра, вход элементаНЕ соединен с входами разрешения прие.ма первого и второго регистров множителя, выход элемента НЕ соединен свходом разрешения приема буферногорегистра.

СмотретьЗаявка

3938737, 01.08.1985

НАУЧНО-ИССЛЕДОВАТЕЛЬСКИЙ ИНСТИТУТ ПРИКЛАДНЫХ ФИЗИЧЕСКИХ ПРОБЛЕМ ИМ. А. Н. СЕВЧЕНКО

КОЛЯДА АНДРЕЙ АЛЕКСЕЕВИЧ

МПК / Метки

МПК: G06F 7/544, G06F 7/72

Метки: вычисления, модулярной, системе, счисления, функций

Опубликовано: 07.07.1987

Код ссылки

<a href="https://patents.su/5-1322268-ustrojjstvo-dlya-vychisleniya-funkcijj-v-modulyarnojj-sisteme-schisleniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления функций в модулярной системе счисления</a>

Предыдущий патент: Устройство для вычисления обратной функции

Следующий патент: Устройство для извлечения корня из суммы квадратов трех чисел

Случайный патент: Устройство для распознавания речевых образцов