Параллельный сумматор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1363188

Автор: Ткаченко

Текст

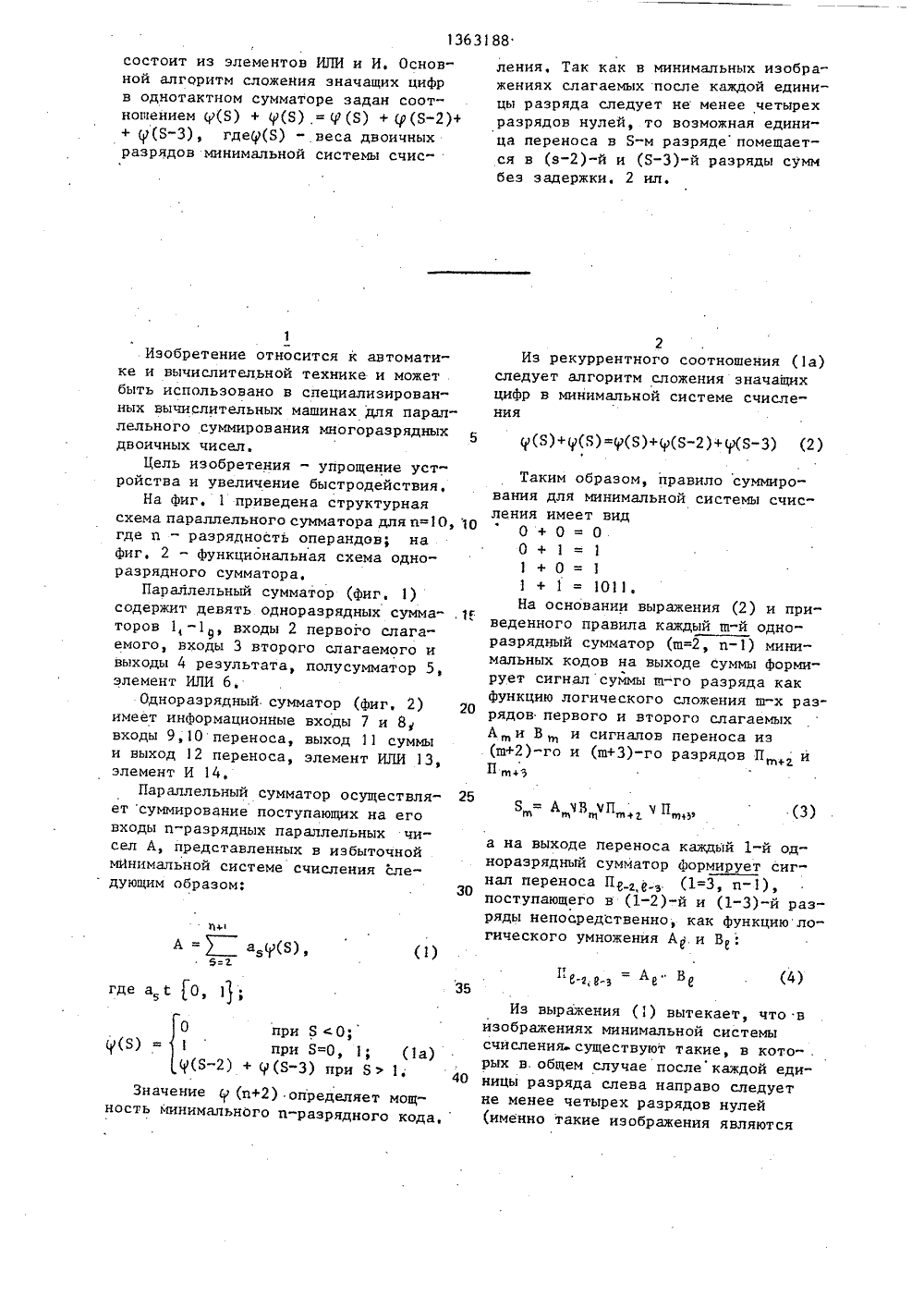

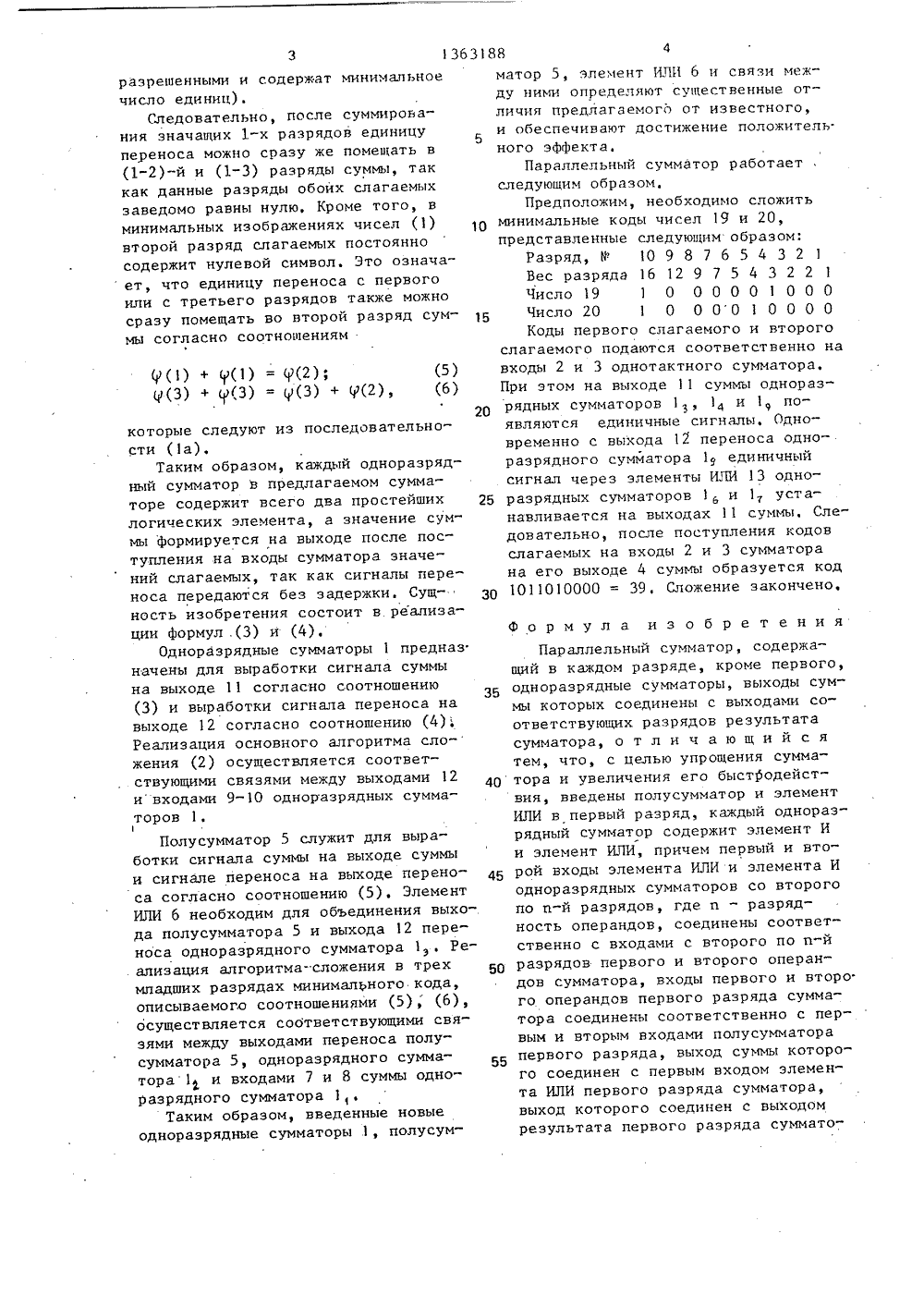

(ю 4 С 06 Р 7/49 О гические осноРадио, 1972,ство СССР /49, 1975 ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИ ОПИСАНИЕ ИЗОБ МУ СВИДЕТЕПЬСТ(57) Изобретение предназначено дляпостроения высоконадежных сверхбыстродействующих специаЛизированныхмикропроцессов.Цель изобретения -упрощение устройства и увеличениебыстродействия, Однотактный сумматор содержит одноразрядные сумматоры 1, полусумматор 5, элемент ИЛИ 6,а каждый одноразрядный сумматор 1(4) 35 гдааоО, 1; состоит из элементов ИЛИ и И, Основ"ной алгоритм сложения значащих цифрв однотактном сумматоре задан соот"ношением (Б) + (1(Я),= 9(Я) + (Р(Б)++ (7(Б)р где 1(Б) - веса двоичныхразрядов минимальной системы счис 1Изобретение относится к автомати"ке и вычислительной технике и можетбыть использовано в специализированных вычислительных машинах для парал"лельного суммирования многоразрядныхдвоичных чисел.Цель изобретения - упрощение устройства и увеличение быстродействия.На фиг. 1 приведена структурнаясхема параллельного сумматора для п=10, 10где и - разрядность операндов; наФиг, 2 - функциональная схема одноразрядного сумматора,Параллельный сумматор (Фиг. 1)содержит девять одноразрядных сумма",1 р:торов 1, "19, входы 2 первого слага"емого, входы 3 второго слагаемого ивыходы 4 результата, полусумматор 5,элемент ИЛИ 6Одноразрядный сумматор (фиг. 2) 20имеет информационные входы 7 и 8входы 9,10 переноса, выход 11 суммыи выход 12 переноса, элемент ИЛИ 13,элемент И 14,Параллельный сумматор осуществляет суммирование поступающих на еговходы п-разрядных параллельных чисел А, представленных в избыточнойминимальной системе счисления следующим образом: 30 0 при Я О; у(Б) =при Я=О, 1; (1 а)(Б) + У(Я) при Б1.Значение(и+2) определяет мощность минимального и-разрядного кода. ления. Так как в минимальных изображениях слагаемых после каждой единицы разряда следует не менее четырех разрядов нулей, то возможная единица переноса в Б-м разряде помещается в (з)-й и (Я)-й разряды сумм без задержки. 2 ил. 2Из рекуррентного соотношения (1 а) следует алгоритм сложения значащих цифр в минимальной системе счисле- ния(Я)+(Я) =у(Б)+фБ)+фЯ) (2) Таким образом, правило суммирования для минимальной системы счисления имеет вид0 + О = ОО + 1 = 11 + О = 11 + 1 = 1011,На основании выражения (2) и принаданного правила каудый и-й однораярядНьй сумматор Гмд 2, и) минимальных кодов на выходе суммы формирует сигнал суммы ш-го разряда какфункцию логического сложения ш-х разрядов первого и второго слагаемыхАу,и В, и сигналов переноса из(ш+2)-го и (ш+3)-го разрядов П иП а на выходе переноса каждый 1-й одноразрядный сумматор формирует сигнал переноса Пе-г,е з (1=3, п), поступающего в (1-2)-й и (1-3)-й разряды непосредственно, как Функцию логического умножения А.и В. Из выражения (1) вытекает, что в изображениях минимальной системы счисления существуют такие, в кото- . рых в. общем случае после каждой единицы разряда слева направо следует не менее четырех разрядов нулей (именно такие изображения являютсяразрешенными и содержат минимальное число единиц),Следовательно, после суммирования значащих 1-х разрядов единицу переноса можно сразу же помещать в (1-2)-й и (1-3) разряды суммы, так как данные разряды обоих слагаемых заведомо равны нулю, Кроме того, в минимальных изображениях чисел (1) второй разряд слагаемых постоянно содержит нулевой символ. Это означа ет, что единицу переноса с первого или с третьего разрядов также можно сразу помещать во второй разряд суммы согласно соотношениям4(1) + 4(1) = 2); (5) 1(3) + С 7(3) = 1(3) + У(2), (6)которые следуют из последовательности (1 а).Таким образом, каждый одноразрядный сумматор в предлагаемом сумматоре содержит всего два простейшихлогических элемента, а значение сум"мы формируется на выходе после поступления на входы сумматора значений слагаемых, так как сигналы переноса передаются без задержкиСущность изобретения состоит в. реализации формул .(3) и (4).Одноразрядные сумматоры 1 предназначены для выработки сигнала суммына выходе 11 согласно соотношению(3) и выработки сигнала переноса навыходе 12 согласно соотношению (4).Реализация основного алгоритма сложения (2) осуществляется соответствующими связями между выходами 12и входами 9-10 одноразрядных сумматоров 1.1Полусумматор 5 служит для выработки сигнала суммы на выходе суммыи сигнале переноса на выходе переноса согласно соотношению (5), ЭлементИЛИ 6 необходим для объединения выхода полусумматора 5 и выхода 12 переноса одноразрядного сумматора 1. Ре. ализация алгоритма-сложения в трехмладших разрядах минимального кода,описываемого соотношениями (5); (6),осуществляется соответствующими связями между выходами переноса полусумматора 5, одноразрядного сумматора 1 и входами 7 и 8 суммы одно"разрядного сумматора 1Таким образом, введенные новыеодноразрядные сумматоры 1, полусумматор 5, элемент ИЛИ 6 и связи между ними определяют существенные отличия предлагаемого от известного,и обеспечивают достижение положитель.ного эффекта,Параллельный сумматор работаетследующим образом,Предположим, необходимо сложитьминимальные коды чисел 19 и 20,представленные следующим образом:Разряд, 1 10 9 8 7 6 5 4 3 2 1Вес разряда 16 12 9 7 5 4 3 2 2 1Число 19 1 0 О О О О 1 О О ОЧисло 20 1 0 0 00 1 0 0 0 0Коды первого слагаемого и второгослагаемого подаются соответственно навходы 2 и 3 однотактного сумматора,При этом на выходе 11 суммы однораз 20 рядных сумматоров 1 14 и 19 появляются единичные сигналы. Одновременно с выхода 12 переноса одноразрядного сумматора 1 единичныйсигнал через элементы ИЛИ 13 одно 25 разрядных сумматоров 1 и 17 устанавливается на выходах 11 суммы, Сле"довательно, после поступления кодовслагаемых на входы 2 и 3 сумматорана его выходе 4 суммы образуется код1011010000 = 39Сложение закончено. Формула изобретенияПараллельный сумматор, содержащий в каждом разряде, кроме первого,одноразрядные сумматоры, выходы суммы которых соединены с выходами соответствующих разрядов результатасумматора, о т л и ч а ю щ и й с ятем, что, с целью упрощения сумма О тора и увеличения его быстсодействия, введены полусумматор и элементИЛИ в первый разряд, каждый одноразрядный сумматор содержит элемент Ии элемент ИЛИ, причем первый и вто рой входы элемента ИЛИ и элемента Иодноразрядных сумматоров со второгопо и-й разрядов, где и - разрядность операндов, соединены соответственно с входами с второго по и-йразрядов первого и второго операндов сумматора, входы первого и второ.го операндов первого разряда сумматора соединены соответственно с первым и вторым входами полусумматорапервого разряда, выход суммы которого соединен с первым входом элемента ИЛИ первого разряда сумматора,выход которого соединен с выходомрезультата первого разряда суммато5 1 Зб 3188в ра, выход элемента ИЛИ одноразрядно- мента ИЛИ одноразрядного сумматора го сумматора данного разряда соеди- первого разряда соединены с выходом нен с выходом суммы данного одно- переноса одноразрядного сумматора разрядного сумматора, яыход элемента аторого раяряда, выход переноса 1-го И однораярядного сумматора данного однораярядного сумматора г 1"3, ,п-.Ц разряда соединен с выходом переноса соединен с третьим и четвертым одноразрядного сумматора данного раз" входами элемента ИЛИ соответственно ряда, выход переноса полусумматора (1-2)-го и (1-3)-го одноразрядных первого разряда соединен с первыми 10 сумматоров, выход переноса однораэ" входами элемента И и элемента ИЛИ рядного сумматора третьего разряда одноразрядного сумматора первого раэ-, соединен с вторым входом элемента ряда, вторые входы элемента И и зле- ИЛИ первого разряда, 7 8 8 Ю Составитель М. Есенина Редактор А. Долинич Техред Л.Олейник Корректор М. Пожо Заказ 63 б 2/39 Тир,аж 671 Подписное ВНИИПИ Государственного комитета СССРпо делам изобретений и открытий113035, Москва, Ж, Раушская наб., д. 4/5Производственно"полиграфическое предприятие, г. Ужгород, ул, Проектная, 4

СмотретьЗаявка

4098657, 21.05.1986

КРАСНОДАРСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНО-ИНЖЕНЕРНОЕ УЧИЛИЩЕ РАКЕТНЫХ ВОЙСК

ТКАЧЕНКО АЛЕКСАНДР ВАСИЛЬЕВИЧ

МПК / Метки

МПК: G06F 7/49

Метки: параллельный, сумматор

Опубликовано: 30.12.1987

Код ссылки

<a href="https://patents.su/4-1363188-parallelnyjj-summator.html" target="_blank" rel="follow" title="База патентов СССР">Параллельный сумматор</a>

Предыдущий патент: Ассоциативное арифметическое устройство

Следующий патент: Узел формирования переноса

Случайный патент: Шихта для изготовления огнеупорных изделий