Преобразователь двоично-десятичных чисел в двоичные

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1003068

Авторы: Распутный, Сальникова

Текст

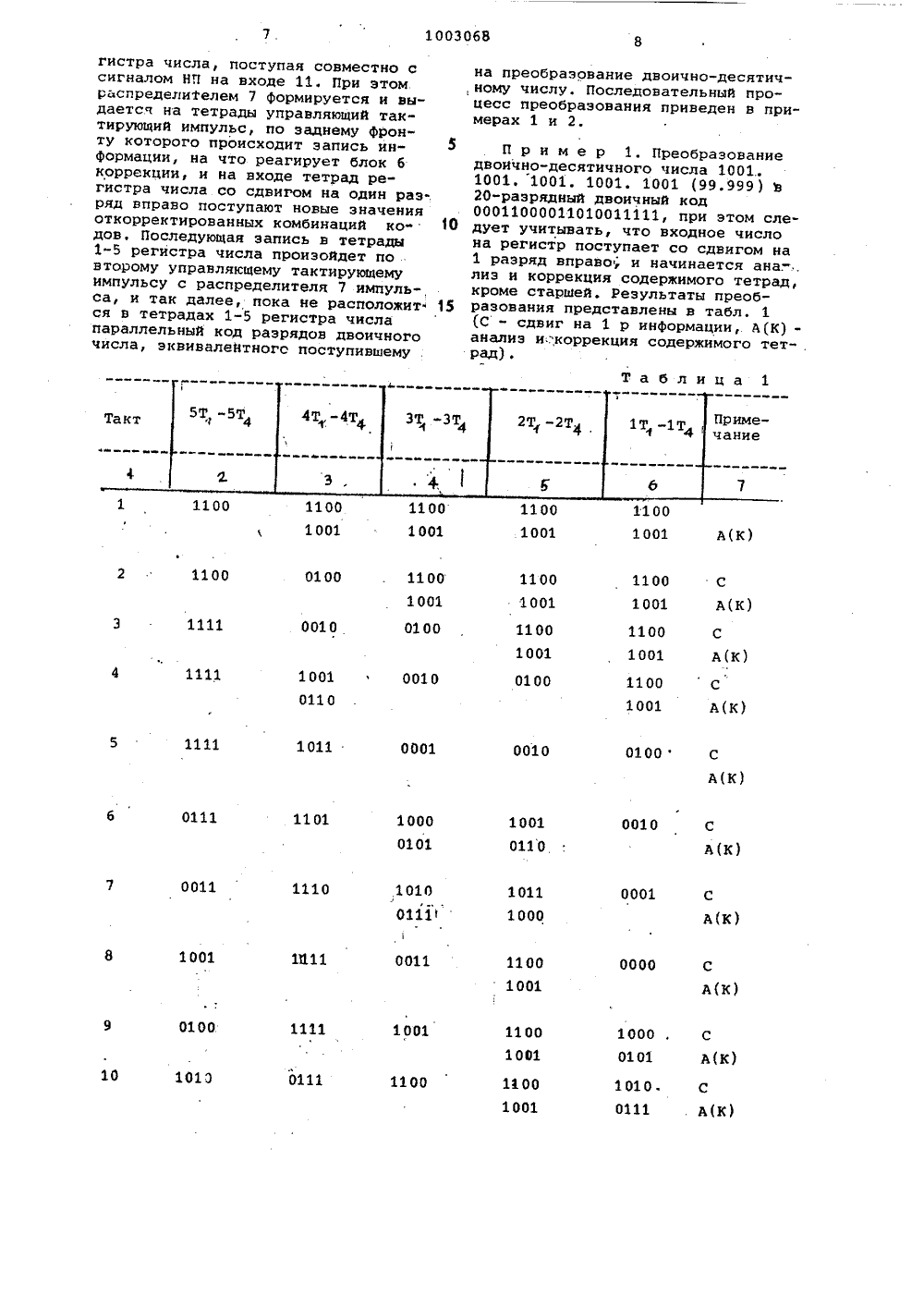

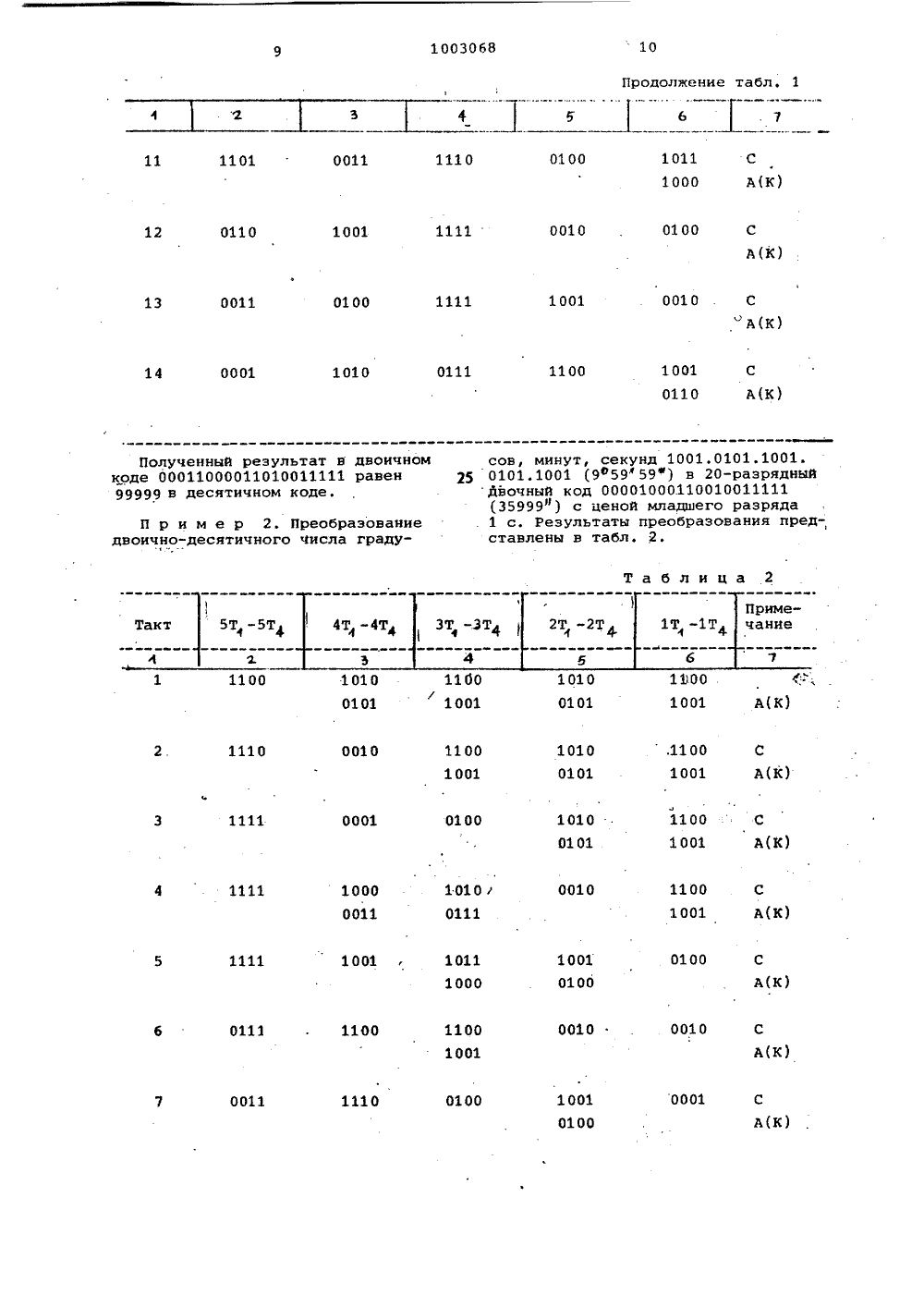

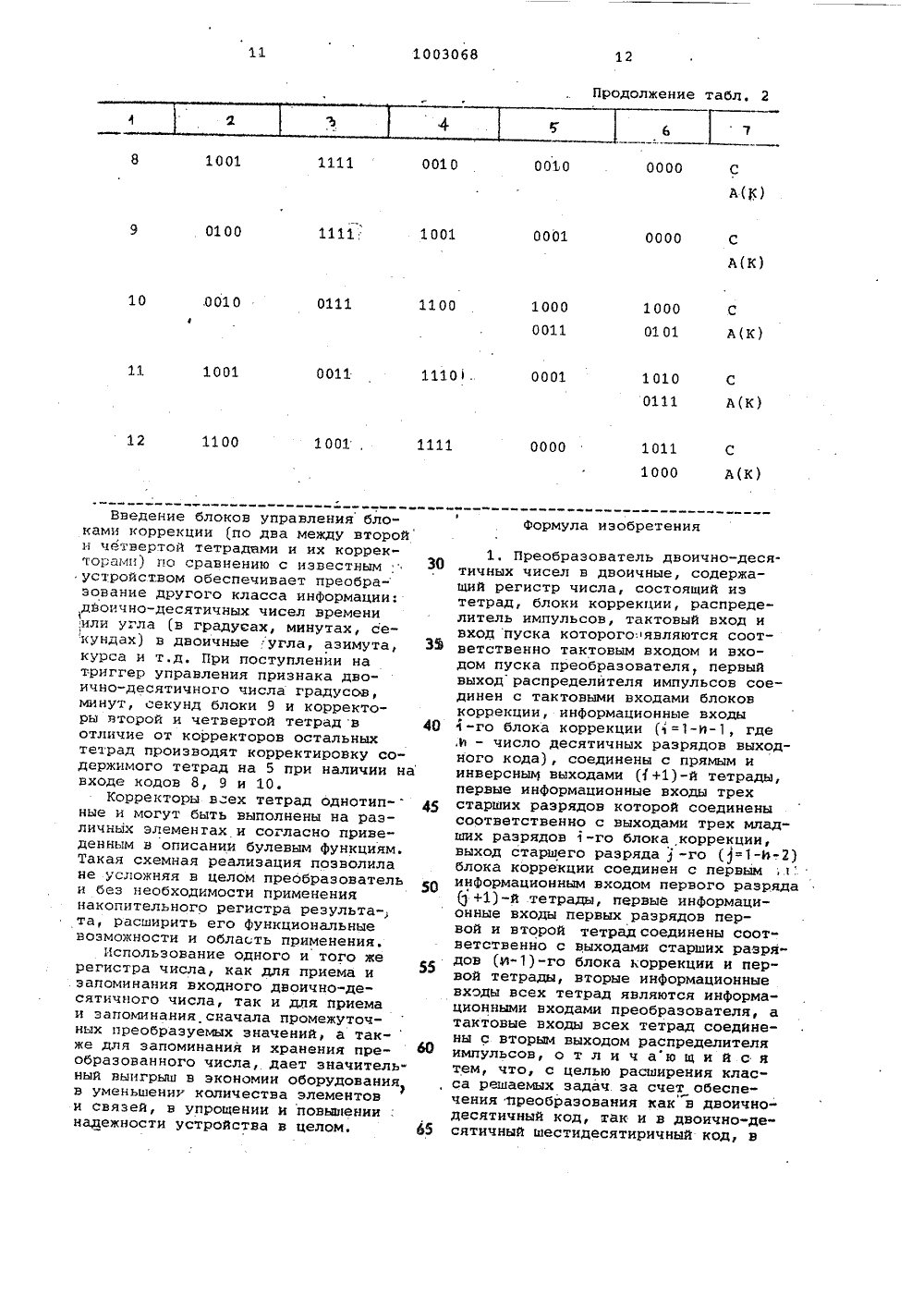

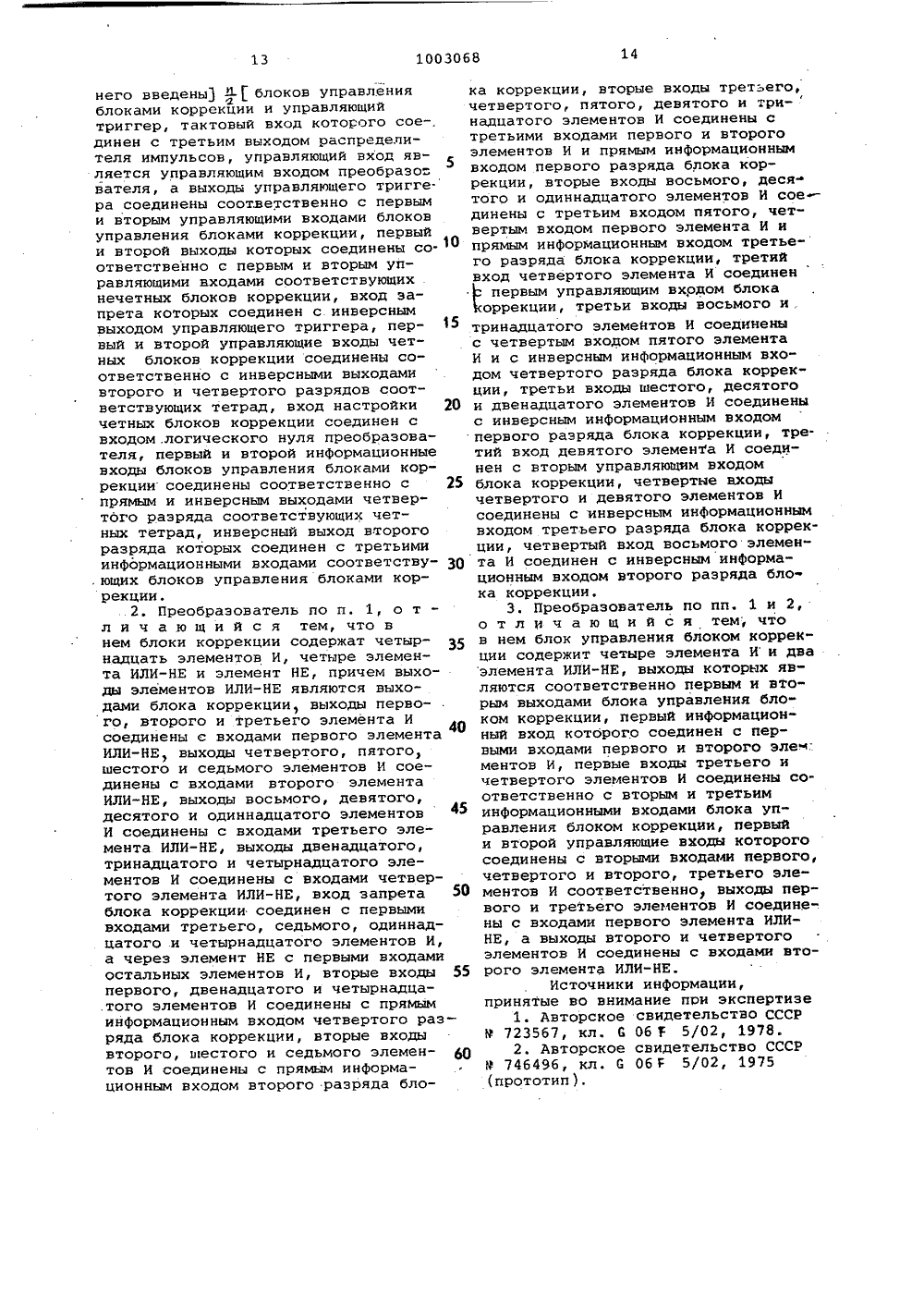

ОПИСАНИЕ ииИЗОБРЕТЕНИЯ Союз СоветскихСоциапистичеснивРеспублик К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(22) Заявлено 20.04.81 (21) 3276773/18-24 1 эт 3 М КПф с присоединением заявки Но(23) Приоритет 606 р 5/02 Государственный комитет СССР оо делам изобретений и открытийОпубликовано 07, 03.83,Бюллетень Но 9 Дата опубликования описания 07.03835 Изобретение относится к автома- тике и цифровой вычислительной технике и может быть использовано в составе систем сбора и обработки информации.Известен преобразователь двоично-десятичных чисел в двоичные, содержащий сдвигаьщне регистры, разделенные на тетрады, блоки коррекции по числу.тетрад преобразуемого числа, регистр результата, блок управления и генератор серий импульсов 1 1)Недостаток известного устройства состоит в ограниченном классе решаемых задач, что связано с невозможностью преобразования кода угловых величин в двоичный код.Наиболее близким по технической сущности и схемному построению к изобретению является преобразователь двоично-десятичных кодов в двоичные, содержащий регистр, состоящий иэ тетрад, распределитель импульсов и блоки коррекции по числу тетрад 2.Недостатком данного преобразователя является воэможность преобразования двоично-десятичных кодов времени (угла, азимута и т.д) непосредствен но в двоичный код и сравнительно.бо лысой обьем аппаратуры.Целью изобретения является расширение класса решаемых задач эа счет обеспечения воэможности преобразования как двоично-десятичных . кодов, так и двоично-десятично-шестидесятиричных кодов в "двоичный код.Поставленная цель достигается тем, что преобразователь двоичнодесятичного кода в двоичный код, содержащий регистГ числа, состоящий из тетрад, блоки коррекции, .распределитель импульсов, тактовый вход и вход пуска которого являются соответственно тактовым входом и вхо дом пуска преобразователя, первый выход распределителя. импульсов соединен с тактовыми входами блоков коррекции, информационные входы 1-го блока коррекции (=1-л), где п - число десятичных разрядов выходного кода, соединены с прямым и инверсным выходами (+1)-й тетрады первые информационные входы трех старших разрядов которой соединены соответственно с выходами трех младших разрядов -го блока коррекции, выход старшего разряда )-го =1-0-2) ,блока коррекции соединен с первыминформационным входом первого разряда +1 )-й тетрады, первые информационные входы первых разрядовпервой и второй тетрад соединенысоответственно с выходами старшихразрядов (и)-го блока коррекции ипервой тетрады, вторые информационные входы всех тетрад являются информационными входами преобразователя, а тактовые входы всех тетрадсоединены с вторым выходом распределителя импульсов, введены в "( блоков управления блоками коррекцйи иуправляющий триггер, тактовый вход которого соединен с третьим выходом распределителя импульсов, управляю щий вход является управляющим входом преобразователя, а выходы управляющего триггера соединены соответственно с первым и вторым управляющими входами блоков управления 20 блоками коррекции, первый и второй выходы которых соединены соответственно с первым и вторым управляющими входами соответствующих нечетных блоков коррекции, вход запрета кото рых соединен с инверсным выходом управляющего триггера, первый и второй управляющие входы четных блоков коррекции соединены соответственно с инверсными выходами второго и чет О вертного разрядов соответствующих тетрад, вход настройки четных блоков коррекции соединен с входом логического нуля преобразователя, первый и второй информационные входи у 5 блоков управления блоками коррекции . соединены соответственно с прямым и инверсным выходами четвертого разряда соответствующих четных тетрад, инверсный выход второго разряда которых соединен с третьими информационными входами соответствующих блоков управления блоками коррекции.При этом в нем блоки коррекции содержат четырнадцать элементов И, четыре элемента ИЛИ-НЕ и элемент ЙЕ, причем выходы элементов ИЛИ-НЕ являются выходами блока коррекции, выходы первого, второго и третьего элемента И соединены с входами первого элемента ИЛИ-НЕ, выходы чет О вертого, пятого, шестого и седьмого элементов И соединены с входами второго элемента ИЛИ-НЕ, выходы восьмого, девятого, десятого и одиннадцатого элементов И соединены с вхо дами третьего элемента ИЛИ-НЕ, выходы двенадцатого, тринадцатого и четырнадцатого элементов И соединены с входами четвертого элемента ИЛИНЕ, вход запрета блока коррекции соеО динен с первыми входами третьего, седьмого, одиннадцатого и четырнадцатого элементов И, а через элемент НЕ с первыми входами остальных элементов И, вторые входы первого, две надцатого и четырнадцатого элементов И соединены с прямым информационным входом четвертого разряда блока коррекции, вторые входы второго, шестого и седьмого элементов И соединены с прямьм информационным входом второго разряда блока коррекции, вторые .входы третьего, четвертого, пятого, девятого и тринадцатого элементов И соединены с третьими входами первого и второго элементов И и прямым информационным входом первого разряда блока коррекции, вторые входы восьмого, десятого и одиннадцатого элементов И соединены с третьим входом пятого, четвертым входом первого элемента И и прямым информационным входом третьего разряда блока коррекции, третий вход четвертого элемента И соединен с первым управляющим входом блока коррекции, третьи входы восьмого и тринадцатого элементов И соединены с чет)вертым входом пятого элемента И и с инверсным информационным входом четвертого разряда блока коррекции, третьи входы шестого, десятого и двенадцатого элементов И соединены с инверсным информационным входом первого разряда блока коррекции, третий вход девятого элемента И соединен с вторым управляющим входом блока коррекции, четвертые входы четвертого и девятого элементов И соединены с инверсным информационным входом третьего разряда блока коррекции, четвертый вход восьмого элемента И соединен с инверсным информационным входом второго разряда блока коррекции еКроме того, в нем блок управленияблоком коррекции содержит четыреэлемента И и два элемента ИЛИ-НЕ,выходы которых являются соответственно первым и вторым выходами блокауправления блоком коррекции, первыйинформационный вход которого соединен с первыми входами первого и второго элементов И, первые входы третьего и четвертого элементов И соединены соответственно с вторым итретьим информационными входами блокауправления блоком коррекции, первыйи второй управляющие входы которогосоединены с вторыми входами первого,четвертого и второго, третьего элементов И соответственно, выходы первого и третьего элементов И соединены с входами первого элемента ИЛИ-НЕ,а выходы второго и четвертого элементов И соединены с входами второгоэлемента ИЛИ-НЕ,На фиг, 1 приведена структурная схема предлагаемого преобразователя, на фиг. 2 - вариант реализации блока коррекции,(К 1000 0101 1001 110 100 0100 1010 011 1100 1010 С0111 . А(К) 10 гистра числа, поступая совместно ссигналом НП на входе 11. При этомраспределителем 7 формируется и выдаетсч на тетрады управляющий тактирующий импульс, по заднему фронту которого происходит запись информации, на что реагирует блок 6коррекции, и на входе тетрад регистра числа со сдвигом на один раз-,ряд вправо поступают новые значенияоткорректированных комбинаций ко" 10дов. Последующая запись в тетрады1-5 регистра числа произойдет повторому управляющему тактирующемуимпульсу с распределителя 7 импуль-,са, и так далее, пока не расположит 15ся в тетрадах 1-5 регистра числапараллельный код разрядов двоичногочисла, эквивалеитногс поступившему на преобразование двоично-десятич,ному числу. Последовательный процесс преобразования приведен в примерах 1 и 2. П р и м е р 1. Преобразование двоично-десятичного числа 10011001. 1001. 1001. 1001 (99.999 ) Ъ 20-разрядный двоичный код00011000011010011111, при этом следует учитывать, что входное число на регистр поступает со сдвигом на 1 разряд вправо, и начинается ана. - . лиз и коррекция содержимого тетрад, кроме старшей. Результаты преобразования представлены в табл. 1 (С - сдвиг на 1 р информации, А(К)- анализ и:.;коррекция содержимого тет- . Рад)еТаблица 1(35999 я) с ценой младшего разряда1 с. Результаты преобразования представлены в табл. 2.(к 0011 001 00 1110 . 1010 0111 СА(К 1100 1 001 011 С 000 А 000 Формула изобретен Введение блоков управления блоками коррекции (по два между второй и четвертой тетрадями и их корректорами) по сравнению с известным устройством обеспечивает преобра- зование другого класса информации: ,дйоично-десятичных чисел времени или угла (в градусах, минутах, секундах) в двоичные :угла, азимута, курса и т.д. При поступлении на триггер управления признака двоично-десятичного числа градусов, минут, секунд блоки 9 и корректоры второй и четвертой тетрад в отличие от корректоров остальных тетрад производят корректировку содержимого тетрад на 5 при наличии на входе кодов 8, 9 и 10.Корректоры в:ех тетрад однотипные и могут быть выполнены на различных элементах и согласно приве" денным в описаний булевым функциям. Такая схемная реализация позволила не усложняя в целом преобразователь и без необходимости применения накопительного регистра результа" та, расширить его функциональные воэможности и область применения.использование одного и того же регистра числа, как для приема и .запоминания входного двоично-десятичного числа, так и для приема и запоминания сначала промежуточных преобразуемых значений, а так-же для запоминания и хранения преобразованного числа, дает значительный выигрыш в экономии оборудования в уменьшениг количества элементов и связей, в упрощении и повышении; надежности устройства в целом. 1, Преобразователь двоично-десятичных чисел в двоичные, содержащий регистр числа, состоящий изтетрад, блоки коррекции, распределитель импульсов, тактовый вход ивход пуска которого. являются соответственно тактовым входом и входом пуска преобразователя, первыйвыход распределителя импульсов соединен с тактовыми входами блоковкоррекции, информационные входы 40 1-го блока коррекции (1=1-И, где,И - число десятичных разрядов выходного кода), соединены с прямым иинверсныМ выходами (1 +1)-й тетрады,первые информационные входы трехстарших разрядов которой соединенысоответственно с выходами трех младших разрядов 1-го блока коррекции,выход старшего разряда 1 -го (=1-Й-.2)блока коррекции соединен с первым ;л.информационным входом первого разряда+1)-й тетрады, первые информационные входы первых разрядов первой и второй тетрад соединены соответственно с выходами старших разрядов (и)-го блока коррекции и первой тетрады, вторые информационныевходы всех тетрад являются информационными входами преобразователя, атактовые входы всех тетрад соедйнены с вторым выходом распределителя ф импульсов, о т л и ч аю щ и й с ятем, что, с целью расширения клас, са решаемых задач за счет обеспечения преобразования как в двоично"десятичный код, так и в двоично-де сятичный шестидесятиричный код, внего введены 5 ф 1 блоков управления блоками коррекции и управляющий триггер, тактовый вход которого сое-. динен с третьим выходом распределителя импульсов, управляющий вход является управляющим входом преобразо: вателя, а выходы управляющего тригге. ра соединены соответственно с первым и вторым управляющими входами блоков управления блоками коррекции, первый и второй выходы которых соединены соответственно с первым и вторым управляющими входами соответствующих нечетных блоков коррекции, вход запрета которых соединен с инверсным выходом управляющего триггера, пер вый и второй управляющие входы четных блоков коррекции соединены соответственно с инверсными выходами второго и четвертого разрядов соответствующих тетрад, вход настройки 20 четных блоков коррекции соединен с входом .логического нуля преобразователя, первый и второй информационные входы блоков управления блоками коррекциисоединены соответственно с 25 прямым и инверсным выходами четвертого разряда соответствующих четных тетрад, инверсный выход второго разряда которых соединен с третьими информационными входами соответству .ющих блоков управления блоками коррекции.2. Преобразователь по и. 1, о т л и ч а ю щ и й с я тем, что в нем блоки коррекции содержат четыр- З 5 надцать элементов И, четыре элемента ИЛИ-НЕ и элемент НЕ, причем выходы элементов ИЛИ-НЕ являются выходами блока коррекции, выходы первого, второго и третьего элемента И соединены е входами первого элемента ИЛИ-НЕ выходы четвертого, пятого, шестого и седьмого элементов И соединены с входами второго элемента ИЛИ-НЕ, выходы восьмого, девятого, десятого и одиннадцатого элементов45 И соединены с входами третьего элемента ИЛИ-НЕ, выходы двенадцатого, тринадцатого и четырнадцатого элементов И соединены с входами четвертого элемента ИЛИ-НЕ, вход запрета 50 блока коррекции соединен с первыми входами третьего, седьмого, одиннадцатого и четырнадцатого элементов И, а через элемент НЕ с первыми входами остальных элементов И, вторые входы 55 первого, двенадцатого и четырнадца.того элементов И соединены с прямым информационным входом четвертого разряда блока коррекции, вторые входы второго шестого и седьмого элемен тов И соединены с прямым информационным входом второго разряда блока коррекции, вторые входы третьего,четвертого, пятого, девятого и три-надцатого элементов И соединены стретьими входами первого и второгоэлементов И и прямым информационнымвходом первого разряда блока коррекции, вторые входы восьмого, десятого и одиннадцатого элементов И соединены с третьим входом пятого, четвертым входом первого элемента И ипрямым информационным входом третье-го разряда блока коррекции, третийвход четвертого элемента И соединенпервым управляющим входом блокаоррекции, третьи входы восьмого и .тринадцатого элемейтов И соединеныс четвертым входом пятого элементаИ и с инверсным информационным входом четвертого разряда блока коррекции, третьи входы шестого, десятогои двенадцатого элементов И соединеныс инверсным информационным входомпервого разряда блока коррекции, третий вход девятого элеменТа И соединен с вторым управляющим входомблока коррекции, четвертые входычетвертого и девятого элементов Исоединены с инверсным информационнымвходом третьего разряда блока коррекции, четвертый вход восьмого элемента И соединен с инверсным информационным входом второго разряда блока коррекции.3. Преобразователь по пп, 1 и 2,о т л и ч а ю щ и й с я тем, чтов нем блок управления блоком коррекции содержит четыре элемента Ии дваэлемента ИЛИ-НЕ, выходы которых являются соответственно первым и вторым выходами блока управления блоком коррекции, первый информационный вход котброго соединен с первыми входами первого и второго элем.ментов И, первые входы третьего ичетвертого элементов И соединены соответственно с вторым и третьиминформационными входами блока управления блоком коррекции, первыйи второй управляющие входы которогосоединены с вторыми входами первого,четвертого и второго, третьего элементов И соответственно выходы первого и третьего элементов И соедине-.ны с входами первого элемента ИЛИНЕ, а выходы второго и четвертогоэлементов И соединены с входами второго элемента ИЛИ-НЕ.Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССРМ 723567, кл. 6 06 % 5/02, 1978.2. Авторское свидетельство СССРР 746496, кл. 6 06 Г 5/02, 19751003068 ель М Состав Техред ршавс Редактор Дан Корректор О. Би.Те 554/32 о 1303 г. Ужгород ул,Проектн Пат илиал П Тираж 704 НодписПИ Государственного комитета СССРо делам изобретений и открытийМосква, Ж, Раушская наб., д.4/5

СмотретьЗаявка

3276773, 20.04.1981

ПРЕДПРИЯТИЕ ПЯ А-3327

РАСПУТНЫЙ ВИЛЕН ПЕТРОВИЧ, САЛЬНИКОВА ЛАРИСА ИВАНОВНА

МПК / Метки

МПК: G06F 5/02

Метки: двоично-десятичных, двоичные, чисел

Опубликовано: 07.03.1983

Код ссылки

<a href="https://patents.su/9-1003068-preobrazovatel-dvoichno-desyatichnykh-chisel-v-dvoichnye.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь двоично-десятичных чисел в двоичные</a>

Предыдущий патент: Однотактный регулятор постоянного напряжения

Следующий патент: Цифровой дискриминатор

Случайный патент: Способ определения мощности смятой осадочной толщи