Сумматор в коде м из n

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 955037

Автор: Гуменюк

Текст

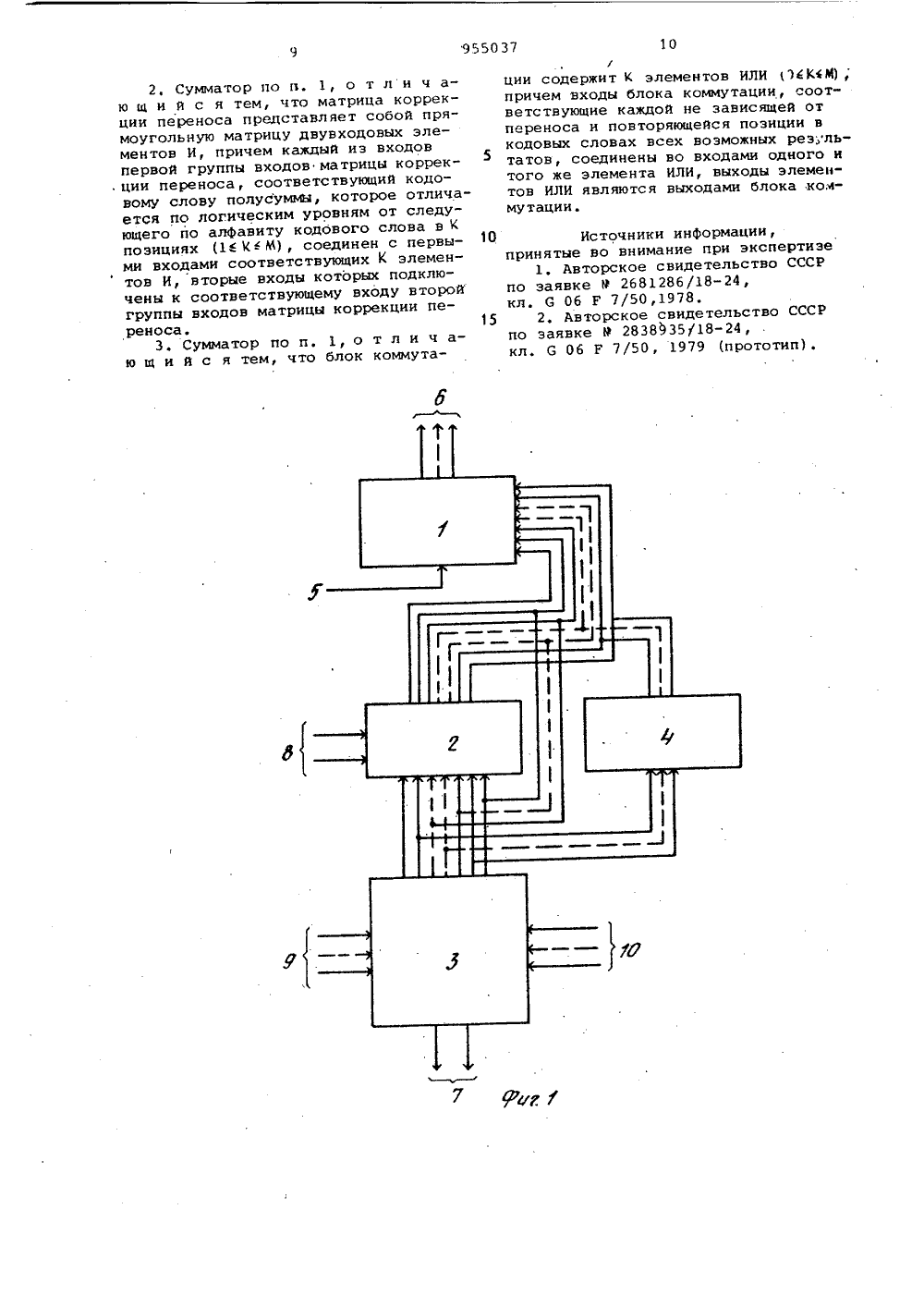

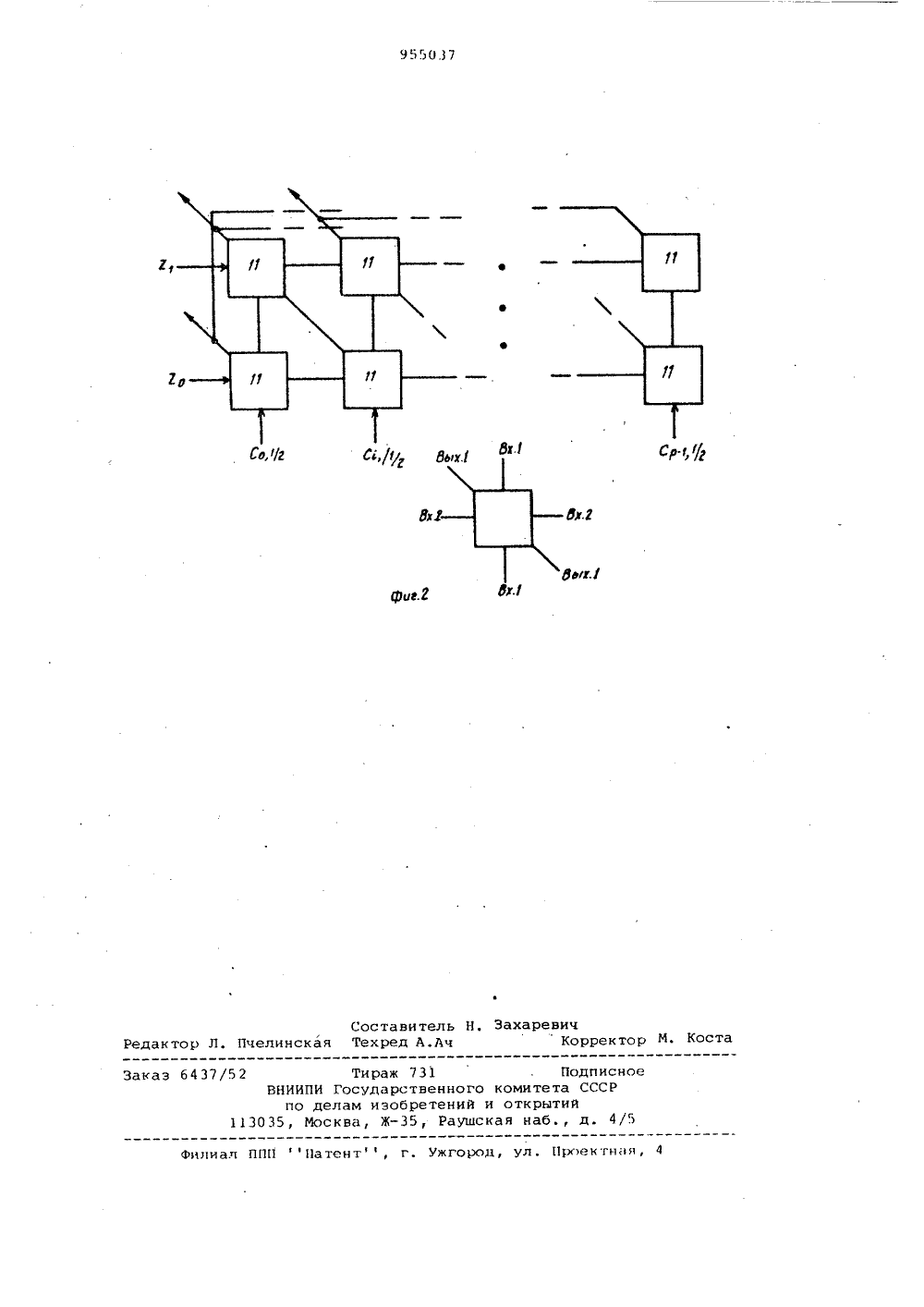

ОПИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоветскихСоциалистическихРеспублик и 955037(22) Заявлено 18.12.80 (21) 3219224/18-24с присоединением заявки Нов(23) ПриоритетОпубликовано 300882. Бюллетень )4 о 32 51 М, Кп,6 06 Р 7/49 Государственный комитет СССР ио делам изобретений и открытийДата опубликования описания 30.08.82(72) Авторизобретения В.А. Гуменюк рдена Трудового Красного Знамени инститнженеров гражданской авиацйи 71) Заявитель евский(54) СУММАТОР В КОДЕ М И 20 Изобретение относится к вычислительной технике и предназначено для суммирования чисел, представленных в коде М из И (где Б - количество позиций в кодовом слове; М - количество единиц в кодовом слове).Известен двуразрядный сумматор в коде М из Б, младший разряд которого содержит схему выдачи результата, шифратор, матрицу элементов И, схему переноса и схему контроля, старший разряд содержит две схемы выдачи результата, два шифратора, матрицу элементов И, схему переноса и схему контроля, причем выходы матрицы младшего разряда соединены со входами схемы переноса и шифратора младшего разряда, выходы матрицы старшего разряда соединены со входами схемы переноса и обоих шифраторов старшего разряда, выходы шифратора.и схемы . контроля младшего разряда соединены со входами схемы выдачи младшего разряда, выходы схемы переноса младшего разряда и обоих шифраторов старшего разряда соединены со входами соответствующих схем выдачи старшего разряда, выходы схемы контроля стар,шего разряда соединены со входами схем выдачи старшего разряда выходы схем выдачи младшего и старшего разрядов и схемы переноса старшего разряда соединены с соответствующими шинами устройства (1.Недостатки данного устройства сравнительно невысокое быстродействие из-за необходимости прохождения сигналов, соответствующих результату выполненной операции, через схемы выдачи результата и большие аппаратурные затраты на реализацию схем контроля и схем выдачи результата,Наиболее близок к предлагаемому по технической сущности сумматор в коде М из И, который содержит. регистр результата, шифратор, матрицу сложения и блок переноса, причем входы матрицы сложения соединены соответственно со входными шинами первого и второго сумматора, выходы матрицы сложения соединены соответственно со входами шифратора и блока переноса, выходы регистра результата соединены с выходными шинами сумматора, первая группа входов регистра результата соединена со входной шиной установки сумматора, выходы шифратора соединены со второй группой входов регистра результата. Операнды в коде М из Б поступают на входы матрицыпереноса, неповторяющиеся позиции в кодовых словах результатов, непосредетвенно соединены с соответствующи ми входами второй группы входов регистра 1 результата, другая часть этих выходов, которым соответствуют независящие от переноса, повторяющи еся позиции в кодовых словах,результатов, соединены со входами блока 4 коммутации, выходы последнего соединены с соответствующими входами второй группы входов регистра 1 резуль тата. сложения, с выходов этой схемы сигналы поступают на один из входов схемы переноса и один из входов шифратора. С одного из выхоцов блока переноса сигнал, соответствующий 0 или 1, поступает на выходную шину устройстваС выхода шифратора сигналы, противоположные (по уровням напря-. жений) результату операции в коде М из И, поступают на нулевые входы триггеров, предварительно установленные в единичное состояние. На выходах регистра результата образуется кодовое слово, соответствующее результату операции в коде М иэ )Ч 2).Недостатком известного устройства 15 является сравнительно невысокое быстродействие, в случае использования его в многоразрядном сумматоре, где приходится учитывать переносы иэ младших разрядов сумматора. Сигнал переноса может быть получен только после прохождения входных сигналов (представляющих операнды) последовательно через два элемента, входящих в состав матрицы сложения и блока переноса. Следовательно, результат опе-рации в коде, противоположном (по уровням напряжений) коду М иэ И с учетом переноса может быть получен только с помощью некоторого третьего блока, включенного последовательно с первыми двумя. Цель изобретения - повышение быстродействия сумматора в коде М иэ И при операции с учетом переноса. 35Поставленная цель достигается тем, что сумматор в коде М из Ы, включающий регистр результата и матрицу сложения, причем входы матрицы сложения соединены соответственно со 4 О входными шинами первого и второго операндов сумматора, выходы регистра результата соединены с выходными шинами сумматора, первая группа входов регистра результата соединена со вход 45 ной шиной установки сумматора, содержит матрицу коррекции переноса и блок коммутации, причем первая группа выходов сложения соединена с выходными шинами переноса сумматора, вторая группа выходов матрицы сложения соединена с первой группой входов матрицы коррекции переноса, те из выходов, которым соответствуют не зависящие отпереноса неповторяющиеся позиции в кодовых слсвах всех возможных результатов, соединены непосредственно с соответствующими входами второй .группы входов регистра результата, другие выходы второй группы выходов матрицы сложения, которым соответствуют не зависящие от переноса. повторяющиеся позиции в кодсвых словах всех возможных результатов, соеди иены со входами блока коммутации, выходы блока коммутации соединены с соответствующими входами второй группы входов регистра результата, вторая группа входов матрицы коррекции переноса соединена со входными шинами переноса сумматора,Матрица коррекции переноса представляет собой прямоугольную матрицу двувходовых элементов И,причем каждый из входов первой группы входов матрицы коррекции переноса,соответствующий кодовому слову полусуммы,которое отличается по логическим уровням от следующего по алфавиту кодовогослова в К позициях (1 й К с М),соединенс первыми входами соответствующих К элементов И,вторые входы которых подключены к соответствующему входу второй группы входов матрицы коррекциипереноса.,Блок коммутации содержит К элементов ИЛИ, где 0 6 КМ, причем входы блока коммутации, соответствующие каждой не зависящей от переноса и повторяющейся позйции в кодовых словах всех возможных результатов, соединены со входами одного и того же элемента ИЛИ, выходы элементов ИЛИ являются выходами блока коммутации.На фиг. 1 представлена блок-схема предлагаемого сумматора в коде М из М; на фиг. 2 - блок-схема матрицы коррекции переноса.Сумматор содержит регистр 1 результата, матрицу 2 коррекции переноса, матрицу 3 сложения и блок 4 коммутации,Первая группа входов регистра 1 результата соединена со входной шиной 5 установки сумматора, выходы матрицы коррекции переноса соединены со второй группой входов регистра 1 результата, выходы последнего и первая группа выходов матрицы 3 сложения соединены с выходными шинами суммы би переноса 7 устройства, вторая группа входов матрицы 2 коррекции переноса и первые две группы входов матрицы 3 сложения соединены со входнымишинами 8 и 9, 10 устройства соответственно, вторая группа выходов матрицы 3 сложения соединена с первойгруппой входов матрицы 2 коррекциипереноса, одна часть этих выходов,которым соответствуют независимые отРе гис тр 1 ре зул ь та та п редс тавля е тсобой группу из И триггеров, единичные вхОды которых образуют первуюгруппу входов, а нулевые - вторуюгруппу в):одов регистра 1. Единичныевыходы триггеров образуют группу выходов регистра 1. Матрица 2 коррекции переноса представляет собой прямоугольную матрицу элементов И 11.На схеме фиг. 2 2 и 2 - сигналы,соответствующие переносу из младшего разряда нуля и единицы соответственно, Свц, С( и Ср.1/, - сигналысоответствующие полусуммам, равным0,1(16 р)и рсоответственно (гдер - основание системы счисления).Матрица 2 коррекции переноса содержиттолько те элементы, которые соответствуют .(И-1)-ым позициям кодовогослова результата (где 1 - номера позиций этого слова, зависящих от переноса из младшего разряда (О1Б),Если принят алфавит, в котором кодовые слова, соответствующие любымдвум соседним (в алфавите) цифрам,отличаются друг от друга только одной позицией (по уровням напряженийв ней), то матрица имеет минимальныеразмеры (2 хр), каждый вход матрицы 2коррекции переноса соединен толькос одной координатной шиной ее. Еслипринят алфавит, в котором различиямежду кодовыми словами, соответствующими соседним цифрам максимальны,то матрица коррекции переноса имееттакже максимальные размеры (3 х р),каждый вход первой группы входовматрицы коррекции перейоса соединенс соответствующими 3-ми (1 ( 3 ( М) координатными шинами каждый вход второй группы - с однойшиной. Выходыэлементов И матрицы коррекции переноса, соответствующие одинаковым позициям кодового слова результата,соединены входными диагональными шинами с соответствующими выходами матрицы 2 коррекции переноса. Матрица 3сложения представляет собой матрицумноговходовых элементов И.Количествовходов каждого элемента И равно 2 М .Входы элементов И соединены с определенными шинами кодов операндов согласно выбранному алфавиту. Шины кодов операндов соединены со входамиматрицы сложения, Каждый элемент Иимеет по два гальванически независимых выхода. Первые выходы элементов,соответствующих одинаковым переносамв следующий разряд, соединены шинами с первой группой выходов матрицысложения, Вторые выходы, соответствующие одинаковым результатам сложения в данном разряде, соединены шинами со второй группой выходов матрицы 3 сложения,Блок 4 коммутации представляет.собой группу из элементов ИЛИ, где 0Ь с М, в зависимости от выбранногоалфавчТа, Входы блока коммутации,соответствующие каждой независящейоч переноса и повтор 4 ощейся позициив кодовых словах (представленных вкоде, пртивоположном коду М из И поуровням напряжений) всех возможныхрезультатов, соединены со входами од-,ного и того же элемента ИЛИ, Выходыэлементов ИЛИ являются выходами блока. Существует зависимость между числом элементов ИЛИ блока 4 коммутациии числом элементов И 11 блока 2Если блок 2 содержитминимальное числоэлементов И 11(2 х р)то число эле ментов блока 4 коммутации максимальноЬ = М. Если блок 2 содержит максимальное число элементов И (3 х р),то Ь = О, т.е. необходимость в блоке4 коммутации отпадает.20 Устройство работает следующим образом.Операнды в коде М из И поступаютна входы матрицы 3 сложения, Еслипоступают правильные кодовые слова,то срабатывает один из многовходовыхэлементов И и с его выходов сигналы,соответствующие результату операцйи,поступают на один из входов матрицы 2коррекции переноса (на первую группувходов), на одну из выходных шин 7переноса, на соответствующие входывторой группы входов регистра 1 результата (в том случае, если в кодовом слове результата есть позиции, 35 уровень напряжений в которых не зависит от величины переноса из младшегоразряда), и на соответствующие входы блока 4 коммутации (в том случае,если упомянутые выше позиции повторя ются в различны.; кодовых словах результатов). Одновременно с этим, наодин из входов второй группы входовматрицы коррекции переноса 2 поступает по входной шине 8 переноса сиг нал. Затем срабатывает один или несколько элементов И 11 матрицы 2 коррекции переноса и соответствующиеэлементы ИЛИ блока 4 коммутации,Сигналы с выходов этих элементов поступают на соответствующие входы второй группы входов регистра 1 результата, образуя вместе с поступившимиранее с выходов второй группы выхоцов матрицы 3 сложения кодовое словорезультата в коде, противоположном(по уровням напряжений) коду М из И.Эти сигналы воздействуют на соответствующие триггеры регистра 1 результата (на нулевые входы), предваритель"н о установленные в единичное состоя 1ние. После этого, на выходах блокаобразуется кодовое слово, соответствующее результату операции в коде Миз Б.Появление ошибочных кодовых слоев 65 операндов с меньшим, чем положено, 955037Формула изобретения количеством единиц приводит к отсутствию сигналов на всех выходах матрины 3 сложен)я. Появление ошибочных кодовых слов операндов с большим, чем положено, количеством единиц приводит к появлению на выходах матрицы 3 сложения сразу нескольких сигналов, которые затем шифруются матрицей 2 коррекции переноса, блоком 4 коммутации и непосредственными связями матрицы 3 сложения с регистром 10 1 результата как результаты нескольких правильных операций, появившихся одновременно в коде, противоположном (по уровням напряжений) коду М из И. Вследствие этого, на выходах регистра 15 1 результата образуется кодовое слово с меньшим, чем положено, количест-, вом единиц, так как большее, чем нужно, количество триггеров (установленных ранее в единичное состояние) 20 будут переведены в нулевое состояние, Такое слово не может быть дешифроваНо как правильное и, следовательно, ошибка не получит дальнейшего распространения. 25П р и м е р, Примем следующий алфавит для кода 2 из 4 при р = б.0 - 0011 у 3 - 0110 р1 - 0101 у 4 - 1010 у2 - 1001 у 5 - 1100, 30 где нулевая позиция - крайняя справа.Матрица коррекции в этом случае содержит шестнадцать элементов И 11Непосредственно соединены со входами регистра 1 результата следующие выходы матрицы 3 сложения;35С- со входомсоответствующим3-ей позиции;С- со входом, соответствующим1-ой позиции,.4 О Выходы матрицы 3 сложения Си С 4 т соединены со входами элемента ИЛИ, в единственном числе представляющем в данном случае блок 4 коммутации. Выход этого элемента соединен со входом регистра 1 результата, соответствующим 0-ой позиции (здесь и ранее речь идет о второй группе входов блока 1). Сложим, например, числа 1 и 3, с учетом переноса единицы из младшего разряда. На одном из выходов первой группы вЫходов матрицы 3 сложения появится сигнал Перенос нуля. Одновременно появляется сигнал на выходе С 4 4 второй группы выходов матрицы 3 сложения и поступает вместе с сигналом 1 Перенос единицы (Е) на вход элемента матрицы коррекции переноса 2 (фиг. 4) .Кроме того, сигнал С 4поступает на вход элемента ИЛИ блока 4 коммутации. С выходов указанных элементов сигналы поступают на входы, соответствующие 1-ой (сигнал с выхода матрицы 2 коррекции переноса) и 0-ой (сигнал с выхода блока коммутации 4) позициям 65 кодового слова результата сложения в коде, противоположном (по уровням напряжений) коду М из М, второй группы входов регистра 1 результата, Поскольку все триггеры регистра 1 результата должны быть к тому моменту установлены в единичное состояние (сигналом, поступившим на первую группу входов), то сигналы, соответствующие 0-ой и 1-ой позициям кодового слова, поступая на нулевые входы триггеров переводят их в нулевое состояние. На выходах регистра результата 1 образуется кодовое слово результата в данном разряде 1100, соответствующее цифре 5.Положительный эффект от внедрения устройства заключается в повышении быстродействия не менее чем на 25 при построении многоразрядного сумматора, так как в отличие от прототипа значение переноса из младшего разряда (или группы младших разрядов) учитывается в следующем после матрицы сложения блоке - матрице коррекции переноса при образовании 1 кодового слова результата операции. 1, Сумматор в коде М из Н, содержащий регистр результата и матрицу сложения, причем входы матрицы сложения соединены соответственно с вход ными шинами первого и второго операн дов сумматора, выходы регистра результата соединены с выходными шинами сумматора, первая группа входов регистра результата соединена со входной шиной установки сумматора, о т л и.ч а ю щ и й с я тем, что, с целью повышения быстродействия, сумматор содержит матрицу коррекции переноса и блок коммутации, причем первая группа выходов матрицы сложения соединена с выходными шинами сумматора, вторая группа выходов матрицы сложения соединена с первой группой входов матрицы коррекции переноса, те из этих выходов, которым соответствуют не зависимые от переноса неповторяющиеся позиции в кодовых словах всех возможных результатов, соединены непосредственно с соответствующими входами второй группы входов регистра результата, другие выходы второй группы выходов матрицы сложения, которым соответствуют не зависимые от переноса повторяющиеся позиции в кодовых словах всех возможных результатов, соединены со входами блока коммутации, выходы блока коммутации соединены с соответствующими входами второй группы входов регистра результата, вторая группа входов матрицы коррекциИ переноса соединена со входными шинами переноса сумматора.2. Сумматор по и. 1, о т л н ч аю щ и й с я тем, что матрица коррекции переноса представляет собой прямоугольную матрицу двувходовых элементов И, причем каждый из входов первой группы входов матрицы коррекции переноса, соответствующий кодовому слову полусумма, которое отличается по логическим уровням от следующего по алфавиту кодового слова в К позициях 1 ) М), соединен с первы ми входами соответствующих К элементов И, вторые входы которых подключены к соответствующему входу второй группы входов матрицы коррекции переноса. 153. Сумматор по п. 1, о т л и ч аю щ и й с я тем, что блок коммутаУции содержит К элементов ИЛИ 1)4 ОМ), причем эходы блока коммутации, соот" ветствующие каждой не зависящей от переноса и повторяющейся позиции в кодовых словах всех возможных рез,льтатов, соединены во входами одного и того же элемента ИЛИ, выходы элементов ИЛИ являются выходами блока .коммутации. Источники инФормации,принятые во внимание при экспертизе1, Авторское свидетельство СССРпо заявке Р 2681286 /18-24,кл. С 06 Р 7/50,19782, Авторское свидетельство СССРпо заявке Р 283813518-24,кл. 6 06 Р 7/50, 1979 (прототип),955037 Ср.т,Со,й Составитель Н. ЗахаревичРедактор Л. Пчелинская Техред А.Ач Корректор М. Кост з 6437/52В е о к ПППатент , г. Ужгород, ул. Проектная Филиал Тираж 731ПИ Государственноделам иэобретениМосква, Ж, Рауш Подпимитета СССкрытийнаб., д.

СмотретьЗаявка

3219224, 18.12.1980

КИЕВСКИЙ ОРДЕНА ТРУДОВОГО КРАСНОГО ЗНАМЕНИ ИНСТИТУТ ИНЖЕНЕРОВ ГРАЖДАНСКОЙ АВИАЦИИ

ГУМЕНЮК ВИТАЛИЙ АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: G06F 7/49

Опубликовано: 30.08.1982

Код ссылки

<a href="https://patents.su/6-955037-summator-v-kode-m-iz-n.html" target="_blank" rel="follow" title="База патентов СССР">Сумматор в коде м из n</a>

Предыдущий патент: Устройство для суммирования

Следующий патент: Устройство для выполнения операций умножения и деления

Случайный патент: Устройство для определения суточного прироста массы животных в групповых станках