Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

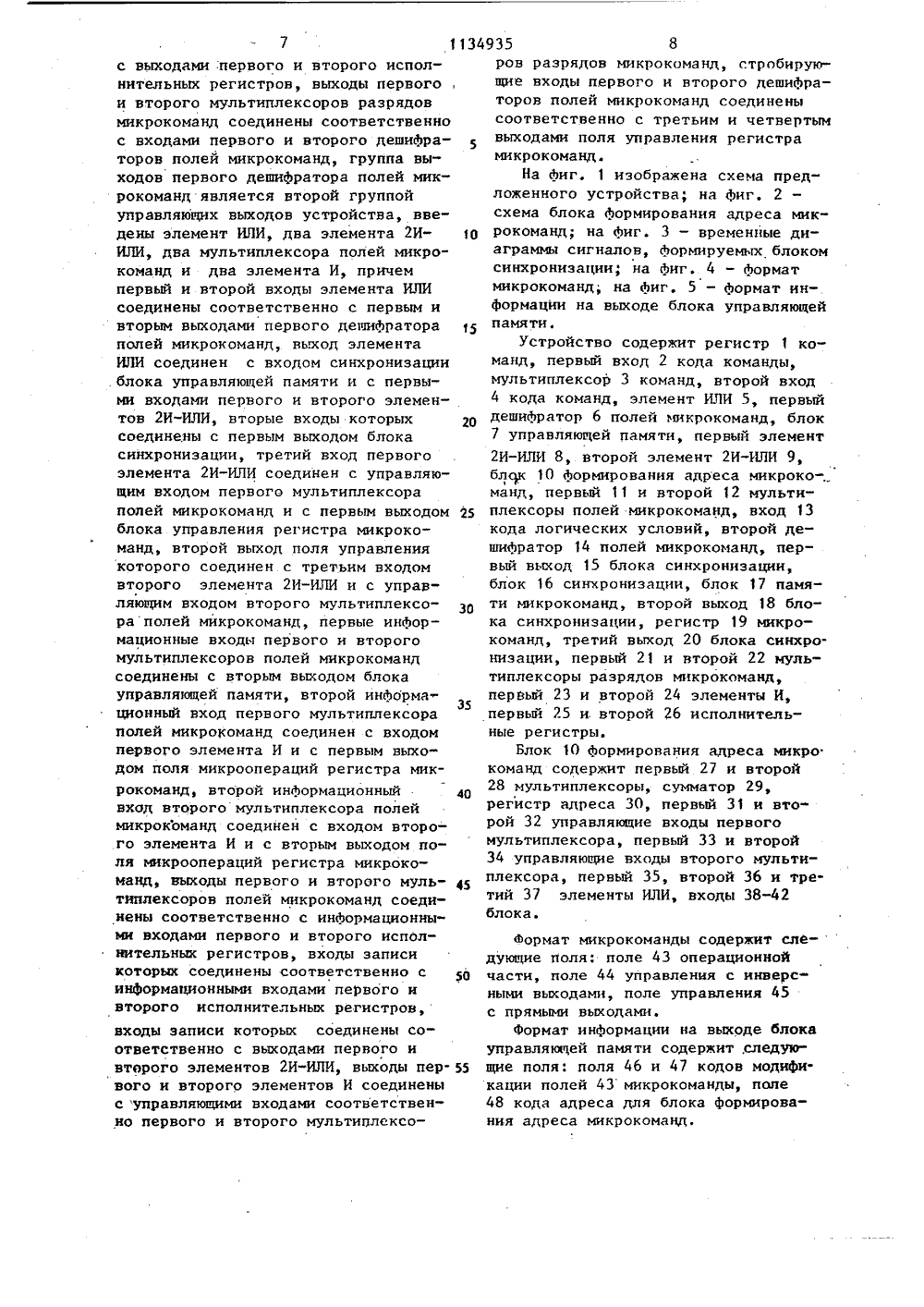

(21) 3591224/18 (22) 13.05.83 (46) 15.01.85. (72) В,А.Иванов и В.В.Сыров (71) Ордена Лен тики им. В.М.Гл (53) 681,325(08. (56) 1. Хассон управление, т, 1974. Бюл Н 2 С,И.Ками скии иберне нашко стит кропрограммнн ввММир авле 3. п) ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ 2. Кравцов Л.Я. Проектировмикропрограммных устройств упния. Л., "Энергия", 1976.3. Авторское свидетельствоВ 387366, кл. (: Об Р 9/22, 194. Патент фРГ М 2204650,кл. С ОЬ Р 9/22, 1977.5. Патент СНА Р 3953833,кл. ( 06 Р 9/22, 1980 (протот(54) (57) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее регистркоманд, мультиплексор команд, блокуправляющей памяти, два исполнительных регистра, блок памяти микрокоманд, регистр микрокоманд, два мультиплексора разрядов микрокоманд,два дешифратора полей микрокоманд,блок синхронизации и блок формирования адреса микрокоманд, содержащий два мультиплексора, сумматор,регистр адреса и три элемента ИПИ,.причем инФормационный вход регистракоманд является первым входом кодакоманды устройства, выход регистракоманд соединен с первым инФормационным входом мультиплексора команд,второй информационный вход которогоявляется вторым входом кода командыустройства, первый и второй управляющие входы мультиплексора команд подключены соответственно к первому и второму входам первого дешифратора полей микрокоманд, выход мультиплексора команд соединен с адресным входом блока управляющей памяти, пер вый выход которого соединен с первым инФормационным входом первого мультиплексора, второй информационный вход которого соединен с первым информационным входом второго мультиплексора, с адресным входом блока памяти микрокоманд и с выходом регистра адреса, инФормационный вход которого соединен с выходом сумматора, первый и второй информационные Е входы которого соединены соответственно с выходами первого и второго ,мультиплексоров, второй инФормацион" ный вход последнего является входом кода логических условий устройства, первый и второй управляющие входы первого мультиплексора соединены соответственно с выходами первого и второго элементов ИЛИ блока формирования адреса микрокоманд, первый и второй управляющие входы второго мультиплексора соединены соответственно с выходом третьего элемента ИПИ блока формирования адреса микро- команд и с первыми входами второго и третьего элементов ИЛИ блока форми. рования адреса микрокоманд и второ-го дешиФратора полей микрокоманд, второй виход которого соединен с первым входом первого элемента ИЛИ блока Формирования адреса микрокоманд, второй вход которого соединен с вторым входом третьего элемента ИЛИ блока формирования адреса микро" команд и с третьим выходом второго1134935 дешифратора полей микрокоманд, четвертый выход которого соединен свторым входом второго элемента ИЛИблока формирования адреса микрокоманд, третий вход которого соединенс третьим входом первого элементаИЛИ блока формирования адреса микрокоманд и с пятым выходом второго дешифратора полей микрокоманд, остальные выходы которого являются управляющими выходами первой группы устройства, вход синхронизации регистраадреса соединен с первым выходомблока синхронизации, второй и третийвыходы которого соединены соответственно с входами синхронизации блокапамяти микрокоманд и регистра микрокоманд, группа информационных входов которого соединена с группойвыходов блока памяти микрокоманд,первый и второй выходы поля микроопераций регистра микрокомаид соединенысоответственно с первыми информационными входами первого и второгомультиплексоров разрядов микрокоманд, вторые информационные входыкоторых соединены соответственно свыходами первого и второго исполнительных регистров, выходы первого ивторого мультиплексоров разрядов микрокоманд соединены соответственно свходами первого и второго дешифраторов полей микрокоманд, группа выходов первого дешифратора полей микрокоманд является второй группой управ"ляющих выходов устройств, о .т л и -ч а ю щ е е с я тем, что, с цельюповышения быстродействия, оно дополнительно содержит элемент ИЛИ, дваэлемента 2 И-ИЛИ, два мультиплексораполей микрокоманд и два элемента И,причем первый и второй входы элемента ИЛИ соединены соответственно спервым и вторым выходами первогодешифратора полей микрокоманд, выходэлемента ИЛИ соединен с входом синхронизации блока управляющей памяти Изобретение относится.к вычислительной технике и предназначено для построения микропрограммных устройств управления ЭВИ. и с первыми входами первого и второго элементов 2 И-ИЛИ, вторые входыкоторых соединены с первым выходомблока синхронизации, третий входпервого элемента 2 И-ИЛИ соединен суправляющим входом первого мультиплексора полей микрокоманд и с первым выходом поля управления регистрамикрокоманд, второй выход поля управления которого соединен с третьимвходом второго элемента 2 И-ИЛИ и суправляющим входом второго мультиплексора полей микрокоманд, первыеинформационные входы первого и второго мультиплексоров полей микрокоманд соединены с вторым выходом блока управляющей памяти, второй информационный вход первого мультиплексора полей микрокоманд соединен свходом первого элемента И и с первым выходом поля микроопераций регистра микрокоманд, второй информационный вход второго мультиплексораполей микрокоманд соединен с входомвторого элемента И и с вторым выходом поля микроопераций регистрамикрокоманд, выходы первого и второго мультиплексоров полей микрокоманд соединены соответственно с информационными входами первого и второго исполнительных регистров, входы записи которых соединены соответственно с информационными входами первого и второго исполнительных регистров, входы записи которых соединены соответственно с выходами первого и второго элементов 2 И-ИЛИ, выходы первого и второго элементов И соединены с управляющими входами соответственно первого и второго мультиплексоров разрядов микрокоманд, стробирующие входы первого и второго дешифраторов полей микрокоманд соединены соответственно с третьим и четвертым выходами поля управления регистра микрокоманд. Известнымикропрограммные устройства управления, содержащие регист команд, память микрокомаид, регистр микроко" манд,блок дешифрации и управления Ии 2.40 3 11349Недостатком указанных устройствявляется необходимость наличия вблоке памяти микрокоманд ветвей микрокоманд, различающихся некоторымиполями в цепочках однотипных микропрограмм. Этот недостаток устраняется в устройствах, .в которых полямикрокоманд могут изменяться.Известно устройство микропрограммного управления, содержащее кромеперечисленных блоков регистр модификации и регистр режима работы, вкотором модификация регистра микрокоманд осуществляется содержимымпредварительно установленнбго регистра модиФикации под управлением регистра режима и дешифратора модификации 3,Недостатки этого устройства - избыточность регистра микрокоманд, низкое быстродействие и отсутствие возможности произвольной модификациимикрокоманды,Известно также микропрограммное,усройсво уравлен, .содержащее 25два блока памяти микрокоманд, первыйиэ которых хранит основную микропрограмму и,маску управления, а второй - специфичную управляющую информацию, причем микрокоманды основной30микропрограммы модифицируются специфичной управляющей информацией1под управлением маски.К недостаткам этого устройстваотносятся большой объем памяти микрокоманд и отсутствие возможностипроизвольной модификации микрокоманды. Наиболее близким по технической сущности к предлагаемому является микропрограммное устройство управления, содердащее регистр команд, мультиплексор команд, блок управляющей памяти, два исполнительных реги-. стра, блок памяти микрокоманд, регистр микрокоманд, два мультиплексо ра разрядов микрокоманд, два дешифратора полей микрокоманд, блок синхронизации и блок формирования адреса микрокоманд, содержащий два муль" тицлексора, сумматор, регистр адре са и три элемента ИЛИ, причем инфор- мационный вход регистра команд является первым входом кода команды устройства, выход регистра команд соединен с первым информационным 55 входом мультиплексора команд, второй информационный вход которого является вторым входом кода команды уст-35 4ройства, первый и второй управляющие входы мультиплексора команд подключены соответственно к первому ивторому выходам первого дешифратораполей микрокоманд, выход мультиплексора команд соединен с апреснымвходом блока управляющей памяти, первый выход которого соединен с первыминформационным входом первого мультиплексора, второй информационныйвход которого соединен с первым информационным входом второго мультиплексора, с адресным входом блокапамяти микрокоманд и с выходом регистра адреса, информационный входкоторого соединен с выходом сумматора, первый и второй информационныевходы которого соединены соответственно с выходами первого и второгомультиплексора, второй информационный вход которого является входомкода логических условий устройства,первый и второй управляющие входыпервого мультиплексора соединенысоответственно с выходами первого.и второго элементов ИЛИ блока формирования адреса микрокоманд, первыйи второй управляющие входы второгомультиплексора соединены соответственно с выходом третьего элементаИЛИ блока формирования адреса микрокоманд и с первыми входами второгои третьего элементов ИЛИ блока формирования адреса микрокоманд и второгодешифратора полей микрокоманд,второй выход .которого соединен спервым входом первого элемента ИЛИблока формирования адреса микрокоманд, второй вход которого соединенс вторым входом третьего элементаИЛИ блока формирования адреса микрокоманд и с третьим выходом второгодешифратора полей микрокоманд, четвертый выход которого соединен свторым входом второго элемента ИЛИблока формирования адреса микрокоманд, третий вход которого соединенс третьим входом первого элементаИЛИ, блока формирования адреса микрокоманд и с пятым выходом второгодешифратора полей мнкрокоманд, остальные выходы которого являются управляющими выходами первой группыустройства, вход синхронизациирегистра адреса соединен с первым выходом блока синхронизации, второй итретий выходы которого соединены соответственно с входами синхрониза 1134935ции блока памяти микрокоманд и регистра микрокоманд, группа инАормационньи входов которого соединенас группой вьиодов блока памяти микро.команд, первый и второй выходы поля 5микроопераций регистра микрокомандсоединены соответственно с первымиинформационными входами первого ивторого мультиплексоров разрядов микрокоманд, вторые информационные входы которых соединены соответственнос выходами первого и второго испол"нительных регистров, выходы первогои второго мультиплексоров разрядовмикрокоманд соединены соответствен 15но с входами первого и второго дешиАраторов полей микрокоманд, группавыходов первого дешиАратора полеймикрокоманд является второй группойуправляющих выходов устройства 5 .Недостаток указанного устройства - малое быстродействие, обусловленное избыточностью циклов обращения к памяти.микрокоманд в процессеФункционирования.Целью изобретения является повышение быстродействия,указанная цель достигается тем,что в микропрограммное устройствоуправления, содержащее регистр ко 30манд, мультиплексор команд, блокуправляющей памяти, два исполнительньи регистра, блок памяти микрокоманд, регистр микрокоманд, два мультиплексора разрядов микрокоманд, 35два дешиАратора полей микрокоманд,блок синхронизации и блок формирования адреса микрокоманд, содержащий два мультиплексора, сумматор,регистр адреса и три элемента ИЛИ 40причем инАормационный вход регистракоманд является первым входом кодакоманды устройства, выход регистракоманд соединен с первым инАормационным входом мультиплексора команд,второй инФормационный вход которогоявляется вторым входом кода командыустройства, первый и второй управляю.щие входы мультиплексора команд подключены соответственно к первому Ии второму входам первого дешифраторапопей микрокоманд, вьиод мультиплексора команд соединен с адресным входом блока управляющей памяти, первый выход которого соединен с первым 5-информационным входом первого мультиплексора, второй информационныйвход которого соединен с первым информационным входом второго мультиплексора, с адресным входом блока памяти микрокоманд и с выходом регистра адреса, информационный вход которого соединен с выходом сумматора, первый и второй инАормационные входы которого соединены соответственно с выходами первого и второго мультиплексоров, второй инАормацион" ный вход последнего является входом, кода логических условий устройства, первый и второй управляющие входы первого мультиплексора соединены соответственно с выходами первого и второго элементов ИЛИ блока Аормирования адреса микрокоманд, первый и второй управляющие входы второго мультиплексора соединены соответственно с выходом третьего элемента ИЛИ блока Формирования адреса микро- команд и с первыми входами второго и третьего элементов ИЛИ блока Аормирования адреса микрокоманд и второго дешнАратора полей микрокоманд, второй выход которого соединен с первым входом первого элемента ИЛИ блока Формирования адреса мнкрокоманд, второй вход которого соединен с вторым входом третьего элемента ИЛИ блока Аормировання аДреса микро- команд и с третьим выходом второго дешиАратора нолей микрокоманд, четвертый выход которого соединен с вторым входом второго элемента ИЛИ блока Аормирования адреса микрокоманд, третий вход которого соединен с третьим входом первого элемента ИЛИ блока Аормирования адреса микро- команд и с пятым выходом второго дешиАратора полей микрокоманд, остальные выходы которого являются управляющими выходами первой группы устройства, вход синхронизации регистра адреса соединен с первым вьиодом блока синхронизации, второй и третий выходы которого соединены соответственно с входами синхронизации блока памяти микрокоманд и регистра микрокоманд, группа информационных входов которого соединена с группой выходов блока памяти микро- команд, первый и второй выходы поля микроопераций регистра микрокоманд соединены соответственно с первыми инАормационными входами первого ивторого мультиплексоров разрядов мик рокомащ, вторые ияАормационные входы которых соединены соответственнос выходами:первого и второго исполнительных регистров, выходы первого и второго мультиплексоров разрядов микрокоманд соединены соответственно с входами первого и второго дешифраторов полей микрокоманд, группа выходов первого дешифратора полей микрокоманд является второй группой управляющих выходов устройства, введены элемент ИЛИ, два элемента 2 И- О ИЛИ, два мультиплексора полей микро- команд и два элемента И, причем первый и второй входы элемента ИЛИ соединены соответственно с первым и вторым выходами первого деиифратора полей мнкрокоманд, выход элемента ИЛИ соединен с входом синхронизации .блока управляющей памяти и с первыми входами первого и второго элементов 2 И-ИЛИ, вторые входы которых соединены с первым выходом блока синхронизации, третий вход первого элемента 2 И-ИЛИ соединен с управляющим входом первого мультиплексора полей микрокоманд и с первым выходом 25 блока управления регистра микрокоманд, второй выход поля управления которого соединен с третьим входом второго элемента 2 И-ИЛИ и с управляющим входом второго мультиплексораполей микрокоманд, первые информационные входы первого и второго мультиплексоров полей микрокоманд соединены с вторым выходом блока управляющей памяти, второй информа 35 ционный вход первого мультиплексора полей микрокоманд соединен с входом первого элемента И и с первым выходом поля микроопераций регистра микрокоманд, второй информационный 40 вход второго мультиплексора полей микрокоманд соединен с входом второго элемента И и с вторым выходом поля микроопераций регистра микрокомацц, выходы первого и второго муль тинлексоров полей микрокоманд соединены соответственно с информационными входами первого и второго исполютельных регистров, входы записи которых соединены соответственно с инФормационными входами первого и второго исполнительных регистров,входы записи которых соединены соответственно с выходами первого и второго элементов 2 И-ИЛИ, выходы пер ваго и второго элементов И соединены с управляющими входами соответственно первого и второго мультиплексоров разрядов микрокоманд, стробирующие входы первого и второго дешифраторов полей микрокоманд соединенысоответственно с третьим и четвертымвыходами поля управления регистрамикрокоманд,На Лиг, 1 изображена схема предложенного устройства; на фиг. 2 -схема блока формирования адреса микрокоманд; на фиг. 3 - временные диаграммы сигналов, формируемых блокомсинхронизации; на Лиг. 4 - форматмикрокоманд; на Лиг. 5 - формат информации на выходе блока управляющейпамяти.Устройство содержит регистр 1 команд, первый вход 2 кода команды,мультиплексор 3 команд, второй вход4 кода команд, элемент ИЛИ 5, первыйдешифратор 6 полей микрокоманд, блок7 управляющей памяти, первый элемент2 И-ИЛИ 8, второй элемент 2 И-ИЛИ 9,блак 10 формирования адреса микроко-,манд, первый 11 и второй 2 мультиплексоры полей микрокоманд, вход 13кода логических условий, второй дешифратор 14 полей микрокоианд, первый выход 15 блока синхронизации,блок 16 синхронизации, блок 1 памяти микрокоманд, второй выход 18 блока синхронизации, регистр 19 микрокоманд, третий выход 20 блока синхронизации, первый 2 и второй 22 мультиплексоры разрядов микрокоманд,первый 23 и второй 24 элементы И,первый 25 и. второй 26 исполнительные регистры.Блок 10 формирования адреса микрокоманд содержит первый 27 и второй28 мультиплексоры, сумматор 29,регистр адреса 30, первый 31 и второй 32 управляющие входы первогомультиплексора, первый 33 и второй34 управляющие входы второго мультиплексора, первый 35, второй 36 и третий 37 элементы ИЛИ, входы 38-42блока. Формат микрокоманды содержит слЕ- дующие поля: поле 43 операционной части, поле 44 управления с инверсными выходами, поле управления 45 с прямыми выходами.Формат информации на выходе блока управляющей памяти содержит, следующие поля: поля 46 и 47 кодов модификации полей 43 микрокоманды, папе 48 кода адреса для блока формирования адреса микрокоманд.Предлагаемое устройство работает следующим образом.Адрес микрокоманды, сформированный в блоке 10 Формирования адреса микрокоманд во время С 1 (Фиг. 3), 5 поступает на вход блока 17 памяти иикрокоманд, считывается из него во время С 2 и заносится на регистр 19 микрокоманд во время С 3. Каждое поле текущей микрокоманды осущест вляет управление соответствующим узлом ЭВМ в двух режимах - с модификацией поля микрокоманды содержимым .исполнительного регистра и без модификации, в соответствии с содержимым 5 поля регистра иикрокоманд. Режим работы, т,е. направление, с которого на дешифраторы 6 и 14 заносится код микрооперации, определяется самими полями микрокоманды при по мощи блоков 23 и 24, мультиплексорами разрядов микрокоманд. При заполнении полей 43 и 44 микрокоманды кодом специальной иикрооперации модификации, выделенной во множестве 25 кодов данного поля, элементы И 23 и 24 через мультиплексоры 21 и 22 разрядов иикрокоманд подключают к входам дешифраторов 6 и 14 выходы соответствующего исполнительного щ регистра 25, 26. При заполнении полей 43 иикрокоианды кодом любой другой мйкроонерации элементы 23 и 24 подключают через мультиплексоры 21 и 22 разрядов иикрокоманд к входам дешифраторов 6 и 14 содержимое полей 43 регистра 19 иикрокоманд. Единичные значения выходов полей 45 разрешают работу дешифраторов 6 и 14, При данной технической реа лйзации код модификации 1111 предпочтителен. В свою очередь, код модификации, хранящийся иа, исполнительных регистрах 25 и 26, может фориироваться из содержимого соответствующего поля управляющей памяти 7 или из соответствующего поля регистра 19 микрокоманд. Управление занесениеи на исполнительные регистры 25 и 26 осуществляется элементами 2 И-ИЛИ: единичные значения сиг.нала на выходе схемы ИЛИ 5 или инверсного сигнала с выходов полей 44разрешают прохождение. фазы С 1 на управляющий вход исполнительных регистров 25 и 26.Первый режим реализуется следующей последовательностью действий. Управляющий разряд модифицируемогополя текущей микрокоманды долженбыть равен единицеВ поле 43 иикрокоманды выделены две микрооперации,определяющие обращение к управляющейпамяти 7 и работу мультиплексора 3команды. Управление мультиплексором3 команд и обращением к управляющей памяти 7 осуществляется первымидвумя выходами дешифратора 6 и происходит во время С 3. При единичномзначении на первом выходе дешифратора 6 к входу управляющей памяти 7подключается информация, поступающая на вход мультиплексора 3 командиз регистра 1 команд. При единичномзначении на втором выходе дешифратора 6 к входу управляющей памяти 7подключается информация, поступающая на второй вход мультиплексора 3с входа 4. Стробирование обращенияк управляющей памяти 7 осуществляется единичным сигналом с выхода схемыИЛИ 5, объединяющей сигналы управ-.ления мультиплексором команд 3 поИЛИ.Единичное значение сигнала на выходе схемы ИЛИ 5 разрешает прохождение фазы С 1 через элементы 8 и9 на входы синхронизации исполнительных регистров 25 и 26 и тем самым занесение поступившей на регистры 25 и 26 информации. Дальнейшеефункционирование устройства проис,ходит описанным способом,Второй режим формирует код модификации из содержимого поля той микрокоманды, в которой это поле для управления узлами ЭВМ в данной микрокоманде не используется. В этом случае в микрокоманде код поля 44 состоит из единиц, Это разрешает подключение через мультиплексоры 11 и 12 полей микрокоманд к входам исполнительных регистров 25 и 26 данных из соответствующих полей 43 регистра микрокоманд 19. Данные, поступившие на входы мультиплексоров 11 и 12 полей микрокоманд из регистра 19 микрокоманд, согласно сигналу на управляющем входе подключаются к входу исполнительных регистров 25 и 26. Единичное значение полей 44 разрешает прохождение фазы С 1 с элеиентов 8 и 9 на управляющие входы исполнительных регистров 25 и 26 и тем самым занесение данных из полей 43 регистра микрокоманд в испол-.11 1134935 12 нительные регистры 25 и 26. Дальней- на первый управляющий вход мультишее Функционирование устройства про- плексора 27 и разрешает подключение исходит описанным выше способом. к первому входу сумматора 29 данных,Формирование адреса микрокоманд поступивших на первый вход мульти- осуществляется следующим образом. 5 плексора 27 с выхода регистра адреБлок 10 Формирования адреса мик- са 30. На выходах 32-34 в это время рокоманд в соответствии с сигналами сигналы отсутствуют, что и вызывана его первых пяти управляющих вхо- ет реализацию Функции РА + 1 на выдах, поступивших с дешиФратора 14 ходе сумматора 29. При появлении во время С 3, Формирует адрес микро сигнала на выходе дешиФратора 14, команды согласно одному из следующих подключенного к входу 39 блока 10, способов: РА + 1, РА + КВ + 1, вырабатываются сигналы на выходах (РА Ч ИУ) + 1, ИУ + 1, (РА Ч КВ) + элементов ИЛИ 35 и 37, что вызывает + ШУ + 1, где РА - содержимое регист- реализацию Функции РА + КВ + 1 на ра адреса 30, КВ в .код условий вет выходе сумматора 29. При появлении влений на входе 13, ПУ - код с вы- сигнала на выходе дешифратора 14, .хода блока управляющей памяти 7, подключенного к входу 40 блока 10В который используется для Формирова- вырабатываются сигналы на выходах ния начального адреса микропрограм- элементов ИЛИ 35 и 36, что вызывает мы отработки команд. При блокиро реализацию Функции (РА Ч ПУ) + 1 на ванном дешиФраторе, т.е. отсутствии выходе сумматора 29, При появлении управляющих сигналов, на регистре сигнала на выходе дешиФратора 14, адреса 30 Формируется адрес микро- подключенного к входу 4 1 блока 10, команды, равный 1: Выход, подключен- вырабатывается сигнал на выходе ный к первому управляющему входу 31 25 элемента ИЛИ 36, что вызывает реалимультиплексора 27, разрешает подклю- зацию Функции ИУ + 1 на выходе сумчение через него к первому входу матора 29. При появлении сигнала сумматора 29 данных с регистра адре- на выходе дешиФратора 14, подключенса 30. Вьиод, подключенный к вто- ного к входу 42 блока 10, вырабатырому управляющему входу 32 мульти- з 0 вается сигнал на выходах элементов плексора 27, разрешает подключение 36 и 37, а также на управляющем через него к первому входу суммато- входе 40 мультиплексора 28, что и . ра 29 данных с первого входа блока вызывает реализацию Функции (РА Ч КВ)+.10 Формирования адреса микрокоманд, + ШУ + 1 на выходе сумматора 29. т.е. данных с выхода блока управля Данные с выхода сумматора 29 пос-ющей памяти 7. Выход, подключенный .тупают на вход регистра адреса 30 к первому управляющему входу 33 муль под управлением синхросигнала С 1. типлексора 28, разрешает подключение через него к второму входу сум- Таким образом, если в известном матора 29 данных с регистра адреса . 4 о устройстве для перехода в режим зане.30. Выход, подключенный к второму : сения в дешиФратор инФормации из исуправляющему входу 34 мультиплексо- полнительного регистра и для перехора 29 разрешает подключение через да в режим занесения в дешиФратор него к второму входу сумматора 29 микрокоманды из регистра микрокоманд данных с второго входа блока 10 Фор.необходима дополнительная команда мирования адреса микрокоманды, т.е. изменения состояния логической ячейкода условий ветвлений на. входе 13 ки, то в предлагаемом устройствепереключение режима занесения управ"При появлении сигнала на выходе лякщих кодов в дешиФратор осущестдешиФратора 14, подключенного к уп- о вляется специальным кодом модиФикаравляющему входу блока 10 Формирова- ции необходимого поля в текущей ьвк ния адреса микрокомандыик входу 38 рокоманде, что увеличивает быстро- блока 10, вырабатывается сигнал на действие предложенногоустройствапо выходе элемента ИЛИ 35.0 н поступает сравнению с устройством-прототипом.1134935 8. останитель Ю.ЛанцоехредС.Легеза рректор Х.Леьяик Редактор ткина сное 1 о ний4 нт", г. Уюород оектна Фили Заказ 10090/41, Тираж 710 ВНИИПИ Государственн по делам изобрете 133035, Москва, М, Р

СмотретьЗаявка

3591224, 13.05.1983

ОРДЕНА ЛЕНИНА ИНСТИТУТ КИБЕРНЕТИКИ ИМ. В. М. ГЛУШКОВА

ИВАНОВ ВЛАДИМИР АНДРЕЕВИЧ, КАМИНСКИЙ СЕРГЕЙ ИГОРЕВИЧ, СЫРОВ ВИКТОР ВАЛЕНТИНОВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 15.01.1985

Код ссылки

<a href="https://patents.su/9-1134935-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Устройство для умножения

Следующий патент: Микропрограммное устройство управления

Случайный патент: Устройство для демонтажа поглощающего аппарата автосцепки с вагона