Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

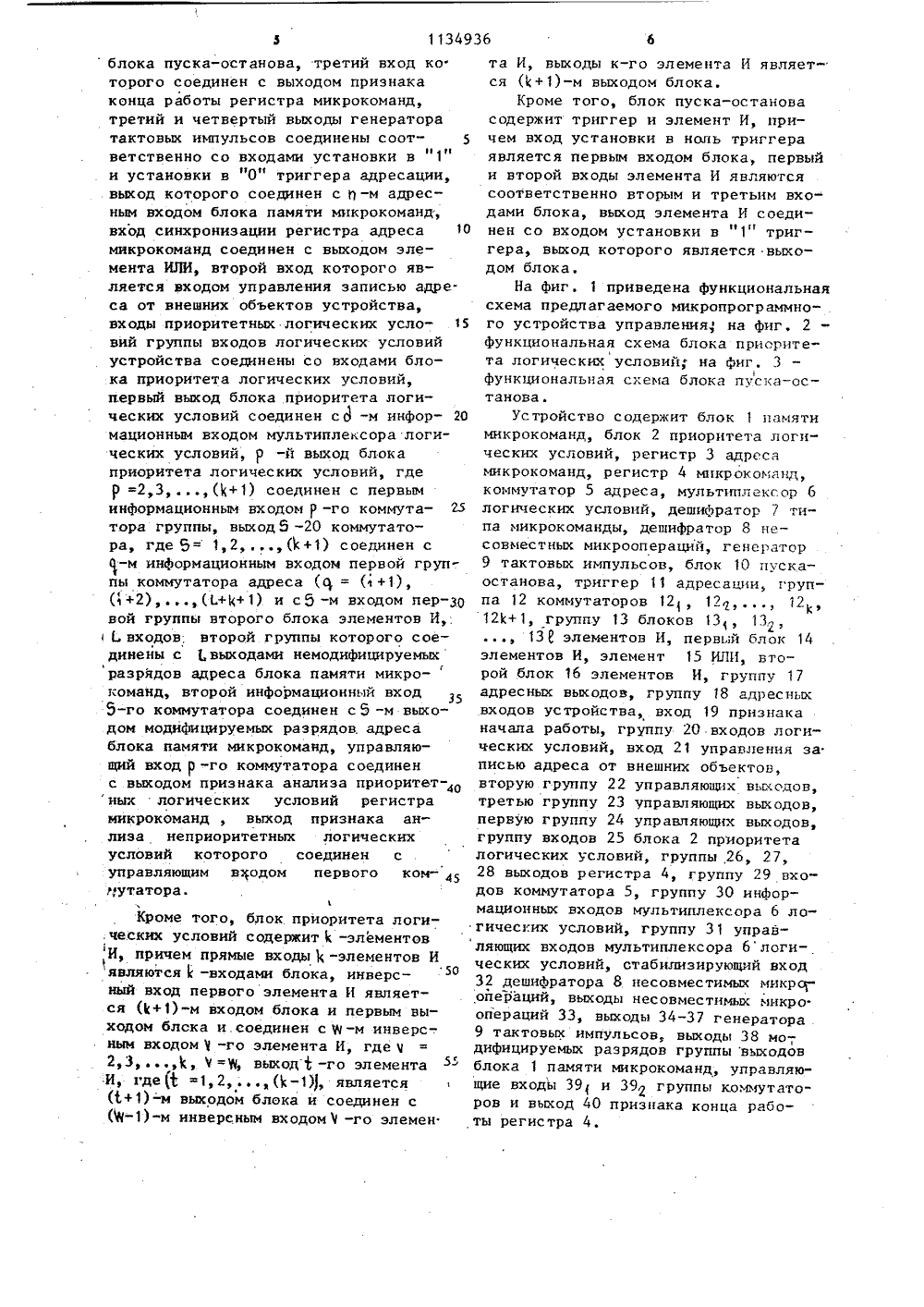

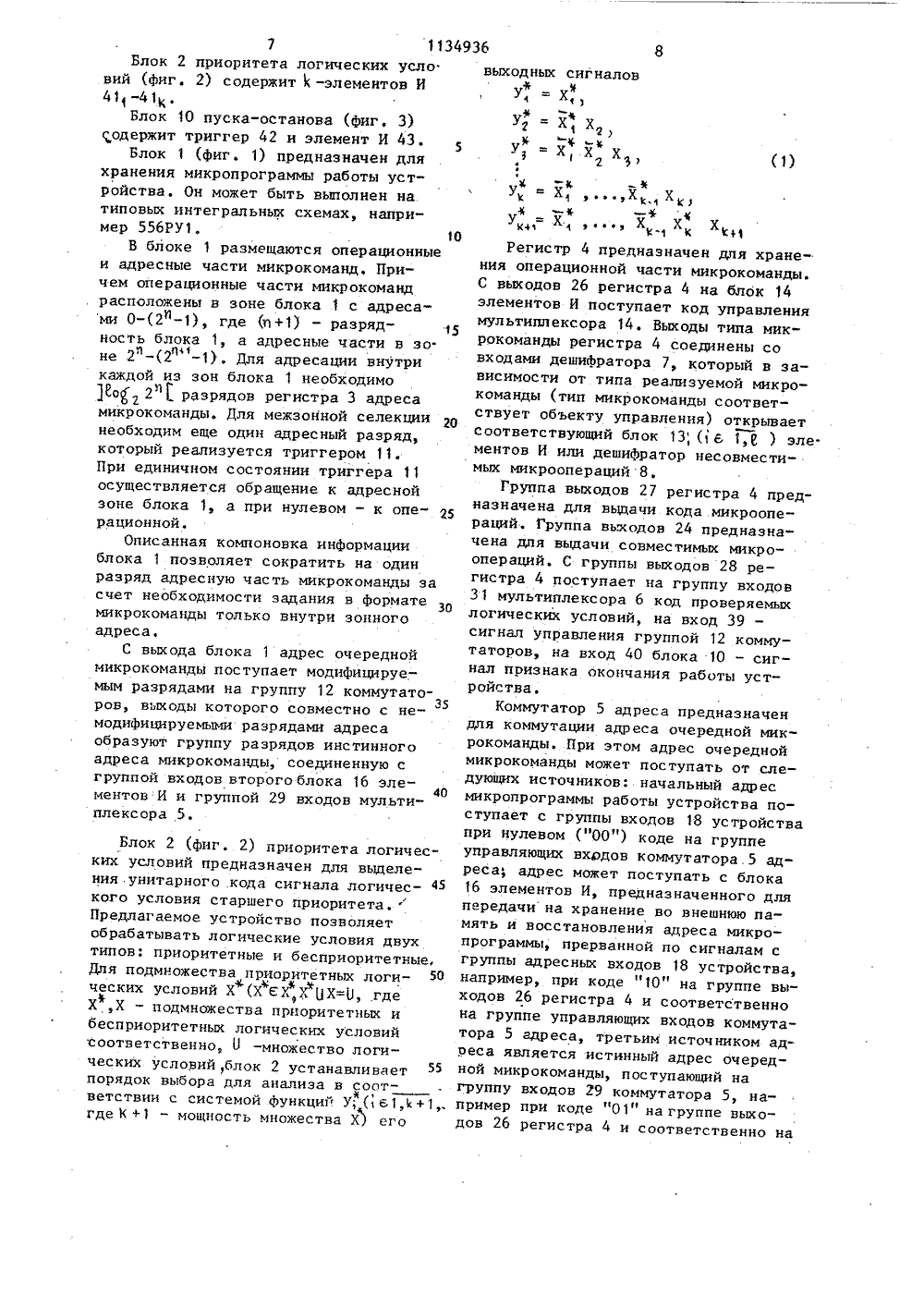

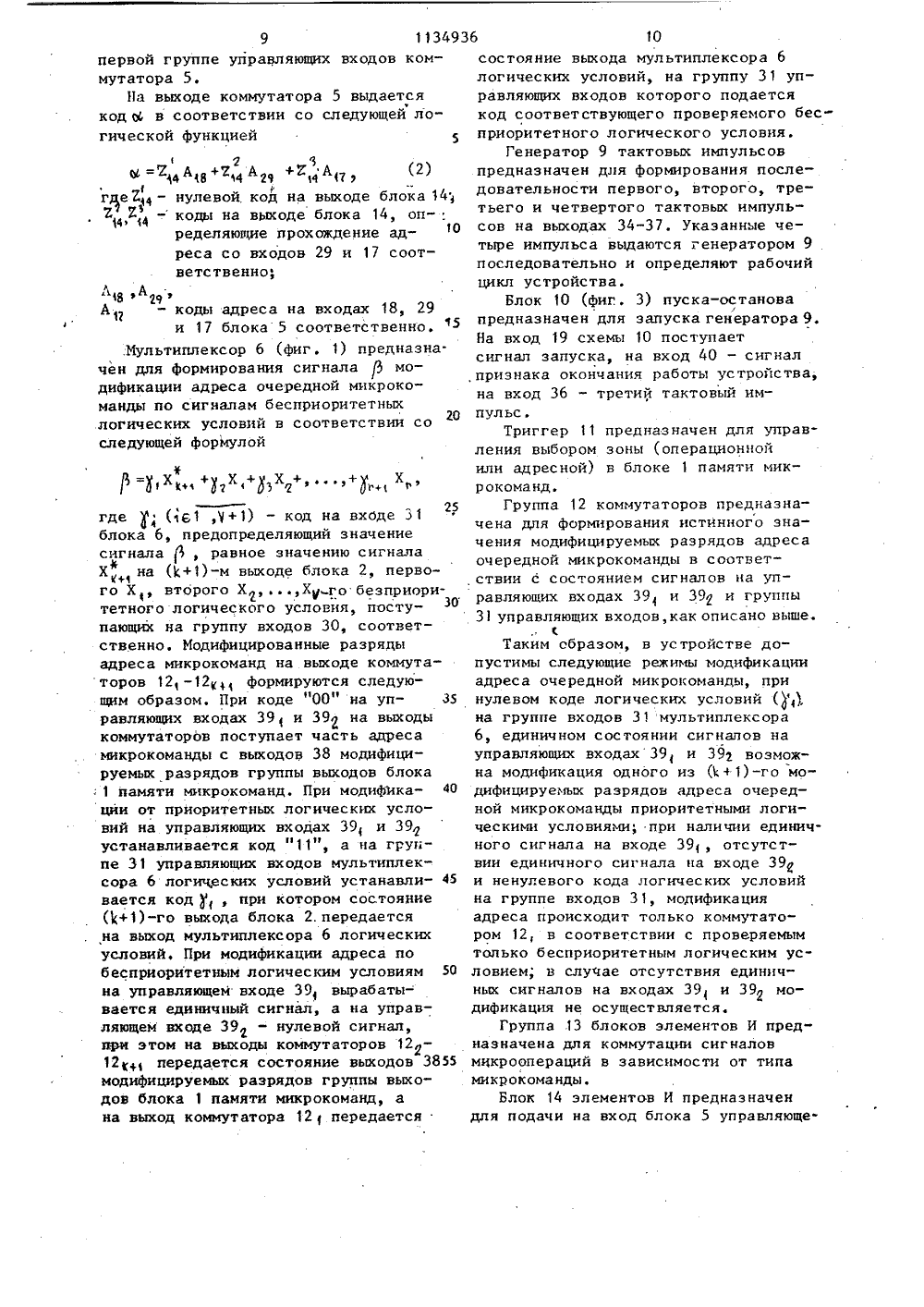

-3" . ммирос,1)Кт деост ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОП (РЫТИЙ ПИСАНИЕ ИЗО ТОРСНОМУ СВИДЕТЕЛЬСТВУ(56) 1,Геолецян А.Г. "ЭВМ НаириПрограммирование и микропрограваниеф М Статистика 197915 2. Авторское свидетельство СССР В 928355, кл. С а 6 Г 9/22, 1982.3. Ээйс Э. Синтез и оптимизация программ с использованием р-функций. Экспресс-информация. Сер. "Вычислительная техника", 1982, Р 36, рис. 1 (прототип).4. Шишмарев А.ИЗаморин А,П. Анг-ло-русско-немецко-французский толковый словарь по вычислительной технике и обработке данныхПод ред. Дород- ицына, М., "Русский язык", 1978(54)(57) 1. МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее блок па-,мяти микрокоманд, регистр адреса ми рокоманд, регистр микрокоманд, коммутатор адреса, мультиплексор логических условий, первый коммутатор, генератор тактовых импульсов и первый блок элементов И, причем группа выходов первого блока элементов И соединена с группой управляющих входов коммутатора адреса, группа выходов которого соединена с группой информационных входов регистра адреса микрокоманд,"й выход которого, г (= 12(п),( - разрядн ь адреса блока памяти микрокоМанд), соединен с- м адресным входом блока памяти микрокоманд, 1. выходов немодифицнруемых разрядов адреса которого, где Ь- число немодифицируемых разрядов адреса, соединены с 1. информационными входами первой группы коммутатора адреса, группа выходов кода управления формированием адреса регистра микро- команд соединена с группой прямых входов первого блока элементов И, вход разрешения формирования адреса микрокоманд устройства соединен с инверсными входами первого блока элементов И, группа выходов кода операций блока памяти микрокоманд и группа выходов кода управления формированием адреса блока памяти мнкрокоманд соединены соответственно с первой и второй группами информационных входов регистра микрокоманд, вход синхронизации которого соединен с первым выходом генератора тактовых Импульсов, группа выходов кода логических условий регистра микрокоманд соединена с группой управляющих входов мультиплексора логических условий,Я -1) информационных входов которого, где д - разрядность кода неприоритетных логических условий, соединены со входами неприоритетных логических условий группы входов логических условий устройства, выход мультиплексора логических условий соединен с первым информационным входом первого коммутатора, пер. вая группа выходов кода микроопераций регистра микрокоманд является первой группой управляющих выходов устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия,1134936 Составитель Ю,ЛанцовТехред С.Легеза Корректор А.Тяск Редактор А.ДОлинич илиал ППП"Патент", г. Ужгород, ул. 11 роектная. аказ 10090/41 Тираж 710 По,цпис н ВНК 4 ПИ Государственного комитета СССР ло делам изобретений и открытий 113035, Чосква, Ж, Раушская наб. д. 4ции регистра адреса микрокоманд соединен с выходом элемента ИЛИ, второй вход которого является входомуправления записью адреса от внешних объектов устройства, входы приоритетньи логических условий группывходов логических условий устройствасоединены со входами блока приоритета логических условий, первый вьиодблока приоритета логических условийсоединен с 3 -м информационным входом мультиплексора логических условий,р -й выход блока приоритеталогических условий,где= 2,3.В+1), соединен с первым информационным входом-го коммутатора группы,вьиод,-го коммутатора,где 5 =1,2,(1+1) соединен с-ым информационнымвходом первой группы коммутатора адреса.Я =О,+1),(1.+2) Й.+1+1) и сб-м входом первой группы второго блока элементов И, Ь входов второй группыкоторого соединены с 1 вьиодами немодифицируемых разрядов адреса блокапамяти микрокоманд, второй информационный вход 5 -го коммутатора соединен с 5 -м выходом модифицируемьи разрядов адреса блока памяти микрокоманд, управляющий вход-го коммутатора соединен с выходом признака анализа приоритетных логических условийрегистра микрокоманд, выход признака анализа неприоритетньи логическихусловий которого соединен с управляю.щнм входом первого коммутатора,2. Устройство по и. 1, о т л и ч а ю щ е е с я тем, что блок приоритета логических условий содержит, к -элементов И, причем прямые входы к-элементов И являются-входами.блока, инверсный вход первого элемента И является (+1)-м входом блока и первым выходом блока и соединен с Ъ-м инверсным входом Ч-го элемента И, где Ч 2,31,Ч =В, вьиод 1-го элемента И где 1 = 1, 2 0-1) является (1+1)-м выходом блока и соединен с (Э)-м инверсным входом М -го элемента И, выходы -го элемента И являются 5+1)-м выходом блока. 3. Устройство по п. 1, о т л и - ч а ю щ е е с я тем, что блок пуска-останова содержит триггер и эле "- мент И, причем вход установки в ноль триггера является первым входом блока, первый и второй входы элемента И являются соответственно вторым и 1134936оно дополнительно содержит блок приоритета логических условий, блок пуска-останова, триггер адресации, совторого по (1+ 1)-ый коммутаторы,где (Ц+1) - число модифицируемых разрядов адреса следующей микрокоманды, группу блоков элементов И, дешифратор типа микрокоианд, дешифраторнесовместимых микроопераций, элемент ИЛИ и второй блок элементов И,причем группа выходов второго блокаэлементов И соединена с группой адресньи выходов устройства и совторой группой информационных входовкоммутатора адреса, третья группа информационньи входов которого является группой адресньи входов устройства, первые .входы второго блока.элементов И соединены со входом приз.нака адресации к внешней памяти устройства, вход признака начала работыустройства соединен с первым входомблока пуске-остаиова, выход которого соединен со входом запуска генератора тактоиьи импульсов, группавыходов кода типа микрокоманды регистра микрокоманд соединена с группой входов дешифратора типа микрокоманд,-й выход которого, где1,2е, (й - количество группсовместимьи микроопераций первоготина) соединен с первыми входами(-го блока элементов И группы, вторые входы которого соединены со входами дешифратора несовместимьи микроопераций и с выходами кода микроопераций регистра микрокоманд второйгруппы, группа вьиодов блоков элементов И группы является второй группойуправляющих выходов устройства, груп"па вьиодов дешифратора несовместимьи микроопераций является третьейгруппой управляющих выходов устройст.ва, стробирующий вход дешифраторанесовместимьи микроопераций соединенс (в+1)-м выходом дешифратора типамикрокоманд, второй выход генератора.,тактовых импульсов соединен с первымвходом элемента ИЛИ и со вторым,входом блока нуска-останова, третийвход которого соединен с выходомпризнака конца работы регистра микрокоманд, третий и четвертый выходы генератора тактовых импульсовсоединены соответственно со входамиустановки в "1" и установки в "О"триггера адресации, выход которогосоединен с и -м адресным входом блокапамяти микрокоманд, вход синхрониза1134936третьим входами блока, выход элемен- "1" триггера, выход которого является та И соединен со входом установки в выходом блокаИзобретение относится к вычислительной технике и может быть использовано для построения устройств управления вычислительных систем.Известно микропрограммное устрой ство управления, содержащее блоки памяти адресных и операционных микро- команд, регистр адреса, счетчик микрокоманд, блок синхронизации, элементы И, ИЛИ Я .10Недостатком этого устройства является узкая область применения, обусловленная невозможностью реализации проверки приоритетных логических условий. 15Известно также микропрограммное устройство управления, содержащее регистры адреса и микрокоманд, блок памяти микрокоманд, элементы И, ИЛИ 2,Недостатком устройства является 20 узкая область применения.Наиболее близким к предлагаемому устройству по технической сущности и достигаемому эффекту является микпропрограммное устройство управления, 5 содержащее блок памяти микрокоманд, регистр микрокоманд, коммутатор адреса, мультиплексор логических условий, первый коммутатор и блок элементов И, причем выход блока элементов 30 И соединен с первой группой входов коммутатора адреса, группа выходов которого соединена с информационными входами регистра адреса микрокоманд, группа выходов регистра адреса микро- З 5 команд соединена с соответствующими О разрядами где (и+ 1) - число ячеек в блоке памяти микрокаманд), грятпы адресных входов блока памяти микрокоманд, выходы немодифицируемых раз-ц рядов группы выходов которого соединены с соответствующими входами немодифицируемых разрядов второй группы входов коммутатора адреса, выход первого модифицируемого разряда груп-;45 пы выходов блока памяти и микрокоманд соединен с первым информационным входом первого коммутатора, выход которого соединен.с соответствующим -входом модифицируемых разрядов второй группы входов коммутатора адре. са, группа выходов блока памяти микрокоманд соединена с группой информационных входов регистра микрокоманд, первая группа выходов которого соединена с группой информационных входов блока элементов И, выходы разрядов логических условий второй группы выходов регистра микрокоманд соединены с группой управляющих входов мультиплексора логических условий, .первая группа информационных входов которого соединена со входами разрядов .бесприоритетных логических условий группы входов логических условий устройства, выход первого управляющего разряда второй группы выходов регистра микрокоманд соединен с управляющим входом первого коммутатора 13 .Недостатком данного устройства является низкое быстродействие, обусловленное сложностью обработки прерываний на микропрограммном уровне, Для реализации реакции на приоритетные логические условия, вызывающие прерывания, в прототипе необходимо выполнить следующие действия.Периодически, с требуемой частотой реакции на приоритетные логические условия в устройстве должно передаваться управление специальной микропрограмме, осуществляющей так называемый "поллинг" 4), т.е. циклическую проверку этих логических условий в порядке уменьшения приоритета. В случае положительного исхода проверки какого-либо приоритетного условия управление должно передаваться мик ропрограмме организации реакции на это условие , а адрес возврата в микропрограмму поллинга - запоминаться. После завершения обработки данного приоритетного логического условия производится возврат к микропрограмме 1поллинга и далее на прерванную. "поллингом" микропрограмму.3 1134Поскольку микропрограмма "поллинга" должна выполняться довольно часто, то быстродействие прототипа существенно снижается. Кроме того, после выполнения "поллинга" для осуществления возврата в основную микропрограмму для каждой точки возврата необходимо вырабатывать фиктивные логические условия, идентифицирующие точку возврата, Сказанное относится 10 также к возврату из микропрограммы- обработчика прерывания.Целью изобретения является повышение быстродействия.15Поставленная цель достигается тем, что в микропрограммное устройство управления, содержащее блок памяти микрокоманд регистр адреса микро- команд, регистр микрокоманд, коммутатор адреса, мультиплексор логических условий, первый коммутатор генератор тактовых импульсов и первый блок элементов И, причем группа выходов первого блока элементов И соединена с группой управляющих входов коммутаэтора адреса, группа выходов которого соединена с группой информационных входов регистра адреса микрокоманд,-й выход которого, где= 1,2 (П) ( й - разрядность адреса блока- памяти микрокоманд, соединен с-м адресным входом блока памяти микрокоманд, (.-выходов немодифицируемых разрядов адреса которого,где . - число немодифицируемых разрядов адреса, 35 соединены с (.информационными, входами первой группы коммутатора адреса, группа выходов кода управления формиро" ванием адреса регистра микрокоманд соединена с группой прямых входов первого4 О блока элементов И,вход разрешения формирования адреса микрокоманд устройства соединен с инверсными входами пер вого блока элементов, И, группа выходов кода операций блока памяти мик рокоманд и группа выходов кода управления формирования адреса блока памяти микрокоманд соединены соответственно с первой и второй группами информационных входов регистра мик"50 рокоманд, вход синхронизации которо" го соединен с первым выходом генератора тактовых импульсов, группа выходов кода логических условий регистра микрокоманд соединена с груп пой управляющих входов мультиплексора логических условий, Ы) информационных входов которого, где 3, - раз 93 б 4рядность кода неприоритетных логический условий, соединены со входами неприоритетных логических условийгруппы входов логических условий устройства, выход мультиплексора логических условий соединен с первым информационным входом первого коммутатора, первая группа выходов кода микроопераций регистра микрокоманд является первой группой управляющихвыходов устройства, дополнительновведены блок приоритета логическихусловий, блок пуска-останова, триггер адресации, со второго по %+1)-йкоммутаторы, где (+ 1) - число модифицируемых разрядов адреса следующеймикрокоманды, группу блоков элементов И, дешифратор типа микрокоманд,дешифратор несовместимых микроопераций, элемент ИЛИ и второй блокэлементов И, причем группа выходоввторого блока элементов И соединенас группой адресных выходов устройства и со второй группой информационныхвходов коммутатора адреса, третьягруппа информационных входов которого является группой адресных входовустройства, первые входы второго блока элементов И соединены со входомпризнака адресации и внешней памятиустройства, вход признака начала ра- .боты устройства соединен с первымвходом блока пуска-останова, выходкоторого соединен со входом запускагенератора тактовых импульсов, группа выходов кода типа микрокоманды рагистра микрокоманд соединена с группой входов дешифратора типа микрокоманд, 1 -й выход которого, где1,2п 1, (т - количество групп совместимых микроопераций первого типа)соединен с первыми входами 1 -го блока элементов И группы, вторые входыкоторого соединены со входами дешифратора несовместимых микроопераций и с выходами кода микрооперацийрегистра микрокоманд второй группы,группа выходов блоков элементов Игруппы является второй группой управляющих выходов устройства, группа вы"ходов дешифратора несовместимых микроопераций является третьей группойуправляющих выходов устройства, стробирующий вход дешифратора несовместимых микроопераций соединен с Ь+ 1) -мвыходом дешифратора типа микрокоманд, второй выход генератора тактовых импульсов соединен с первым входом элемента ИЛИ и со вторым входомблока пуска-останова, третий вход которого соединен с выходом признакаконца работы регистра микрокоманд,третий и четвертый выходы генераторатактовых импульсов соединены соответственно со входами установки в "1"и установки в "0" триггера адресации,выход которого соединен с О -м адресным входом блока памяти микрокоманд,вход синхронизации регистра адреса 10микрокоманд соединен с выходом элемента ИЛИ, второй вход которого является входом управления записью адреса от внешних объектов устройства,входы приоритетных логических условий группы входов логических условийустройства соединены со входами блока приоритета логических условий,первый выход блока приоритета логических условий соединен со -м информационным входом мультиплексора логических условий, р -й выход блокаприоритета логических условий, где=2,3(+1) соединен с первыминформационным входом-го коммутатора группы, выход 5 -20 коммутатора, где 5= 1,2 6+1) соединен с-м информационным входом первой груп-.пы коммутатора адреса (с = 6+1),(4+2)(Ь1) и сб -м входом пер-З 0вой группы второго блока элементов И,Ь входов второй группы которого соединены с (,выходами немодифицируемыхразрядов адреса блока памяти микрокоманд, второй информационный вход5-го коммутатора соединен с б -м выходом модифицируемых разрядов. адресаблока памяти микрокоманд, управляющий вход р -го коммутатора соединенс выходом признака анализа приоритет ных логических условий регистраиикрокоманд , выход признака анлиза неприоритетных логическихусловий которого соединен суправляющим втодом первого коммутатора,Кроме того, блок приоритета логи.ческих условий содержит к -элементов,И, причем прямые входы-элементов Иявляются-входами блока, инверсный вход первого элемента И является (+1)-м входом блока и первым выходом блока и соединен с В-м инверсным входом М -го элемента И, где Ч23,,1, Ч =%, выход 1 -го элементаИ, где ф 1,2,Ь), является(М)-м инверсным входом Ч -го элемен та И, выходы к-го элемента И является 6+1)-м выходом блока.Кроме того, блок пуска-останова содержит триггер и элемент И, причем вход установки в ноль триггера является первым входом блока, первый и второй входы элемента И являются соответственно вторым и третьим входами блока, выход элемента И соединен со входом установки в "1" триггера, выход которого является выходом блокаНа фиг, 1 приведена функциональная схема предлагаемого микропрограммного устройства управления на фиг, 2 - функциональная схема блока приоритета логических условий," на фиг, 3 функциональная схема блока пуска-останова.Устройство содержит блок 1 памяти микрокоманд, блок 2 приоритета логических условий, регистр 3 адреса микрокоманд, регистр 4 микрокомацд, коммутатор 5 адреса, мульттптлексор 6 логических условий, дешифратор 7 типа микрокоманды, дешифратор 8 не - совместных микроопераций, генератор 9 тактовых импульсов, блок 10 пускаостанова, триггер 11 адресации, группа 12 коммутаторов 121, 12 12, 121+1, груттпу 13 блоков 31, 13.-,3 элементов И, первый блок 14 элементов И, элемент 15 ИЛИ, второй блок 16 элементов И, группу 17 адресных выходов, группу 18 адресных входов устройства, вход 19 признака начала работы, группу 20 входов логических условий, вход 21 управления за писью адреса от внешних объектов, вторую группу 22 управляющих выходов, третью группу 23 управляющих вьжодов, первую группу 24 управляющих выходов, группу входов 25 блока 2 приоритета логических условий, группы 26, 27, 28 выходов регистра 4, группу 29 входов коммутатора 5, группу 30 информационных входов мультиплексора 6 логических условий, группу 3 1 управляющих входов мультиплексора блогических условий, стабилизирующий вход 32 дешифратора 8. несовместимых микро"ойераций, выходы несовместимых микро.операций 33, выходы 34-37 генератора9 тактовык импульсов, выходы 38 мо-, дифицнруемых разрядов группы выходов блокапамяти микрокоманд, управляющие входы 39 и 392 группы коммутаторов и выход 40 признака конца работы регистра 4.7 113493Блок 2 приоритета логических условий (фиг. 2) содержит 1 -элементов И411-41 .Блок 10 пуска-останова (Фиг. 3)содержит триггер 42 и элемент И 43Блок 1 (фиг. 1) предназначен дляхранения микропрограммы работы устройства. Он может быть выполнен натиповых интегральных схемах, например 556 РУ 1, 1 ОВ блоке 1 размещаются операционныеи адресные части микрокоманд. Причем операционные части микрокомандрасположены в зоне блока 1 с адресами 0-(2"-1), где (и+1) - разрядность блока 1, а адресные части в зо.не 2"-(2 -1), Для адресации внутрикаждой из зон блока 1 необходимо11 о 2 п разрядов регистра 3 адресамикрокоманды. Для межзонной селекциинеобходим еще один адресный разряд,который реализуется триггером 11.При единичном состоянии триггера 11осуществляется обращение к адреснойзоне блока 1, а при нулевом - к опе- драционной.Описанная компоновка информацииблока 1 позволяет сократить на одинразряд адресную часть микрокоманды засчет необходимости задания в Форматемикрокоманды только внутри зонногоадреса,С выхода блока 1 адрес очередноймикрокоманды поступает модифицируемым разрядами на группу 12 коммутато 35ров, выходы которого совместно с не- "модифицируемыми разрядами адресаобразуют группу разрядов инстинногоадреса микрокоманды, соединенную сгруппой входов второго блока 16 элементов И и группой 29 входов мультиплексора 5.Блок 2 (фиг. 2) приоритета логических условий предназначен для вьделения унитарного кода сигнала логичес кого условия старшего приоритета.Предлагаемое устройство позволяет обрабатывать логические условия двух типов: приоритетные и бесприоритетные, Для подмножества приоритетных логических условий Х (Х Е 7.,Х 1 Х=0, гдек м,%Х,Х - подмножества приоритетных и бесприоритетных логических условий соответственно, 0 -множество логических условий, блок 2 устанавливает порядок выбора для анализа в соответствии с системой функций У; (1 е 1,1 + 1,.где К + 1 - мощность множества Х) его выходных сигналовУ = Х1 1)Уг =Х,Х,м Ф -кУ =Х,Х Х, (1)к -к %Х,ХкХ к4 - Ф %у = Х,Х,Хк 1Регистр 4 предназначен для хранения операционной части микрокоманды.С выходов 26 регистра 4 на блок 14элементов И поступает код управлениямультиплексора 14. Выходы типа микрокоманды регистра 4 соединены совходами дешифратора 7, который в зависимости от типа реализуемой микрокоманды (тип микрокоманды соответствует объекту управления) открываетсоответствующий блок 13,(1 6 3,К ) элементов И или дешифратор несовместимых микроопераций 8.Группа выходов 27 регистра 4 предназначена для выдачи кода микроопераций. Группа выходов 24 предназначена для выдачи совместимых микроопераций. С группы выходов 28 регистра 4 поступает на группу входов3 1 мультиплексора 6 код проверяемыхлогических условий, на вход 39 -сигнал управления группой 12 коммутаторов, на вход 40 блока 10 - сигнал признака окончания работы устройства.Коммутатор 5 адреса предназначендля коммутации адреса очередной микрокоманды. При этом адрес очередноймикрокоманды может поступать от следующих источников: начальный адресмикропрограммы работы устройства поступает с группы входов 18 устройствапри нулевом ("00") коде на группеуправляющих входов коммутатора.5 адреса, адрес может поступать с блока16 элементов И, предназначенного дляпередачи на хранение во внешнюю память и восстановления адреса микропрограммы, прерванной по сигналам сгруппы адресных входов 18 устройства,например, при коде "10" на группе выходов 26 регистра 4 и соответственнона группе управляющих входов коммутатора 5 адреса, третьим источником адреса является истинный адрес очередной микрокоманды, поступающий нагруппу входов 29 коммутатора 5, например при коде "01" на группе выходов 26 регистра 4 и соответственно напервой группе управляющих входов коммутатора 5.На выходе коммутатора 5 выдается код с 6 в соответствии со следующей логической функцией 5ггеЕН- нулевой. код на выходе блока 14- коды на выходе блока 14 оп- .14 14Уределяющие прохождение адреса со входов 29 и 17 соответственно;18 ф 2 ефА - коды адреса на входах 18, 29и 17 блока 5 соответственно,:Мультиплексор б (фиг. 1) предназначен для формирования сигнала /3 модификации адреса очередной микрокоманды по сигналам бесприоритетных логических условий в соответствии со20 следующей формулой% 25 где(61,+1) - код на входе 31 блока б, предопределяющий значение сигнала 3, равное значению сигнала Х на Й+1)-м выходе блока 2, первоК+Яго Х, второго Х 2,..,Х 1-го безприоритетного логического условия, поступающих на группу входов 30, соответственно. Модифицированные разряды адреса микрокоманд на выходе коммутаторов 12, - 12 формируются следующим образом. При коде 00" на уп равляющих входах 391 и 39 на выходы коммутаторов поступает часть адреса микрокоманды с выходов 38 модифицируемых разрядов группы выходов блока : 1 памяти микрокоманд, При модифнка ции от приоритетных логических условий на управляющих входах 391 и 392 устанавливается код "11", а на группе 31 управляющих входов мультиплексора 6 логических условий устанавли вается код, при котором состояние 5+1)-го выхода блока 2.передается на выход мультиплексора 6 логических условий. При модификации адреса по бесприоритетным логическим условиям 50 на управляющем входе 39 вырабатывается единичный сигнал, а на управляющем входе 392 - нулевой сигнал, при этом на выходы коммутаторов 12- 12+ передается состояние выходов 3855 модифицируемых разрядов группы выходов блока 1 памяти микрокоманд, а на выход коммутатора 12передается состояние выхода мультиплексора 6 логических условий, на группу 3 1 управляющих входов которого подается код соответствующего проверяемого бесприоритетного логического условия.Генератор 9 тактовых импульсов предназначен для формирования последовательности первого, второго, третьего и четвертого тактовых импульсов на выходах 34-37. Указанные четыре импульса выдаются генератором 9 . последовательно и определяют рабочий цикл устройства.Блок 10 (Фиг 3) пуска-останова предназначен для запуска генератора 9, На вход 19 схемы 10 поступает сигнал запуска, на вход 40 - сигнал признака окончания работы устройства, на вход 36 - третий тактовый импульс.Триггер 11 предназначен для управления выбором эоны (операционнойили адресной) в блоке 1 памяти микрокоманд,Группа 12 коммутаторов предназначена для формирования истинного эначения модифицируемых разрядов адресаочередной микрокоманды в соответствии с состоянием сигналов на управляющих входах 391 и 39 и группы31 управляющих входов, как описано выше. с Таким образом, в устройстве допустимы следующие режимы модификацииадреса очередной микрокоманды, принулевом коде логических условий (ф,на группе входов 31 мультиплексора6, единичном состоянии сигналов науправляющих входах 391 и 392 возможна модификация одного из 5+1) - го модифицируемых разрядов адреса очередной микрокоманды приоритетными логическими условиями; при наличии единичного сигнала на входе 39, отсутствии единичного сигнала на входе 39 и ненугевого кода логических условий на группе входов 3 1, модификацияадреса происходит только коммутатором 12, в соответствии с проверяемым только бесприоритетным логическим условием; в случае отсутствия единичных сигналов на входах 391 и 39 модификация не осуществляется.Группа 13 блоков элементов И предназначена для коммутации сигналовмикроопераций в зависимости от типамикрокоманды. Блок 14 элементов И предназначендля подачи на вход блока 5 управляюще 11 11349го кода с выходов 26 регистра 4 прнотсутствии блокирующего сигнала наего инверсных входах.Элемент ИЛИ 15 предназначен дляформирования импульса управлениязаписью в регистр 3 адреса микрокоманды, занесении адреса в который может осуществляться либо по импульсус выхода 36 генератора 9, либо посигналу записи со входа 2 1 устройства, который подается на этот входпри необходимости занесения адресаизвне со входов 18 устройства.Блок 16 элементов И предназначендля обеспечения передачи адреса микрокоманды немодифицируемьи разрядовс выхода блока 1, а модифицированныхразрядов с выхода коммутаторов 121 -12Рассмотрим работу предлагаемогоустройства,В исходном состоянии все элементы,памяти находятся в нулевом состоянии. На входы 18 (фиг. 1) подаетсяадрес первой микрокоманды микропрограммы (код реализуемой команды),сигнал входа разрешения формирования адреса микрокоманд устройства закрывает блок 14 элементов И. Сигнална вторых входах блока 16 элементовИ отсутствует, по сигналу со входа21 устройства осуществляется залисьв регистр 3 через коммутатор 5 адреса первой микрокоманды, после чегосигнал со входа разрешения формирования адреса микрокоманд устройства35снимается, а затем сигналом со входа 19 триггер 42 (фиг. 3) устанавливается в единичное состояние и включа.ет генератор 9 (фиг. 1) .По первому тактовому импульсу свыхода 34 генератора 9 происходитзапись в регистр 4 информации изблокаС выходов 26 регистра 4 выдаетсякод 2 , разрешающий прохождение навходы регистра 3 сигналов группы входов 29 коммутатора 5.По второму тактовому импульсу свыхода 35 генератора 9 триггер 11 5 О устанавливается в единичное состоя,ние, предопределяя задание адреса в зоне старших адресов блока 1, где записаны адресные части микрокоманд.По третьему тактовому импульсу с 55выхода 36 генератора 9 через коммутатор 5 в регистр 3 записывается код адреса очередной микрокоманды. Таким образом, адрес очередной микрокоманды через блок 16 поступает на выходы 17 и запоминается во внешней (стековой) памяти (память процессора.внешнего уровня управления вычислительной системы), а через коммутатор 5 в регистр 3 записывается13 1134936 14 адрес первой микрокоманды прерывающей ство выполняет заданную микропрограммикропрограммы, му аналогично описанному,Далее о очередному четвертому так. При необходимости завершения ратовому импульсу с выхода 37 гене- боты с выхода 40 выдается сигнал ратора 9 триггер 11 устанавливаетсяокончания работы, по которому при в нулевое состояние и устройство вы- наличии третьего тактового импульполняет заданную микропрограмму ана- са с выхода 36 генератора 9 срабалогично описанному, тывает элемент 43 И (см. фиг. 3), усПри завершении выполнения прерываю- танавливая триггер 42 в нулевое сосщей микропрограммы в последней ее 10 тояние Генератор 9 выключается после микрокоманде на взыкоде 26 регистравьдачи. четвертого тактового импульса 4 выдается код Е, а на одном нз и блокирует работу устройства. выходов группы 24 сигнал, по которо-му на выходы 17 подается из внешней Таким образом, исключение необходипамяти заполненный адрес очередной 1 мости испопьзования микропрограммы микрокоманды прерванной микропрограм- "поллинга" для обработки приоритетмы, По коду Е через коммутатор 5 ных логических условий приводит кЦв регистр 3 передается адрес, посту- повышению быстродействия изобретения лающий по входам 17, и далее устрой- по отношению к прототипу,

СмотретьЗаявка

3619806, 13.07.1983

ПРЕДПРИЯТИЕ ПЯ А-7160

КРИВОНОСОВ АНАТОЛИЙ ИВАНОВИЧ, КИРИЧЕНКО НИКОЛАЙ ВАСИЛЬЕВИЧ, КАЛМЫКОВ ВАЛЕНТИН АЛЕКСАНДРОВИЧ, СУПРУН ВАСИЛИЙ ПЕТРОВИЧ, МЕХОВСКОЙ НИКОЛАЙ ФИЛИППОВИЧ, СЫЧЕВ АЛЕКСАНДР ВАСИЛЬЕВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 15.01.1985

Код ссылки

<a href="https://patents.su/10-1134936-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Микропрограммное устройство управления

Следующий патент: Микропрограммное устройство управления

Случайный патент: Устройство для контроля четности двоичного последовательного кода