Формирователь уровня считывания

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

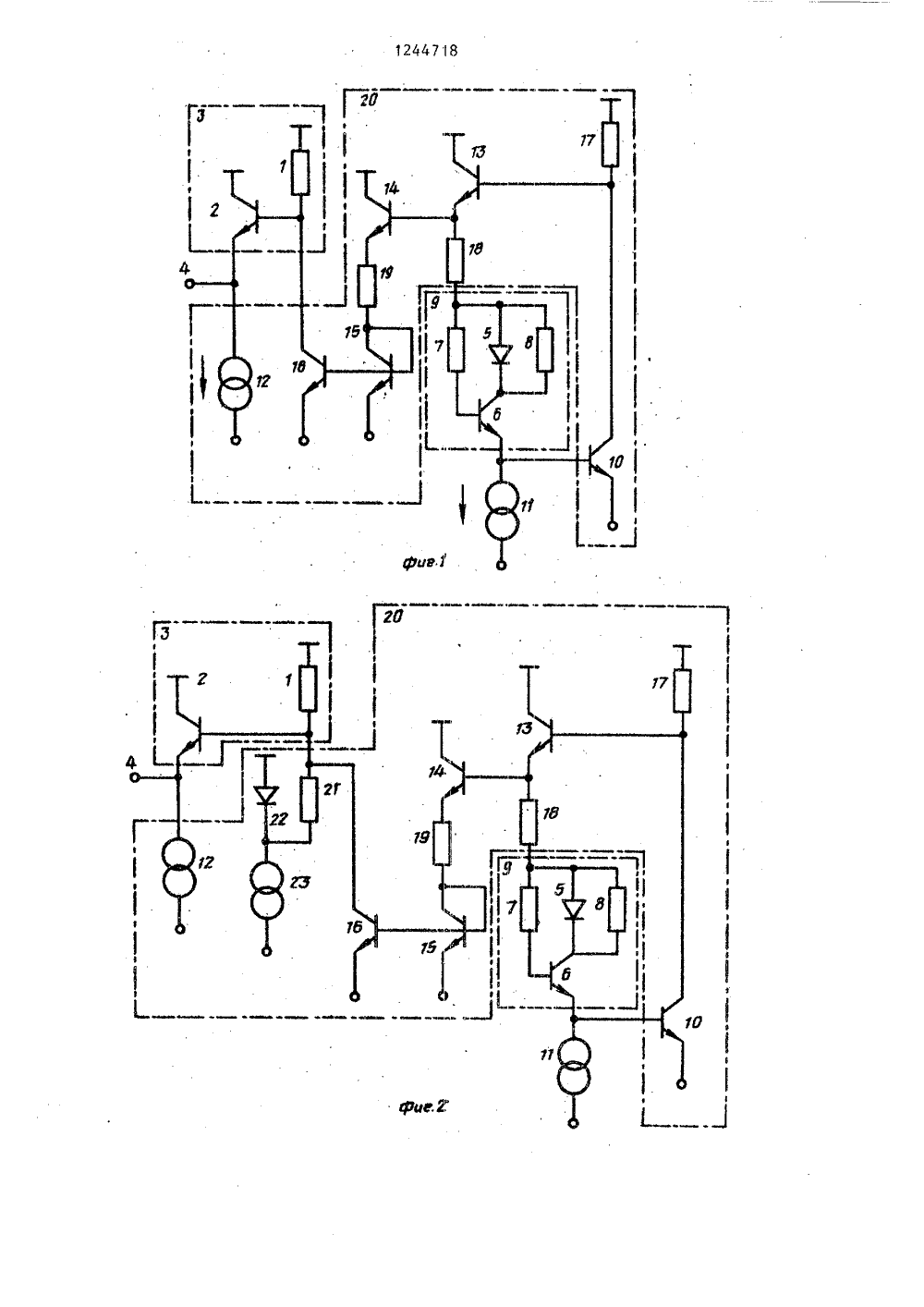

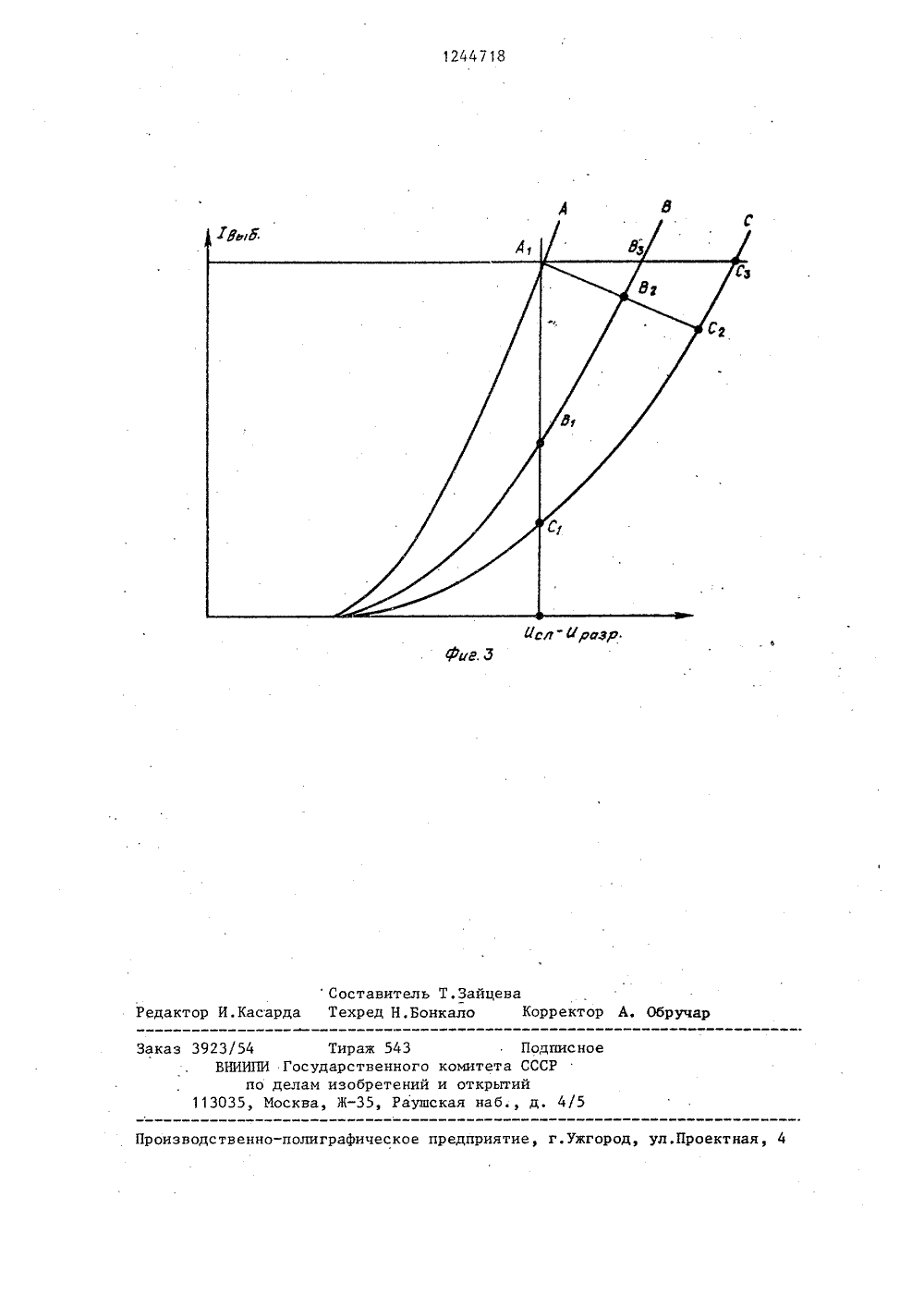

/00,54) ФОРМИ 57) Изоб ельной т НЯ СЧИТЫВАНИЯ тся к вычислибыть исполь ВАТЕЛЬ УР тение относ нике н може полярных статических зап тройствах. Целью нзобрет овано йил. минающих у ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ(56) Патент США У 4кл. 307-238, опублиПатент ФРГ 9 273кл, 422, С 11 Сопублик. 1979. ния является повышение точности формирования уровня считывания. Формирователь уровня считывания содержитпереключающий, нагрузочный, усилительный н три согласующих транзистора, первый диод, два источника тока,шестьрезисторов. Повышение точностиформирования уровня считывания достигается введением четвертого согласующего транзистора .что обеспечиваетувеличение тока, протекающего черезнагрузочный транзистор. Введениев формирователь второго диода,третьего источника тока и седьмогорезистора позволяет учесть перепадлогических уровней. 1 з.п ф-лы, 3Формирователь уровня считывания работает слецующим образом.При изменении величины резистора 18 или коэффициента усиления тока транзистора 6 меняется падение напряжения на резисторе 7 (фиг. 1). Сумма падений напряжений на резисторах 7 и 18 выделяется на резисторе 19, Поэтому ток через резистор 19 изменяется в соответствии с изменением напрякения на резисторе 7, Так как ток ре 50 1 124 7Изобретение относится к вычислительной технике и может быть использовано в биполярных статических запоминающих устройствах,Цель изобретения - повышение точности формирования уровня считывания,На фиг, 1 приведена принципиальнаяэлектрическая схема формирователяуровня считывания, на фиг. 2 - принципиальная электрическая схема вари Оанта выполнения формирователя уровнясчитывания, в котором учитываетсяизменение перепада уровней в ячейкепамяти; на фиг, 3 - диаграмма зависимости уровня считывания от характеристик ячейки памяти, поясняющая работу Формирователя.Формирователь уровня считывания,(фиг. 1) Содержит первый резистор 1и первый согласующий транзистор 2, 2 Овыполняющие функцию эквивалента адресного формирователя 3 с выходом 4,первый диод 5, нагрузочный транзистор 6, второй 7 и третий 8 резисторы, выполняющие функцию эталонной "5ячейки 9 памяти, переключающий транзистор 10, первый 11 и второй 12источники тока, второй 13 и третий 14согласующие, усилительный 15 и четвертый согласующий 16 транзисторы и ЗОрезисторы 17-19 с четвертого по шестой, выполняющие функцию блока 20регулирования. Во вторбм варианте выполнения формирователь уровня считывания содержит также (фиг. 2) седьмой резистор 21, второй диод 22 итретий источник 23 тока.На фиг. 3 показаны зависимостиА, В, С падения напряжения ЗА - Пр ргде Уд - потенциал словарной шины,П . - потенциал разрядной шины, оттока 1, протекающего через ячейку 9 памяти.В качестве. эталонной ячейки 9 памяти могут быть использованы ячейкиразличных типов; тиристорные, инжекционные, с резистивными нагрузками. зистсра 19 ранен току, протекающемучерез транзистор 15, а токи транзисторов 15 и 16 соотносятся также, каксоотносятся площади их эмиттеров, тоток коллектора транзистора 16 изменяется пропорционально изменению напряжения на резисторе 7. На резисторе 1,через который протекает ток коллектора транзистора 16, выделяется перепад напряжения, отслеживающий изменение напряжения на резисторе 7. Этотперепад напряжения через транзистор 2,работающий в режиме эмиттерного повторителя передается на выход. Токисточника 12 тока создает на транзисторе 2 и резисторе 1 падение напряжения, равное падению напряженияна адресном формирователе (на Фиг.1не показано) в результате чего навыходе 4 устанавливается потенциал(относительно шины нулевого потенциала), ра.вныйс% ( кт 1 ь Б 2 ) 3 Бвт 2где Б, - потенциал считывания навыходе 4;Тц.,ь - ток коллектора транзистора 16;Тд 2 - ток базы транзистора 2;К - номинал резистора 1;П. - падение напряжения на переходе база-эмиттер транзистора 2,Величина этого потенциала отличается от потенциала верхнего логического уровня в ячейке памяти накопителя (на фиг, 1 не показано) на вели. чину падения напряжения на резисторе 18.На фиг. 3 кривая А характеризует граничный случай когда. весь ток выборки втекает в ячейку 9 и не течет в транзистор 10. Кривая В соответствует случаю, когда ток выборки делится поровну - одна половина течет в ячейку 9, другая половина - в транзистор 10. Кривая С соответствует случаю, когда большая часть тока выборки течет в транзистор 10. Точки А, В С, отражают случай работы Формирователя в первом варианте выполнения (фиг. 1), не позволяющем учитывать зависимость уровня считывания от параметров ячейки, Наклон линии А, В 2, С обуславливается тем, что ток выборки в формирователе уровня считывания делится на две части Первая часть (большая) течет в ячейку 9 памяти, а вторая - в блок 20.Использование предлагаемого формирователя позволяет избавиться от деления токов между блоком 20 и эталонной ячейкой 9,Формирователь уровня считывания во втором варианте выполнения, позволяющем учитывать перепад логических уровней в ячейке памяти (фиг. 2), работает следующим образомПри изменении параметров ячейки памяти накопителя формирователь уровня считывания устанавливает уровень считывания ниже высокого логического уровня в ячейке памяти накопителя на величину падения напряжения на резисторе 18 (фиг. 1), в результате че. ,го весь ток выборки, за исключением тока эмиттера закрытого транзистора 10, течет в ячейку памяти накопи.теля. Этот режим (фиг. 3) характеризуется точками А, В , С . В этом случае положение уровня считывания определяется соотношением резисторов 1 и 21. Резистор 19 выбирается так, чтобы скомпенсировать ошибку в положении уровня считывания, вносимую базовым током транзистора 1 б.Формула изобретения1. Формирователь уровня считывания, содержащий переключающий, нагрузочный, усилительный и согласующие транзисторы, первый диод, источник тока и резисторы, причем база первого согласующего транзистора соединена с первым выводом первого резистора, а коллектор и второй вывод первого реэиСтора подключены к шине нулевого потенциала, выход первого источника тока соединен с эмиттером нагрузочного транзистора, база которого под" ключена к первому выводу второго резистора, а коллектор соединен с первым выводом третьего резистора и ка-, тодом первого диода, коллектор переключающего транзистора подключен к первому выводу четвертого резистора и базе второго согласующего транзистора, первый вывод пятого резистораподключен к базе третьего согласующего транзистора, коллекторы второгои третьего согласующих транзисторови второй вывод четвертого резисторасоединены с шиной нулевого потенциала, коллектор и база усилительноготранзистора подключены к первому вы воду шестого резистора, входы первого и второго источников тока соединены с шиной питания, о т л и ч а ющ и й с я тем, что, с целью повыше ния точности формирования уровня счи тывания, в формирователь введен четвертый согласующий транзистор, коллектор которого подключен к базе первого согласующего транзистора, абаза соединена с базой усилительноготранзистора, эмиттер которого и эмиттеры четвертого согласующего и переключающего транзисторов подключенык шине питания, причем эмиттер второ.го согласующего транзистора соединен 25 с первым выводом пятого резистора,второй вывод которого подключенк аноду первого диода и вторым выводам второго и третьего резисторов,эмиттер третьего согласующего транзистора соединен с вторым выводомшестого резистора, база переключающего транзистора соединена с выходомпервого источника тока, эмиттер первого согласующего транзистора подклю.чен к выходу второго источника тока 35и является выходом формирователя.2, Формирователь по п. 1, о т л ич а ю щ и й с я тем, что в него введены второй диод, третий источник 40 тока и седьмой резистор, первый выводкоторого соединен с базой первогосогласующего транзистора, а второйвывод и катод второго диода подключены к выходу третьего источника тока,вход которого соединен с шиной питания, причем анод второго диода подключен к шине нулевого потенциала, 12447181244718 Ыраэ 4 ъе 3Составитель Т.Зайцеваактор И.Касарда Техред Н.Бонкало ректор А уча ираж 543рственного к аз 3923/54 ВНИИПИ Госуд по делам 113035, Москва, Подписноета СССР обретении и о -35, Раушская ытииб., д

СмотретьЗаявка

3796995, 01.10.1984

ПРЕДПРИЯТИЕ ПЯ В-2892

ДОРОЖКИН СЕРГЕЙ АНАТОЛЬЕВИЧ, МАКАРОВ АЛЕКСАНДР БОРИСОВИЧ

МПК / Метки

МПК: G11C 7/00

Метки: считывания, уровня, формирователь

Опубликовано: 15.07.1986

Код ссылки

<a href="https://patents.su/5-1244718-formirovatel-urovnya-schityvaniya.html" target="_blank" rel="follow" title="База патентов СССР">Формирователь уровня считывания</a>

Предыдущий патент: Формирователь адресных сигналов для буферной памяти

Следующий патент: Запоминающее устройство

Случайный патент: Способ подземного выщелачивания полезных ископаемых