Формирователь адресных сигналов для буферной памяти

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1244717

Автор: Лупиков

Текст

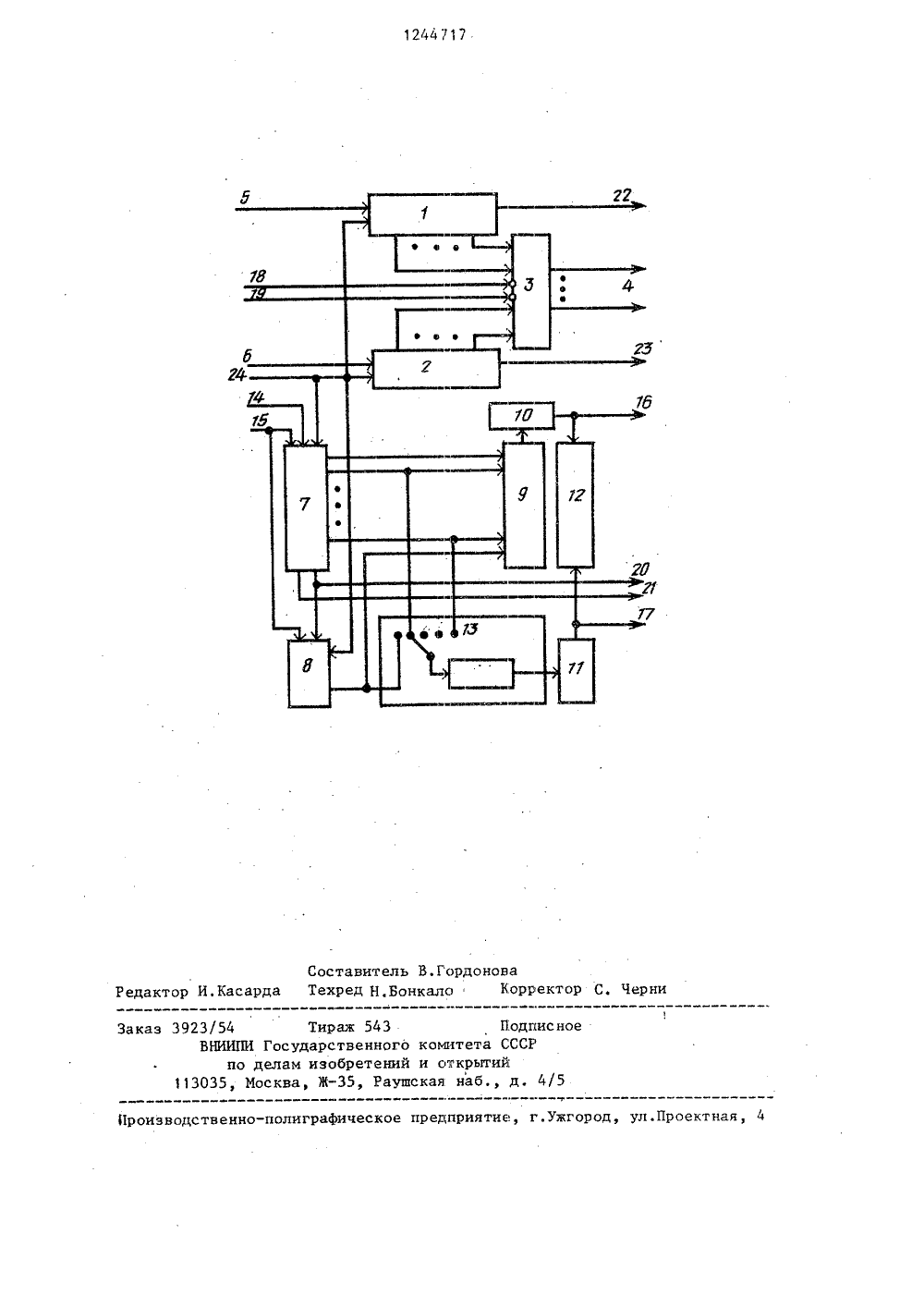

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 4471 1 С 7 ГОСУДАРСПО ДЕЛ БРЕТЕНИЯ ЕТЕПЬСТВУ(56) Авторское свидетельство СССР У 822293, кл, С 11 С 17/00, 1981,Авторское свидетельство СССР В 813504, кл. С 11 С 800, 1981. (54) ФОРМИРОВАТЕЛЬ АДРЕСНЫХ СИГНАЛОВ ДЛЯ БУФЕРНОЙ ПАМЯТИ(57) Изобретение относится к вычислительной технике и может быть испольма, коммутатор, элементы ИЛИ, И- нения формироват счет возможности ности формируемо риггер, кивер ИЛИ. Область и еля расширяетс увеличения ра о адреса. 1 илры, мед ЕНКЫЙ КОМИТЕТ СССРЗОБРЕТЕНИЙ И ОТКРЫТИЙ ОПИСАНИЕ К АВТОРСКОМУ С зовано в качестве формирователя адреса буферного запоминающего устройства для последовательной адресацииячеек памяти. Целью изобретенияявляется расширение области применения формирователя адресных сигналов. Устройство содержит счетчикиадреса записи, чтения, счетчик объеЕсли для ор 1 анизации адресации к буферной памяти требуется один модуль Формирователя адресных сигналов, т,е. К =1, то при его установке необходимо произвести следующую коммутацию управляющих входов: пятьпЪ 18, третий 14 управляющие входы подключаются к первому управляющему входу 5; шестой 19, четвертый 15 управляющие входы подключаются к второму управляющему входу 6. Первый управляющий выход 16 являетоя указателем состоя" ния "Буфер пуст". Второй управляющий выход 17 является указателем состояния "Буфер заполнен".Если для организации адресации и буферной памяти требуется К 1 мо 50 Изобретение относится к вычислительной технике и может быть использовано в качестве формирователя адреса буферного запоминающегоустройства для последовательной адресации ячеек памяти.Цель изобретения - расширениеобласти применения формирователя адресных сигналов за счет увеличенияразрядности Формируемого адреса. 1 ОНа чертеже представлена структурная схема предлагаемого формирователя адресных сигналов.Формирователь адресных сигналовсодержит первый счетчик 1, второйсчетчик 2, элементы 3, И-ИЛИ, адресные выходы 4, первые 5 и второй 6управляющие входы, третий счетчик,3,триггер 8, элемент 9 ИЛИ, первый 10и второй 11 инверторы с открытым коллекторным выходом, согласующий элемент 12, коммутатор 13, третий 14и четвертый 15 управляющие входы,первьп 16 и второй 17 управляющиевыходы, пятый 18 и шестой 19 управляющие входы, третий 20, четвертый 21,пятый 22 и шестой 23 управляющиевыходь 1, установочный вход 24.Формирователь адресных сигналовработает следующим образом ЗОКоличество К модулей Формирователя адресных сигналов зависит от требуемой информационной емкости буферной памяти и определяется как:где И - требуемый информационныйобъем буферной памяти;и - разрядность счетчика 1 (счетчиков 2, 7);К - ближайшее целое число,Щ дулей Формирователя адресных сигналов, то при их установке необходимопроизвести следующую коммутациюуправляющих входов и выходов, Пятый 18, третий 14 управляющие входыпервого (младшие разряды адре:а)модуля формирователя адресных сигналов соединяются с первым управляющимвходом 5 этого модуля и пятыми управляющими входами 18 остальных К модулей. Шестой 19, четвертый 15управпяющие входы первого модуля соединяются с вторым управляющим входом 6 этого модуля и шестыми управляющими входами 19 остальных модулей. Пятый управляющий выход 22 каж -дого модуля, кроме последнегс. (старшие разряды адреса), соединяетсяс первым управляющим входом " последующего модуля. Шестой управляющийвыход 23 каждого модуля, кроме последнего, соединяется с вторым управляющим входом б последующего модуля.Первые управляющие выходы 16 всехмодулей объединяются и являются указателем состояния "Буфер пуст".Вторые управляющие выходы 17 всех модулей объединяются и являются указателем состояния "Буфер заполнен".Третий управляющий выход 20 каждогомодуля, кроме последнего, соединяется с третьим управляющим входом 14последующего модуля. Четвертый управляющий выход 21 каждого модуля, кромепоследнего., соединяется с четвертымуправляющим входом 15 последующегомодуля . Коммутатор 13 всех модулей,кроме последнего, устанавливаетсяв такое положение, при котором к выходу коммутатора 13 подключается выходной сигнал триггера 8. В такое жеположение устанавливается коммута-.тор 13 и в последнем модуле в томслучае, если его разрядность полностьюйспользуется для адресации ячеекбуферной памяти. Если это условиене выполняется, то коммутатор 13устанавливается в положение, прикотором на его выходе присутствуетсигнал одного соответствующего разряда. счетчика 7. Перед началом работы сигналом по установочному входу 24 счетчики 1, 2, 7 и триггеры 8 модулей устанавливаются в нулевое состояние.При поступлении запроса за текущим адресом записи, который поступает на первый управляющий вход 5 пер 1244717вого модуля, а также на третий 14 и пятый 18 управляющие входы этого модуля и пятые управляющие входы 18, остальных модулей, к адресным выходам 4 модулей подключаются через открытые по третьимвходам эпементы 3 И-ИЛИ выходные сигналы счетчиков 1. Задним фронтом сигнала на первом управляющем входе 5 первого модуля производится модификация содержимого счетчика 1 и счетчика 7 (добаьляется "1"). Формирование последующих адресов записи для буферной памяти осуществляется аналогично.При поступлении запроса за текущим адресом чтения, который поступает на второй управляющий вход 6 первого модуля, а также на четвертый 15 и шестой 19 управляющие входы этого модуля и шестые управляющие входы 19 остальныйх модулей, к адресным выходам 4 модулей подключаются через открытые по четвертым входам элементы 3 И-ИЛИ выходные сигналы счетчиков 2. Задним фронтом сигнала на втором управляющем входе 6 первого модуля производится модификация содержимого счетчика 2 (добавляется "1") и счетчика 7 (вычитается "1"). Формирование последующих адресов чтения для буферной памяти осуществляется аналогично.Триггеры 8 устанавливаются в единичное состояние сигналами переполнения соответствующих счетчиков 7 и сбрасываются в нулевое состояние сигналами, приходящими на вычитающие входы этих счетчиков.Формула изобретенияФормирователь адресных сигналов для буферной памяти, содержащий первый и второй счетчики, входы которых соответственно являются первым и вторым управляющими входами формирователя адресных сигналов, а их выходысоединены соответственно с первымии вторыми входами элементов И-ИЛИ,выходы которых являются адреснымивыходами формирователя адресных сигналов, третий счетчик и триггер, о тл и ч а ю щ и й с я тем, что,с целью расширения области примененияформирователя адресных сигналов за10 счет увеличения разрядности формируе- .мого адреса, он содержит элемент ИЛИ,первый и второй инверторы с открытыми коллекторными выходами, коммутатори согласующий элемент, входы которогосоединены соответственно с выходамипервого и второго инверторов с открытыми коллекторными выходами и являются первым и вторым управляющими выходами формирователя адресных сигналов,вход первого инвертора с открытымколлекторным выходом соединен черезэлемент ИЛИ с выходами триггера итретьего счетчика, первый и второйвходы которого являются третьим и чет.25 вертым управляющими входами формирователя адресных сигналов, выходытретьего счетчика являются соответственно третьим и четвертым управляющими выходами формирователя адресныхсигналов, причем один выход третьегосчетчика соединен с первым входомтриггера, второй вход которого подключен к другому входу третьегосчетчика, выход триггера соединен35с одним входом коммутатора, другиевходы которОго подключены к соответствующим выходам третьего счетчика,кроме последнего, а выход коммутаторасоединен с входом второго инверторас открытым коллекторным выходом, вы 40ходы первого и второго счетчиковявляются соответственно пятым и шестым управляющими выходами формирователя адресных сигналов, пятым и шес 45тым управляющими входами которого являются соответственно третие и четвертые входы элементов И-ИЛИ.1244717 Составитель В.Гордоноваактор И.Касарда Техред Н.Бонкало Коррект Ч Заказ 392 1303 енно-полиграфическое предприятие, г.ужгород, ул.Проектная,1 роизвод 4 Тираж 543НИИПИ Государственного коми по делам изобретений и от , Москва, И, Раушская П.одпис нота СССРьгтийб., д. 4/5

СмотретьЗаявка

3786860, 01.09.1984

ПРЕДПРИЯТИЕ ПЯ А-3756

ЛУПИКОВ ВИКТОР СЕМЕНОВИЧ

МПК / Метки

МПК: G11C 8/06

Метки: адресных, буферной, памяти, сигналов, формирователь

Опубликовано: 15.07.1986

Код ссылки

<a href="https://patents.su/4-1244717-formirovatel-adresnykh-signalov-dlya-bufernojj-pamyati.html" target="_blank" rel="follow" title="База патентов СССР">Формирователь адресных сигналов для буферной памяти</a>

Предыдущий патент: Преобразователь сигналов для усилителя считывания

Следующий патент: Формирователь уровня считывания

Случайный патент: Способ получения антимонатов трехвалентных металлов