Формирователь выходных сигналов для запоминающего устройства на кмдп-транзисторах

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 767835

Авторы: Баранов, Герасимов, Кармазинский, Савостьянов

Текст

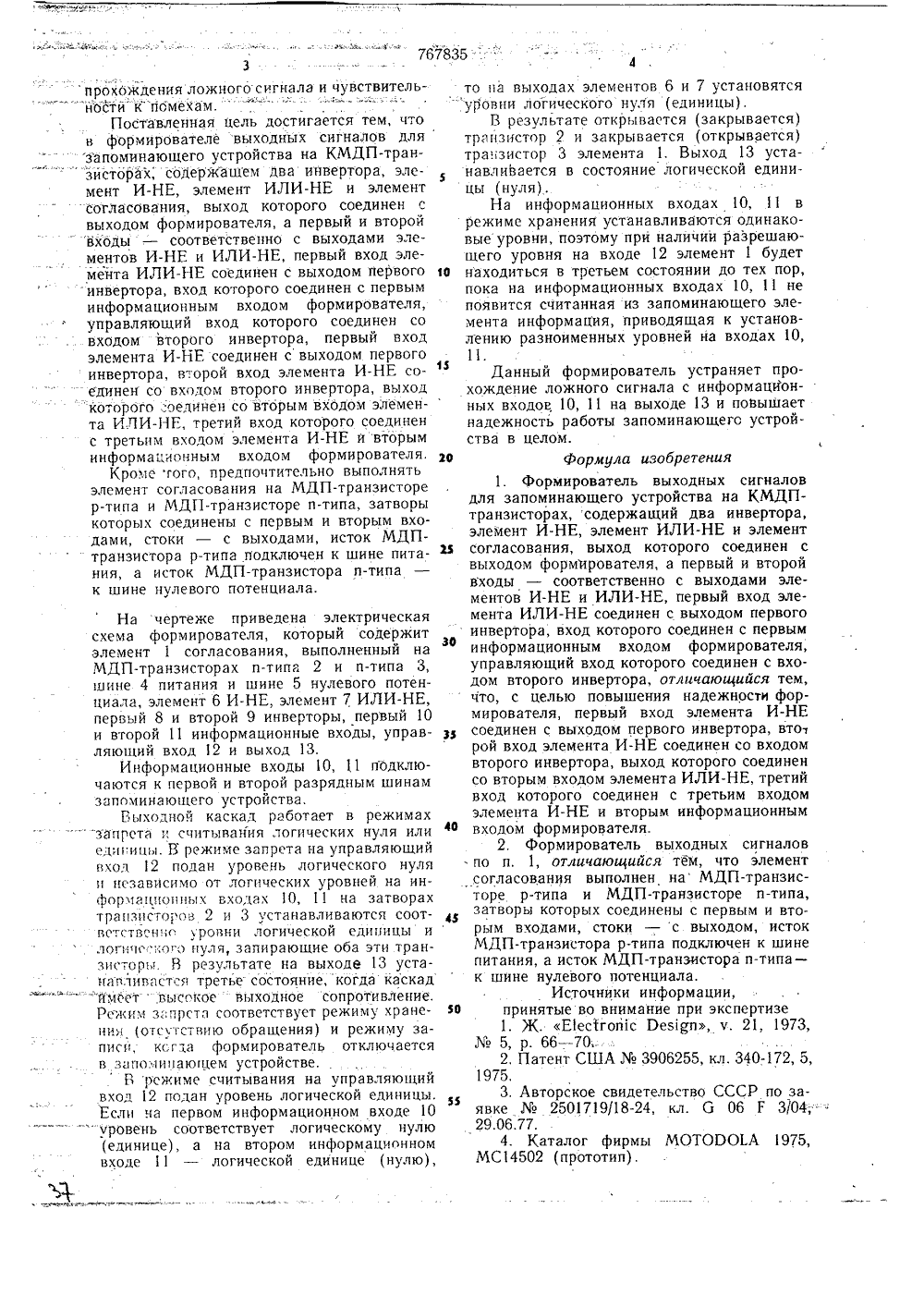

ОП ИСАНИЕ ИЗОБРЕТЕНИЯ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз Советски кСоциалистически кРеспублик 11 767835 Ж(51) М. Кл з б 11 С 7/00 Гаоударстаоиимй комитет СССР ао делам изооретеиий и открытий(54) ФОРМИРОВАТЕЛЬ ВЫХОДНЫХ СИГНАЛОВ ДЛЯ ЗАПОМИНАЮЩЕГО УСТРОЙСТВА НА КМДП-ТРАНЗИСТОРАХ1Изобретение относится к вычислительной технике и может быть использовано при построении микромощныхинтегральных запоминающих устройств на КМДГ 1-транзисторах, имеющих выходы с тремя состояниями.Известны формирователи выходных сигналов для запоминающих устройств на КМДП-транзисторах, содержащие "выходные транзисторы, соединенные с шиной питания, шиной нулевого потенциала и выходами логических элементов управления 1, 2 и 3,Основной недостаток - сложность конструкции,Наиболее близким техническим решением к данному является формирователь выходных сигналов для запоминающего устройства на КМДП-транзисторах, содержащий четыре инвертора, два элемента ИЛИ-НЕ, элемент И-НЕ и элемент согласования, выход которого соединен с выходом формирователя, а первый, второй и третий входы- соответственно с выходами элемента И-НЕ и первого и второго элементов ИЛИ-НЕ, первый вход элемента И-НЕ соединен с выходом первого инвертора и с входом второго инвертора, выход которого соединен с первыми входами элементов ИЛИ-НЕ, второйвход первого элемента ИЛИ-НЕ соединенсо вторым входом элемента И-НЕ и с выходом третьего инвертора, второй вход второго элемента ИЛИ-НЕ соединен с выходомчетвертого инвертора,входы первого; треть-"его и четвертого инверторов соединены с- " соответствующйми информационными и управляющими входами формирователя.Кроме того, элемент согласования выпол 1 о нен на двух последовательно включенныхМДП-транзисторах р-типа и двух параллельно включенных МДП-транзисторах п-типа,образующих выходной каскад с тремя состояниями 4,5Недостаток этого формирователя - возможность прохождения ложных сигналовна выход при подаче управляющих сигналовраньше информационных сигналов, считываемых с разрядной шины запоминающегоустройства, что происходит при выходе из20 режима хранения информации. Кроме того,этот формирователь чувствителен к помехамна разрядных шинах.Цель изобретения - повышение надежности формирователя за счет исключенияпрохождения ложного сигнала и чувствительностй к"помехам.Поставленная цель достигается тем, чтов формирователе выходных сигналов для запоминающего устройства на КМДП-транзисторах, содержащем два инвертора, элемент И-НЕ, элемент ИЛИ-НЕ и элемент согласования, выход которого соединен с выходом формирователя, а первый и второйвходы - соответственно с выходами элементов И-НЕ и ИЛИ-НЕ, первый вход элемента ИЛИ-НЕ соединен с выходом первого инвертора, вход которого соединен с первым информационным входом формирователя, управляющий вход которого соединен со входом второго инвертора, первый вход элемента И-НЕ соединен с выходом первого инвертора, второй вход элемента И-НЕ соединен со входом второго инвертора, выход которого ."оединен со вторым входом элемента ИЛИ-НЕ, третий вход которого соединен с третьим входом элемента И-НЕ и вторым информационным входом формирователя,Кроме гого, предпочтительно выполнятьэлемент согласования на МДП-транзисторе р-тииа и МДП-транзисторе п-типа, затворы которых соединены с первым и вторым входами, стоки - с выходами, исток МДП- транзистора р-типа подключен к шине питания, а исток МДП-транзистора п-типа к шине нулевого потенциала.На чертеже приведена электрическаясхема формирователя, который содержитэлемент 1 согласования, выполненный наМДП-транзисторах п-типа 2 и и-типа 3,шине 4 питания и шине 5 нулевого потенциала, элемент 6 И-НЕ, элемент 7 ИЛИ-НЕ,первый 8 и второй 9 инверторы, первый 10и второй 11 информационные входы, управляющий вход 12 и выход 13,Информационные входы 10, 11 подключаются к первой и второй разрядным шинамзапоминающего устройства,Г ыходной каскад работает в режимах"запрета г считывания логических нуля илиединицы. В режиме запрета на управляющийвход 12 подан уровень логического нуляи независимо от логических уровней на информационных входах 10, 11 на затворахтранзисторов 2 и 3 устанавливаются соответствснг уровни логической единицы илоп ясского нуля, запирающие оба эти.транзисторьн В результате на выходе 13 устанав:1 ивастся третье состояние, когда каскад"ймеет высг кое выходное сопротивление.Режим знпрста соответствует режиму хранения (отсл ствию обращения) и режиму записи, ксг да формирователь отключаетсяв запоминающем устройстве.В режиме считывания на управляющийвход 12 подан уровень логической единицы.Если ча первом информационном входе 10" уровень соответствует логическому нулю(единице), а на втором информационномвходе 11 - логической единице (нулю),Ято на выходах элементов 6 и 7 установятсяуровни логического нуля (единнцы).В результате открывается (закрывается)транзистор 2 и закрывается (открывается)тра зистор 3 элемента 1. Выход 13 устанавливается в состояние логической единицы (нуля),На информационных входах 10, 11 врежиме хранения устанавливаются одинаковые уровни, поэтому при наличии разрешающего уровня на входе 12 элемент 1 будет10 находиться в третьем состоянии до тех пор,пока на информационных входах 10, 11 непоявится считанная из запоминающего элемента информация, приводящая к установлению разноименных уровней на входах 10,11.Данный формирователь устраняет прохождение ложного сигнала с информацИонных входов 10, 11 на выходе 13 и повышаетнадежность работы запоминающего устройства в целом.20 формула изобретения1. формирователь выходных сигналовдля запоминающего устройства на КМДПтранзисторах, содержащий два инвертора,элемент И-НЕ, элемент ИЛИ-НЕ и элементи согласования, выход которого соединен свыходом формирователя, а первый и второйвходы - соответственно с выходами элементов И-НЕ и ИЛИ-НЕ, первый вход элемента ИЛИ-НЕ соединен с выходом первогоинвертора, вход которого соединен с первым0 информационным входом формирователя,управляющий вход которого соединен с входом второго инвертора, отличающийся тем,что, с целью повышения надежности формирователя, первый вход элемента И-НЕсоединен с выходом первого инвертора, второй вход элемента И-НЕ соединен со входомвторого инвертора, выход которого соединенсо вторым входом элемента ИЛИ-НЕ, третийвход которого соединен с третьим входомэлемента И-НЕ и вторым информационным40 входом формирователя.2. Формирователь выходных сигналов- по п, 1, отличающийся тем, что элементсогласования выполнен на МДП-транзисторе р-типа и МДП-транзисторе п-типа,затворы которых соединены с первым и вторым входами, стоки - с выходом, истокМДП-транзистора р-типа подключен к шинепитания, а исток МДП-транэистора и-типа -к шине нулевого потенциала.Источники информации,0 принятые во внимание при экспертизе1. Ж. Еес 1 гоис Рез 1 рп, ч. 21, 1973,5, р.66 - 70:2, Патент США3906255, кл. 340-172, 5,1975.3. Авторское свидетельство СССР по заявке2501719/18-24, кл. б 06 Г 3/04; - .29.06.77.4. Каталог фирмы МОТОРО 1 А 1975,МС 14502 (прототип).го комитета ССС ий и оч крытийаушская наб., д, жгород, ул. Проект

СмотретьЗаявка

2668723, 29.09.1978

ПРЕДПРИЯТИЕ ПЯ Р-6429

БАРАНОВ ВАЛЕРИЙ ВИКТОРОВИЧ, ГЕРАСИМОВ ЮРИЙ МИХАЙЛОВИЧ, КАРМАЗИНСКИЙ АНДРЕЙ НИКОЛАЕВИЧ, САВОСТЬЯНОВ ЭДГАР ПАВЛОВИЧ

МПК / Метки

МПК: G11C 7/10

Метки: выходных, запоминающего, кмдп-транзисторах, сигналов, устройства, формирователь

Опубликовано: 30.09.1980

Код ссылки

<a href="https://patents.su/3-767835-formirovatel-vykhodnykh-signalov-dlya-zapominayushhego-ustrojjstva-na-kmdp-tranzistorakh.html" target="_blank" rel="follow" title="База патентов СССР">Формирователь выходных сигналов для запоминающего устройства на кмдп-транзисторах</a>

Предыдущий патент: Устройство для считывания информации из матричного накопителя

Следующий патент: Буферное запоминающее устройство

Случайный патент: Устройство для измерения частоты