Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

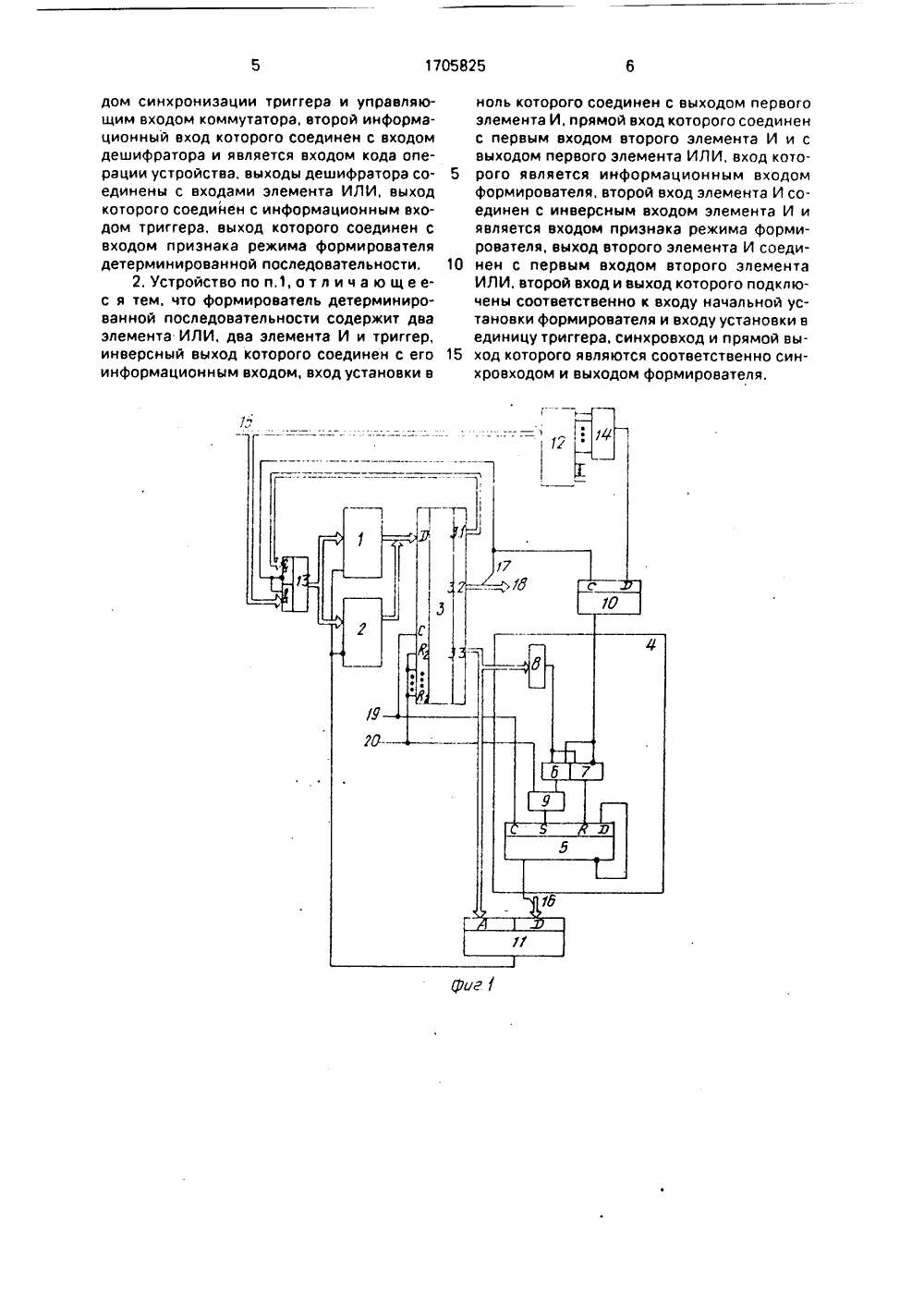

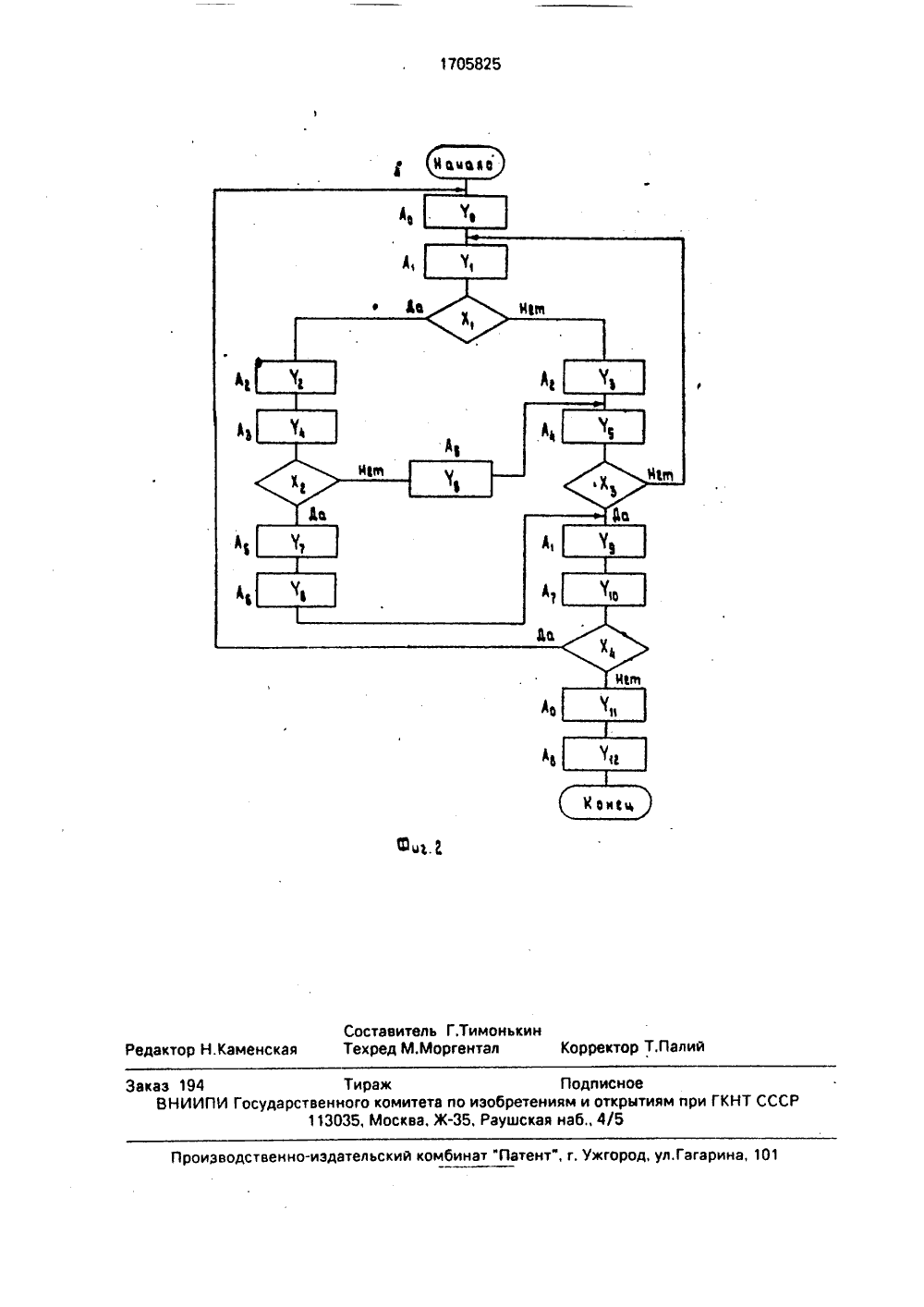

(51)э 6 0 САНИЕ ИЗОБРЕТЕНИЯ Изобретение ной технике и авт пользовано в управления спец тельных систем,Целью изобр ние коэффициент памяти микроко размещения ми первом и втором тносится к вычислительматике и может быть искачестве устройства ализированных вычислиетения является увеличеа использования емкости манд путем равномерного крокомандного базиса в блоках памяти. ОСУДАРСТВЕ ННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГКНТ СССР АВТОРСКОМУ СВИДЕТЕЛЬСТВ(71) Конструкторское бюро электроприборостроения(56) Авторское свидетельство СССР М 964640, кл. 6 06 Р 9/22, 1982.Авторское свидетельство СССР М 1399738, кл. 6 06 Г 9/22, 1988. .(54) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ Сущность изобретения состоит в равномерном распределении микрокомандного базиса в блоках памяти микропрограммного устройства управления, Это достигается за счет разделения множества микропрограмм на два подмножества. При реализации микропрограмм первого подмножества триггер формирователя после выполнения микрокоманд ветвления устанавливается в нулевое состояние, а при реализации мик(57) Изобретение относится к вычислительной технике и автоматике и может быть использовано в качестве устройства управления специализированных вычислительных систем, Целью изобретения является увеличение коэффициента использования емкости памяти микрокоманд. Для этого микропрограммное устройство управления содержит первый и второй блоки 1, 2 памяти, регистр 3 микрокоманд, формирователь 4 детерминированной последовательности, триггер 10, мультиплексор 11 дешифратор 12. коммутатор 13 и элемент ИЛИ 14. Цель достигается введением дешифратора, элемента ИЛИ, триггера, коммутатора и обусловленных ими связей. 1 з.п, ф-лы, 2 ил. рокоманд второго подмножества - в единичное состояние.На фиг.1 приведена функциональная схема микропрограммного устройства управления; на фиг,2 - пример алгоритма.Микропрограммное устройство управления содержит первый и второй блоки 1, 2 памяти, регистр 3 микрокоманд с выходами Со 3,1 адреса очередной микрокоманды, выхо- Я дом 3.2 микроопераций, выходом 3.3 кода (Л проверяемого условия, формирователь 4 детерминированной последовательности, состоящей из триггера 5, элементов И 6 и 7, элементов ИЛИ 8, 9, триггер 10, мультиплексор 11, дешифратор 12, коммутатор 13. элемент ИЛИ 14, вход 15 кода операции, вход 16 сигналов логических условий, выход 17 сигнала микрооперации "Конец команды", выход 18 микроопераций устройства, вход 19 синхронизации устройства, вход 20 начальной установки, 1705825Микропрограммное устройство управления функционирует следующим образом.Перед началом работы по сигналу начальной установки со входа 20 регистр 3 устанавливается в начальное состояние, все триггеры регистра 3 устанавливаются в нулевое состояние за исключением триггера, формирующего сигнал "Конец команд" на, выход 17, который устанавливается в единичное состояние, триггер 5 устанавливается в единичное состояние, Сигнал с выхода триггера 5 через мультиплексор 11 поступает на блоки 1, 2 памяти и открывает блок 1 памяти, Код операции (адрес первой микро- команды соответствующей микропрограммы) со входа 15 устройства поступает на дешифратор 12 и через коммутатор 13 - на адресные входы блоков 1, 2 памяти, При этом из блока 1 памяти выбирается микро- команда и поступает на 0-вход регистра 3 микрокоманд. По заднемуфронту импульса, поступающего со входа 20 устройства, микрокоманда записывается в регистр 3, единичный сигнал на выходе 17 при этом исчезает, а триггер 5 переводится в нулевое состояние, Если выполняемая микропрограмма принадлежит к первому множеству, то на соответствующем выходе дешифратора 12 появляется сигнал, Этот сигнал с выхода элемента ИЛИ,14 поступает на О-вход триггера 10. По заднему фронту сигнала с выхода 17 триггер 10 устанавливается в единичное состоя ние.Сигналы микроопераций с выхода 3.2 регистра 3 поступают на выходы 18 устройства, код адреса очередной микрокоманды с выхода 3.1 через коммутатор 13 поступает на адресные входы блоков 1,2 памяти, код проверяемого логического условия с выхода 3.3. блока 3 поступает на элемент ИЛИ 8 и на адресный вход мультиплексора 11. Сигнал на выходе мультиплексора 11 отсутствует, поэтому очередная микрокоманда будет выбираться из блока 2 памяти. По заднему фронту очередного синхроимпульса эта микрокоманда записывается в регистр 3 и триггер 5 переводится в противоположное состояние. Очередная микрокоманда, аналогично описанному выше алгоритму, будет выбираться из блока 1 памяти. Далее устройство будет функционировать аналогично описанному выше алгоритму, Если очередная микрокоманда является микрокомандой ветвления, то на выходе 3,3. будет присутствовать ненулевой код. При этом сигналом с выхода элемента И 6 триггер 5 переводится в единичное состояние, Сигнал проверяемого условия со входа 16 через мультиплексор 11 поступает на блоки 1, 2 памяти, В зависимости от значения этого 5 10 20 25 30 35 40 45 50 55 сигнала очередная микрокоманда будет выбираться либо иэ блока 1 памяти (при единичном значении сигнала), либо из блока 2памяти (при нулевом значении сигнала).При выборке этой микрокоманды изблоков Ц 2) памяти триггер 5 перейдет в нулевое состояние. Очередная микрокомандапри этом будет выбираться из блока 2 памяти,Если же выполняемая микропрограммапринадлежит ко второму множеству, то перед ее выполнением на выходах дешифратора 12 сигналы будут отсутствовать и навыходе элемента ИЛИ 14 будет нулевой сигнал,При записи в регистр 3 первой микрокоманды микропрограммы триггера 10 установливается в нулевое состояние. Привыполнении линейных микрокоманд устройство функционирует аналогично описанному выше алгоритму, Если в регистрзаписывается микрокоманда ветвления, тов процессе ее выполнения триггер 5 устанавливается в нулевое состояние. Микрокоманда, следующая после микрокомандыветвления, выбирается либо из блока 1 памяти (при единичном значении проверяемого логического условия), либо из блока 2памяти(при нулевом значении проверяемо.го логического условия), а очередная линейная микрокомандэ будет выбираться из блока1 памяти, Далее устройство функционируеттак, как и при выполнении микрокоманд микропрограмм первого подмножества,Таким образом, при выполнении микро-упрограмм первого подмножества микрокоманды, следующие после микрокомандветвления, выбираются из блока 2 памяти,При выполнении микропрограмм второгоподмножества микрокоманды, следующиепосле микрокоманд ветвления, выбираютсяиз блока 1 памяти, Реализация такого подхода позволяет на этапе проектированиямикрокомандный базис равномерно размещать в первом и втором блоках 1, 2 памяти,уменьшать их информационную емкость исложность устройства в целом, т.е, увеличивать коэффициент использования емкостипамяти микрокоманд,Формула изобретения1. Микропрограммное устройство управления по авт.св. М 1399738, о т л и ч а ющ е е с я тем, что, с целью увеличения коэффициента использования емкости памятимикрокоманд, оно дополнительно содержитдешифратор, элемент ИЛИ, триггер и ком- .мутатор, первый информационный вход которого соединен с первым выходомрегистра, выход сигнала микрооперациидом синхронизации триггера и управляющим входом коммутатора, второй информационный вход которого соединен с входом дешифратора и является входом кода операции устройства. выходы дешифратора соединены с входами элемента ИЛИ, выход которого соединен с информационным входом триггера, выход которого соединен с входом признака режима формирователя детерминированной последовательности.2. Устройство по п,1,отл ич а ю щеес я тем. что формирователь детерминированной последовательности содержит два элемента ИЛИ, два элемента И и триггер, инверсный выход которого соединен с его информационным входом, вход установки в ноль которого соединен с выходом первого элемента И, прямой вход которого соединен с первым входом второго элемента И и с выходом первого элемента ИЛИ, вход кото рого является информационным входомформирователя, второй вход элемента И соединен с инверсным входом элемента И и является входом признака режима формирователя, выход второго элемента И соеди нен с первым входом второго элементаИЛИ, второй вход и выход которого подключены соответственно к входу начальной установки формирователя и входу установки в единицу триггера, синхровход и прямой вы ход которого являются соответственно синхровходом и выходом формирователя,1705825 Т.Пал едактор Н.Каменска зводственно-издательский комбинат "Патент", г, Ужгород, ул.Гагарин аказ 194 ВНИИПИ Госуд Составител Техред М.М Тиражвенного комитета113035, Москва. Ж.Тимонькингентал Корректо Подписноеизобретениям и открытиям при ГКНТ ССС

СмотретьЗаявка

4807175, 05.02.1990

КОНСТРУКТОРСКОЕ БЮРО ЭЛЕКТРОПРИБОРОСТРОЕНИЯ

БАЙДА НИКОЛАЙ КОНСТАНТИНОВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, БЛАГОДАРНЫЙ НИКОЛАЙ ПЕТРОВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, СКАПЕНКО АЛЕКСАНДР ВАСИЛЬЕВИЧ, СЕРЕДА ВАЛЕРИЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 15.01.1992

Код ссылки

<a href="https://patents.su/4-1705825-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Устройство суммирования частот

Следующий патент: Устройство приоритета

Случайный патент: Способ управления трехфазным мостовым вентильным преобразователем частоты