Преобразователь двоичного кода смешанных чисел в двоично десятичный код

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

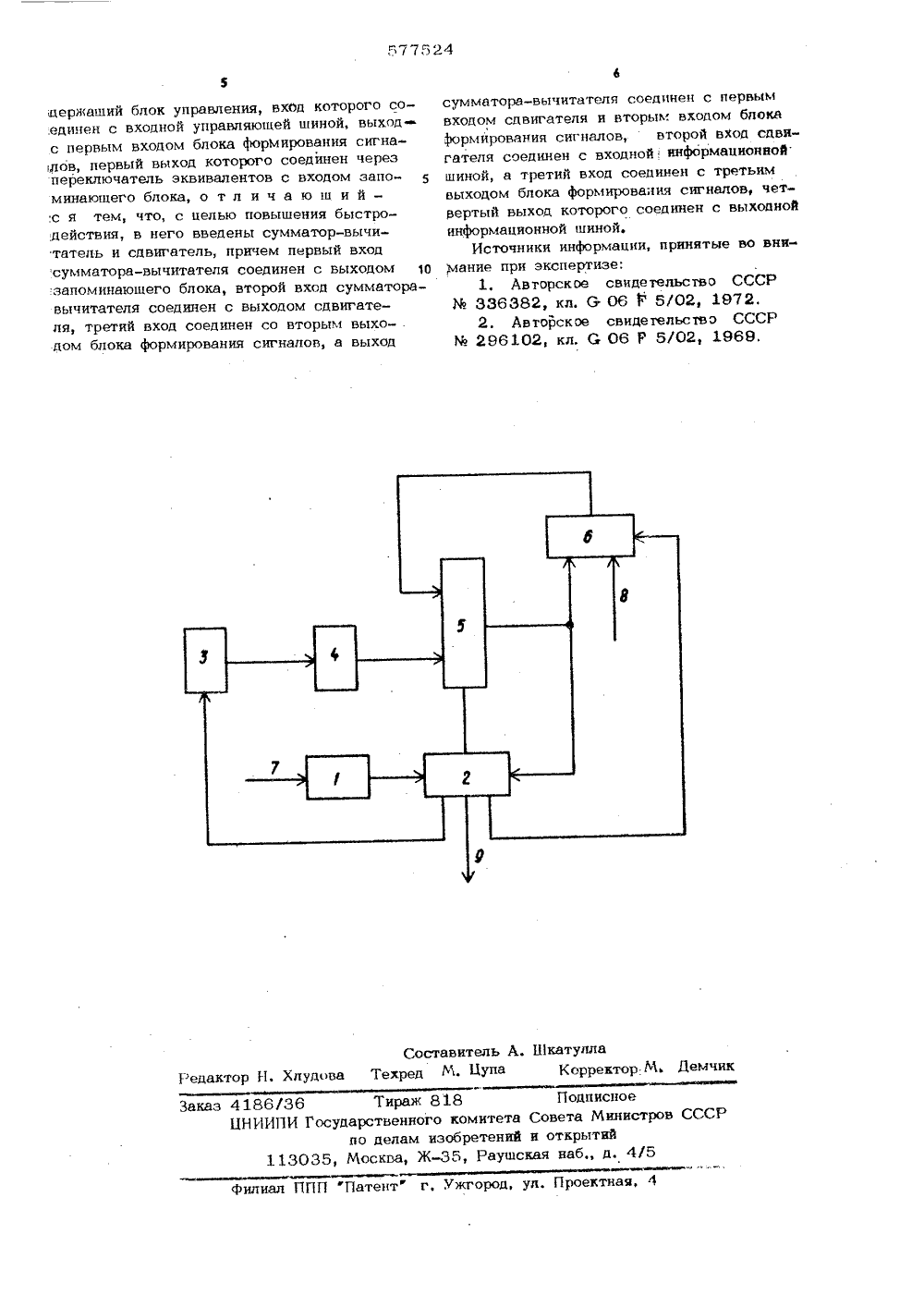

ОП ИСАНИЕизоваетения К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз Советских Социалистиыеских Республик)М. Кл, Ст 06 Р 5 соединением аявкиГооудвр Совета по дел еиныи комите иистров СССР иэооретеиийкрытий 23) Приорит ОпубликованБюллетень Мбст сания 1011.77(45) Дата опубликования опи 72) Авторы изобретен В,виВ,В клин 1) Заявит) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО 110 ДА СМЕШАННЬ ЧИСЕЛ В ДВОИЧНО-ДЕСЯТИЧНЫЙ КОД нреобраэоатель исумматоразапоминаючто вается те 1 сулима разователей дятичный наибол шности к заяь ватель введесдвигатель, и1 вычитателя с1 шего блока,ричем пединен выходо вход сумматора-вычи гаИзобретение относится к области вычислигельной техники и автоматики и может быть использовано в специализированных арифметических и логических устройствах, оперирующих в двоичной системе счисления и выдающих результат обработки информации для восприятия в десятичной системе.Известен преобразователь кодов 1 из двоично-десятичной системы счисления в двоичную, содержащий блок управления, переклю чатель экивалентов, запоминающее устрой 1ство двоичных эквивалентов, распределитель двоичных разрядов по весам, регистр числа, одноразрядный двоичный сумматор, регистр результата ) 1, Быстродействие 15 этого преобразователя недостаточно высоко и зависит от числа двоичных разрядов Гт;преобразование к, - разрядного десятичного числа длится в течение времени 4 К 1 тт где-длительность одного такта пре образования.Из известных преоб воичного кода в двоично-дес ее близким по технической су ченному является преобразователь двоичного кода 25 смешанных чисел в двоично-десятичный код,содержащий блок управления, вход кототтотсоединен с входной управляюгцей шиной,1 выход - с первым входом блока формирования:игналов, первый выход которого соединенчерез переключатель эквивалентов с входомзапоминающего блока 2 . Схема этогопреобразователя весьма проста, а переводдвоичного кода смешанных чисел в двоичнодесятичный код осуществляется беспрограммным путем с использованием двоичныхэквивалентов десятичных чисел вида (1 д )где )( -0,1,2,3Однако быстродействие данного преобразователя также зависитот числа двоичных разрядов тт, а времяперевода достигает значения 9 Ц тт 1 .Целью изобретения является повышениебыстродействия преобразования двоичногокода смешанных чисел в двоично-десятичныйход, 577524теля соединен с выходом сдвтателя, третий вход соединен со вторым выходом блокаформирования сигналов, а выход сумматоравычитатепя соединен с первым входом сдвигателя и вторым входом блока формирования 5сигналов второй вход сдвигателя соединенс входной информационной шиной, а третийвход соединен с третьим выходом блокаформирования сигналов, четвертый выход которого соединен с выходной информационнойшиной,На чертеже представлена структурнаясхема преобразователя двоичного кода слешвнных чисел в двоично-десятичный код,Преобразователь двоичного кода смешенных чисел в двоично-десятичный код содержит блок управления 1, блок 2 формпрования сигналов, переключатель эквивалентов 3, запоминающий блок 4 сумматор-вычитатель 5, сдвигатель 6, входную управляюшую "шину 7, входную инфорллационнуюшину 8, выходную информационнуо шину 9,Преобразование осуществляется последовательным нахождением тетрад лвоично-десятичного кола смешанных чисел, начиная со 25старшей тетрвлы, методом деления обрабатываемого двоичного параллельного кода безвосстановления остатка на двоичные, эквиваленты десятичных чисел вида (10 2 ),где С - число лесятичных разрядов пе 30лой части переводимого числа; Ю=1,2,3,(к -1), ), 1 - обшее число десятичныхразрядов переводимого числа.Преобразователь работает следуюшим образом, Управляюций импульс, поступаюший по шине 7, запускает блок управления1,. который вырабатывает импульсы, необходимые лля автономного функционированияпреобразователя, и пересылает их в блок 2формирования сигналов. Сигнал с выходаблока 2 переводит переключатель эквивалентов 3 на считывание из запоминающего блока 4 соответствуюцего эквивалента десятичных чисел (в начале преобразования -старшего, то есть при И=1), двоичный параллельный код которого йоступает на входсумматора-вычитателя 5 и служит при на -хождении данной тетрады делителем. Одновременно на другой вход сумматоравычита 10теля 5 в первом такте - преобразования подается через сдвигатель 6, управляемый блоком 2, двоичный параллельный код входнойинформации, который берется делимым (вдальнейшем,1 делимым является предыдушийостаток). Блок 2 разрешает в первом тактепреобразования вычитание делителя из делимого в сумматоре-вычитателе 5, откуда навход ;сдвигателя 6 поступает код полученного частичного остатка, знаковый разрядкоторого поступает также в блок 2 для фор мирования кода двоично-десятичной тетрадыи определения необходимости вычитания илисложения в следуннцем такте преобразования, При этом, если по анализу знаковогоразряда сумматора-вычитателя 5 частичныйостаток оказался отрицательным, то блок2 выдает на выходную информационную шину9 в виде очередной цифг, цвоично-десятичной тетрады-нуль и долг отввпивает в сумматоре-вычитателе 5 цепи сложения дляслелуюшего такта преобразования, а есличастичный остаток получился положительным, то на выходную информационну: шину9 вылается единица, а в слелую 1 цел тактепроизводится вычитание делителя из делимого. В следуюшпх тактах определенияданной двои шо-десятичной тетрады делимое, т. е, прелылуший частичный остаток,передается через сдвигатель 6 на вход сумматора-вычитателя 5 со сдвиголл кода наолин двоичный разояд в сторону старших разрядов, делитель остается прежним, Посленахожления всех цифр лвоично-десятичнойтетрады, т, е. выполнения четырех тактов,в случае отрицательного остатка производится восстановление положительного остатка в дополнительном такте путем прибавления в сумматоре-вычитателе 5 того жеделителя к отрицательному остатку, Длянахождения последуюших двоично-десятичных тетрад переключатель эквивалентов Эпереводится под возлействием сигналов блока2 на выборку из запоминвюшего блока 4следующих по-порядку (меньших по величине) эквивалентов, которые берутся новымиделителями, в качестве лелимых берутсяпредыдушие положительные остатки и выполняется порядок вышеописанных действийопределения кода каждой тетрады. Процесспреобразования будет повторяться до техпор, пока не будут найдены все десятичныеразряды числа,В описываемом преобразователе время перевода смешанных чисел из двоичного в двоично-десятичный код уменьшается до значения5 )1 не зависит от разрядности двоичного кода обрабатываемых чисел, что значительно повышает его быстродействие. Приэтом применение схемы предлагаемого преобразователя в арифметических и логическихустройствах специализированных цифровыхвычислительных машин позволяет использовать его узлы при выполнении других операций;формула изобретенияПреобразователь лвоичного кода смешанных чисел в лвоично-десятичный код, со577524 Составитель А. ШкатуллаРедактор Н, Хлудова Техред М. Цупа Корректор М Демчик Заказ 4186/36 Тираж 818 Подписное ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская набд, 4/5Филиал ППП "Патент" г, Ужгород, ул. Проектная, 4 цержаший блок управления, вход которого соединен с входной управляющей шиной, выходс первым входом блока формирования сигна,лов, первый выход которого соединен черезпереключатель эквивалентов с входом запоминаюшего блока, о т л и ч а ю ш и й -,с я тем что, с целью повышения быстродействия, в него введены сумматор-вычитатель и сдвигатель, причем первый входсумматора-вычитателя соединен с выходом 10запоминаюпего блока, второй вход сумматоравычитателя соединен с выходом сдвигателя, третий вход соединен со вторым выхо- .дом блока формирования сигналов, а выход сумматора-вычитателя соединен с первым входом сдвигателя и вторым входом блока формирования сигналов, второй вход сдвиГателя соединен с входнойинформационной шиной, а третий вход соединен с третьим выходом блока формирования сигналов, четВертый выход которого соединен с выходной информационной шиной,Источники информации, принятые во вниМание при экспертизе:1, Авторское свидетельство СССР Мф 336382, кл. О 065/02, 1972.2. Ав торск се свидетельство СССР % 296102, кл, С 06 Р 5/02, 1969.

СмотретьЗаявка

2096546, 09.01.1975

ПРЕДПРИЯТИЕ ПЯ А-1178

РОЗОВ ВИКТОР НИКОЛАЕВИЧ, ЧЕКЛИН ВЛАДИМИР ВАСИЛЬЕВИЧ

МПК / Метки

МПК: G06F 5/02

Метки: двоично, двоичного, десятичный, код, кода, смешанных, чисел

Опубликовано: 25.10.1977

Код ссылки

<a href="https://patents.su/3-577524-preobrazovatel-dvoichnogo-koda-smeshannykh-chisel-v-dvoichno-desyatichnyjj-kod.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь двоичного кода смешанных чисел в двоично десятичный код</a>

Предыдущий патент: Устройство для ввода-вывода информации

Следующий патент: Логическая ячейка

Случайный патент: Устройство очистки дробильных валов текстильных машин