Микропрограммное устройство управления с контролем

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

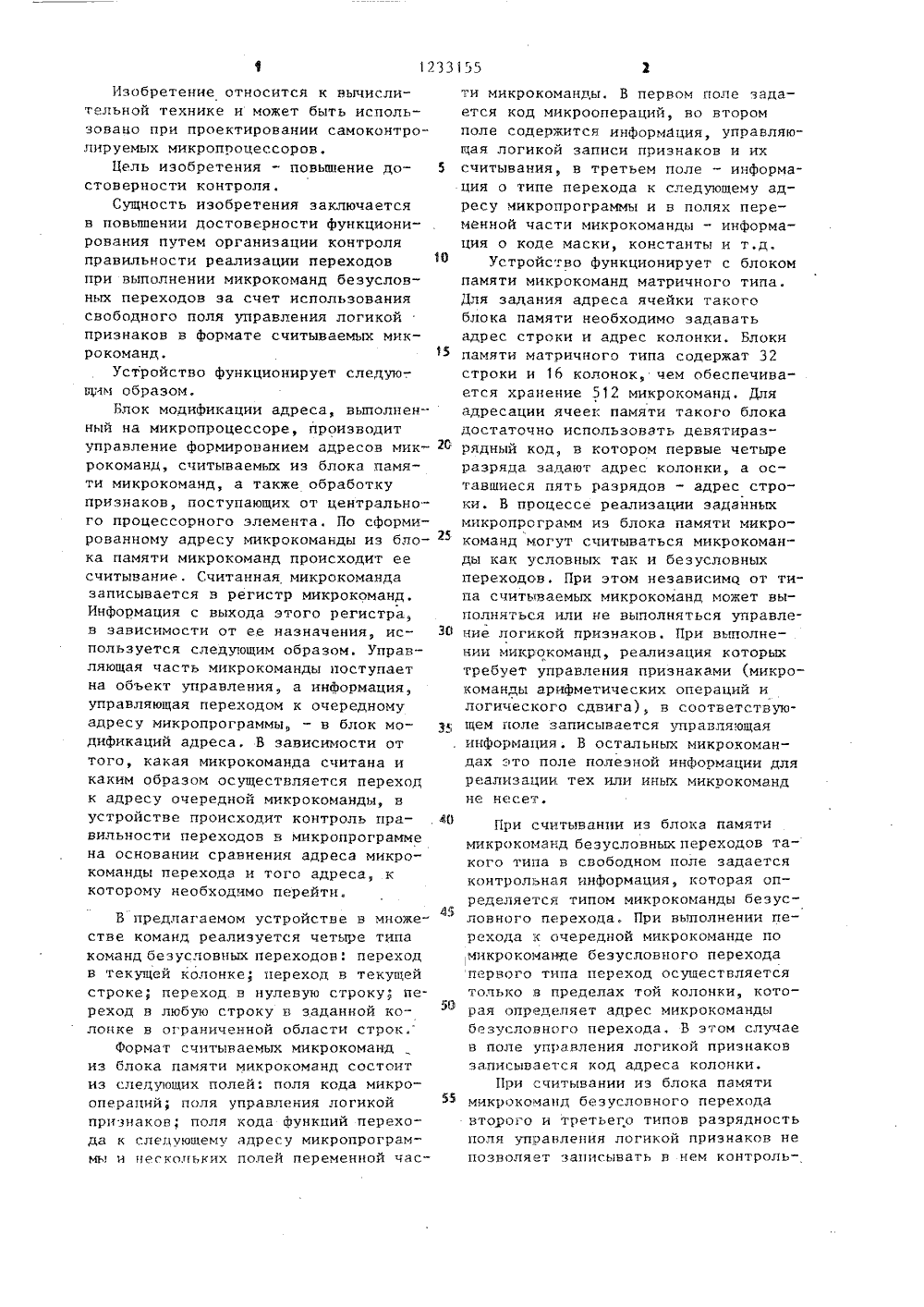

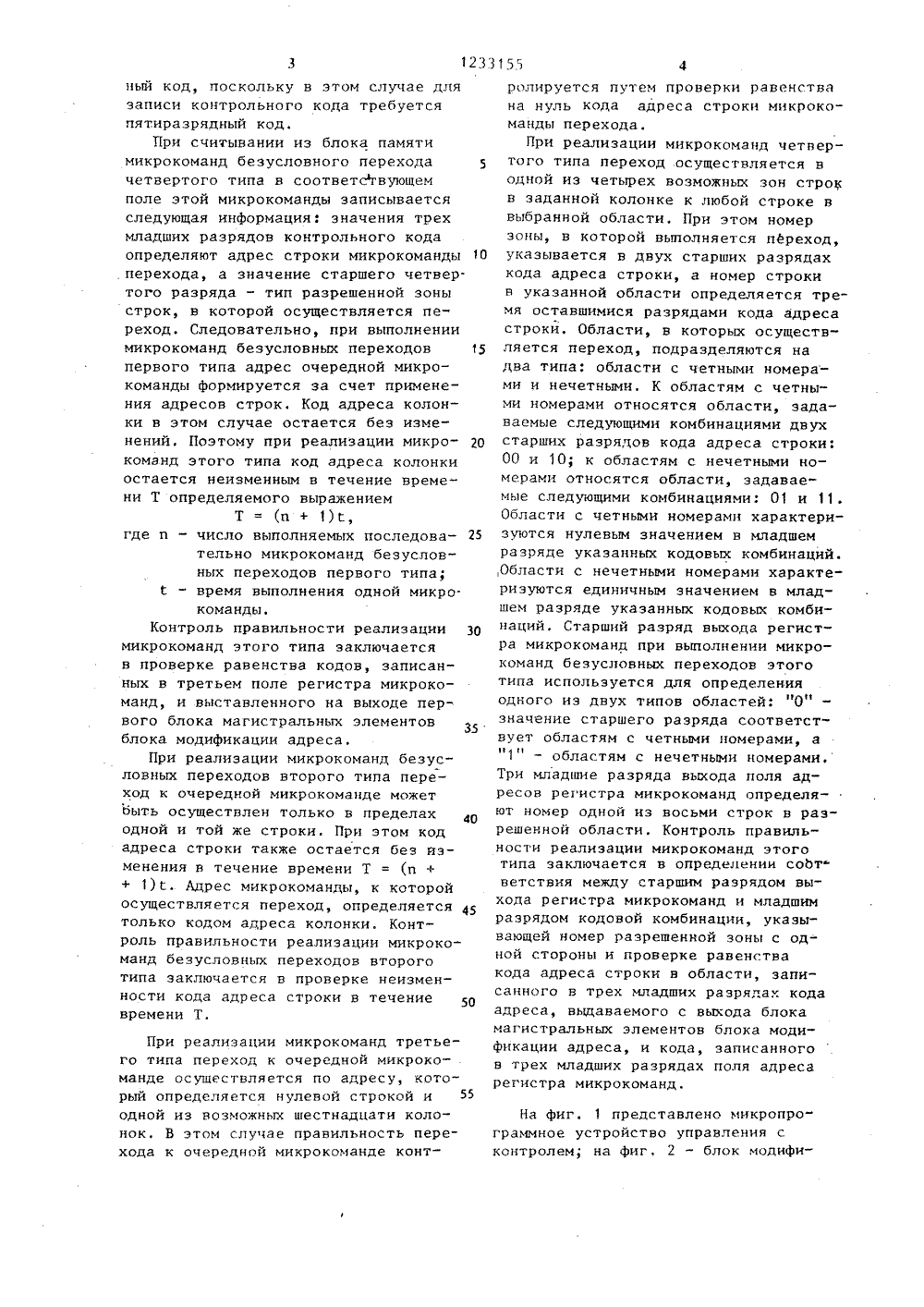

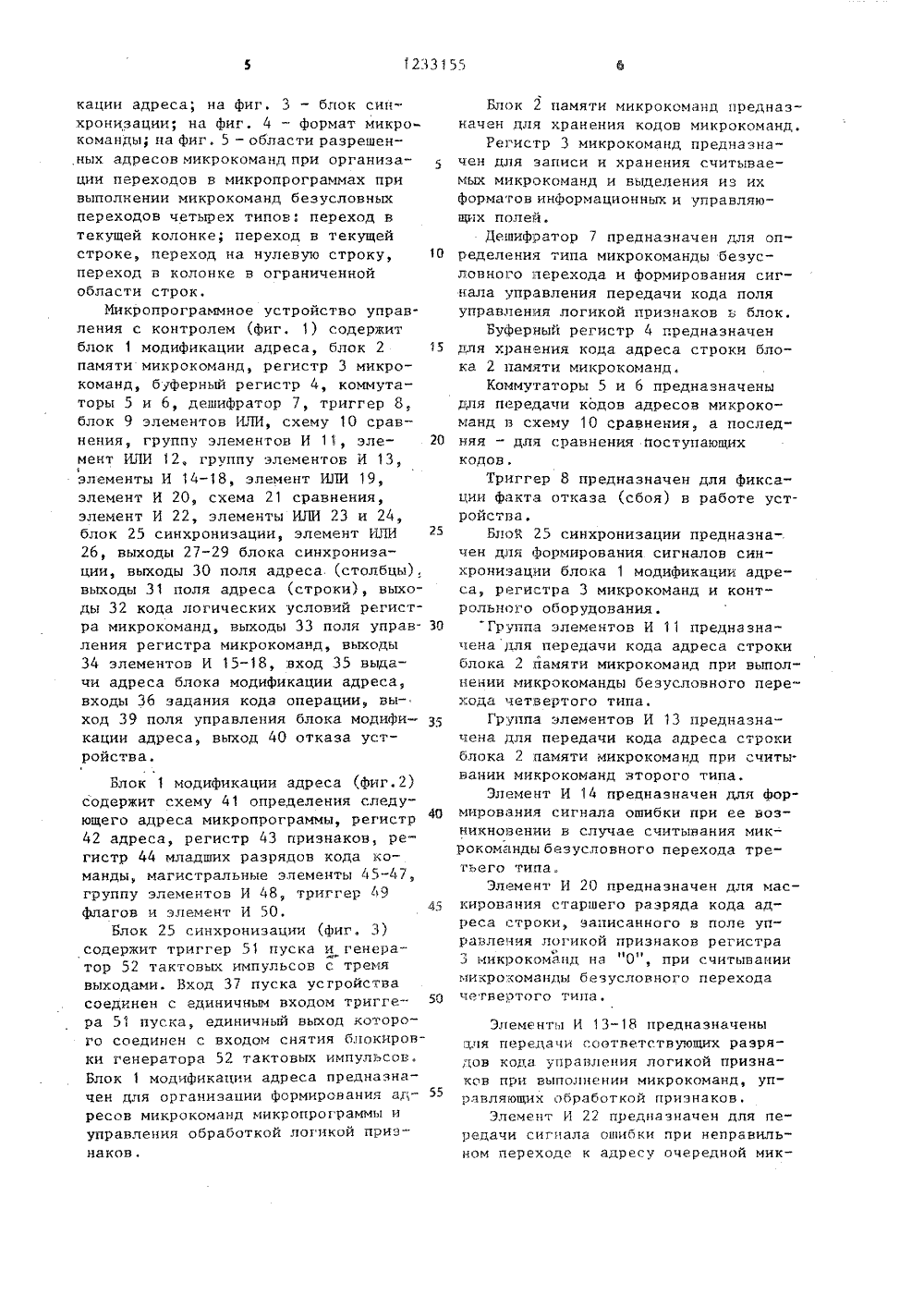

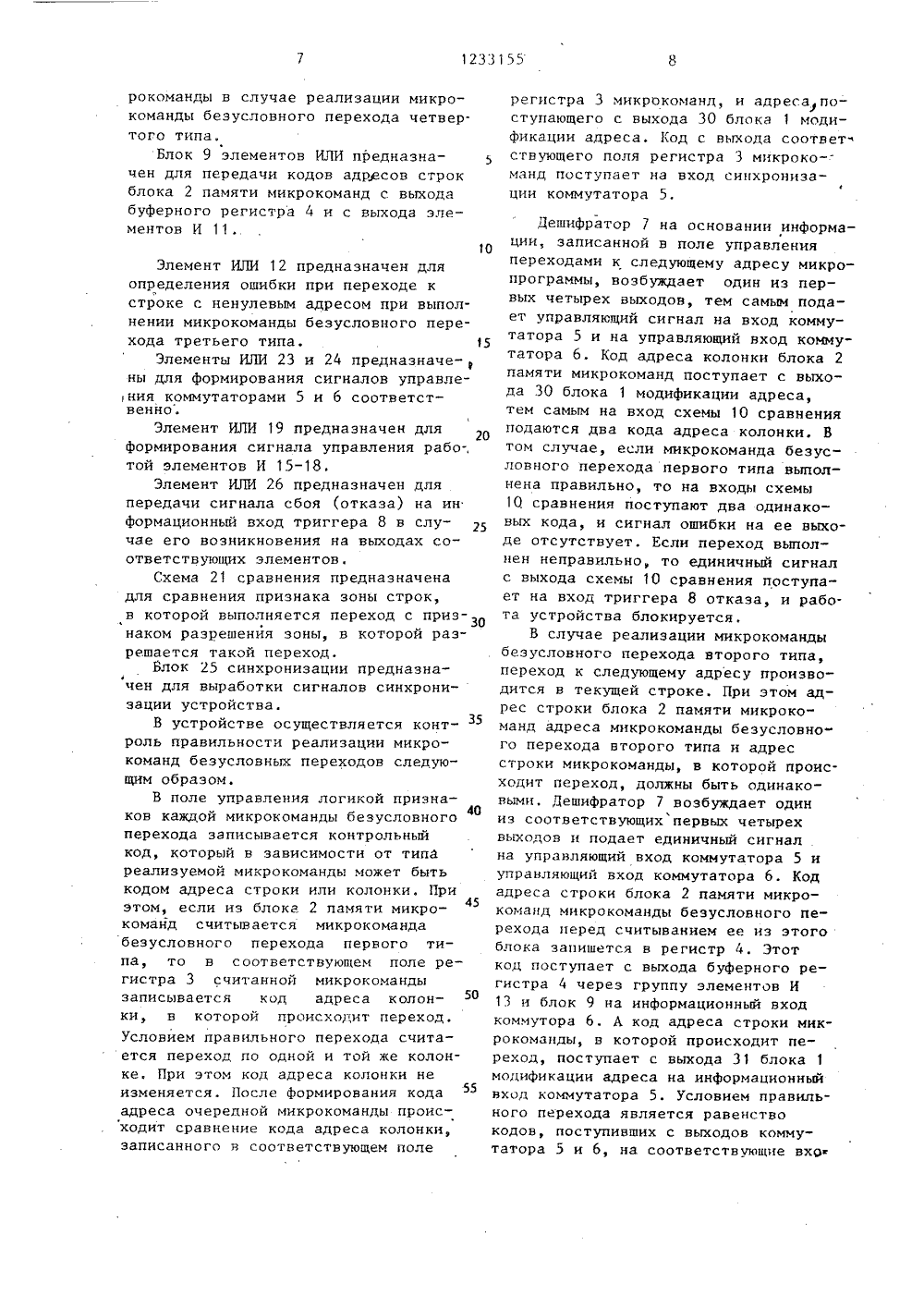

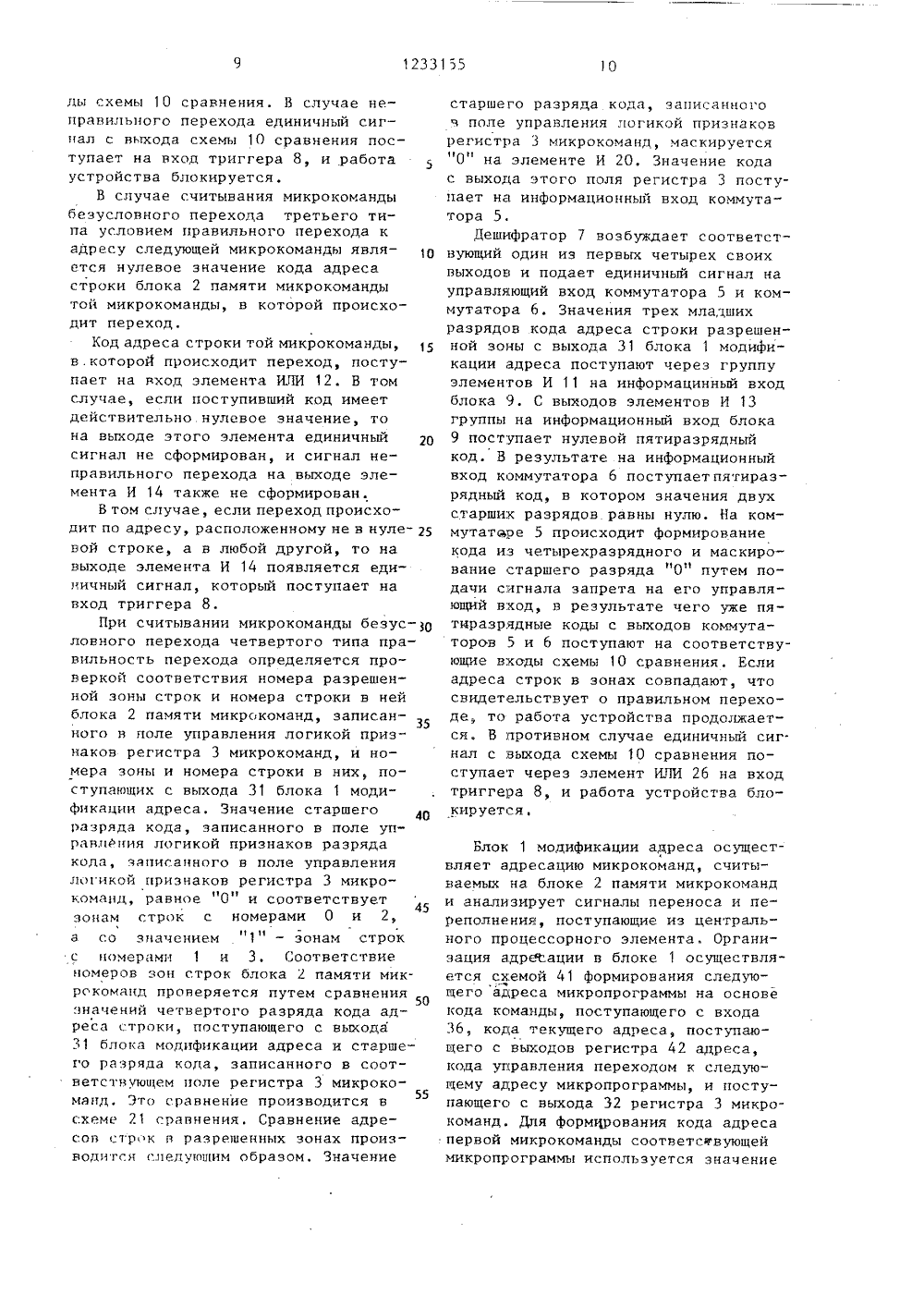

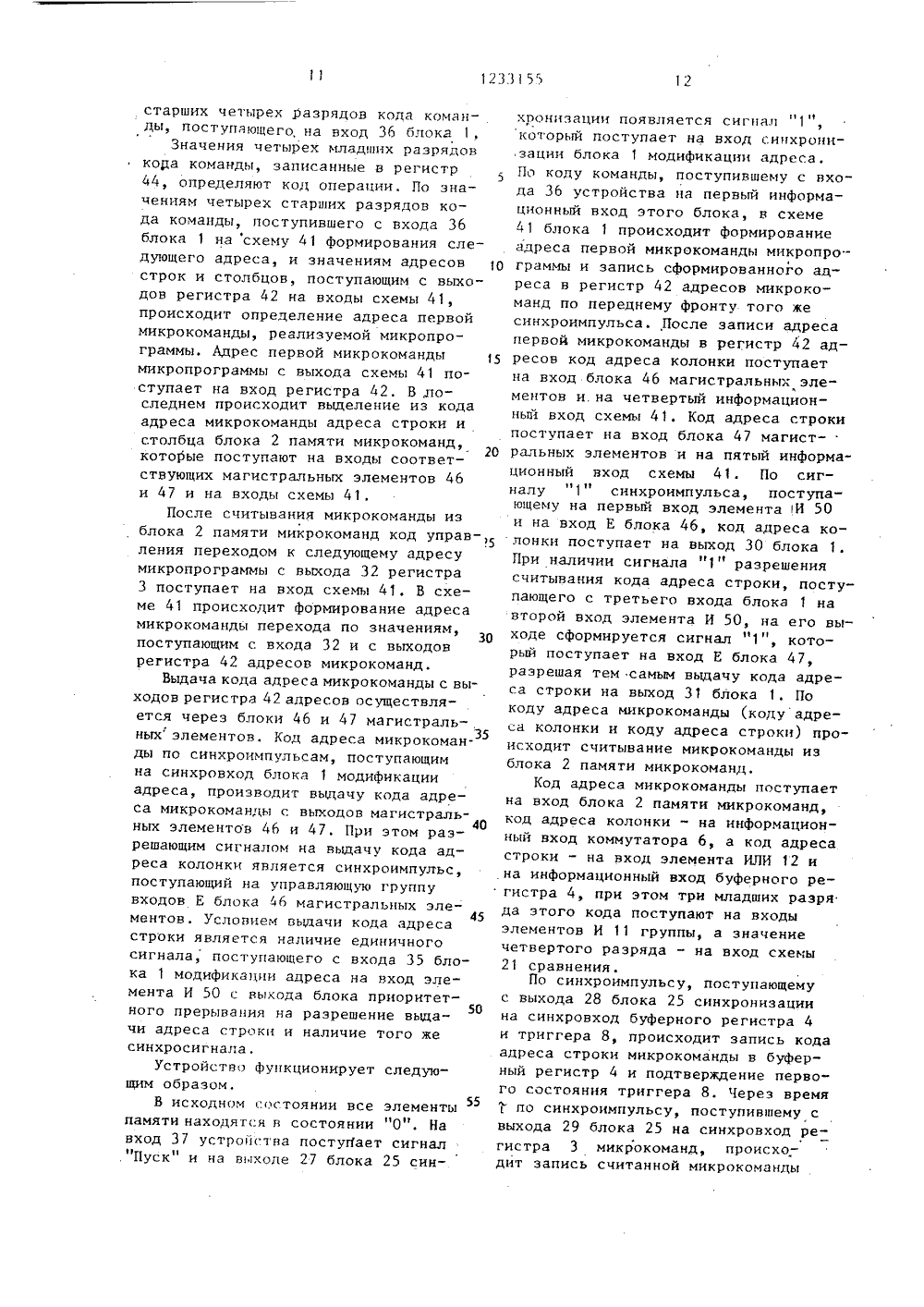

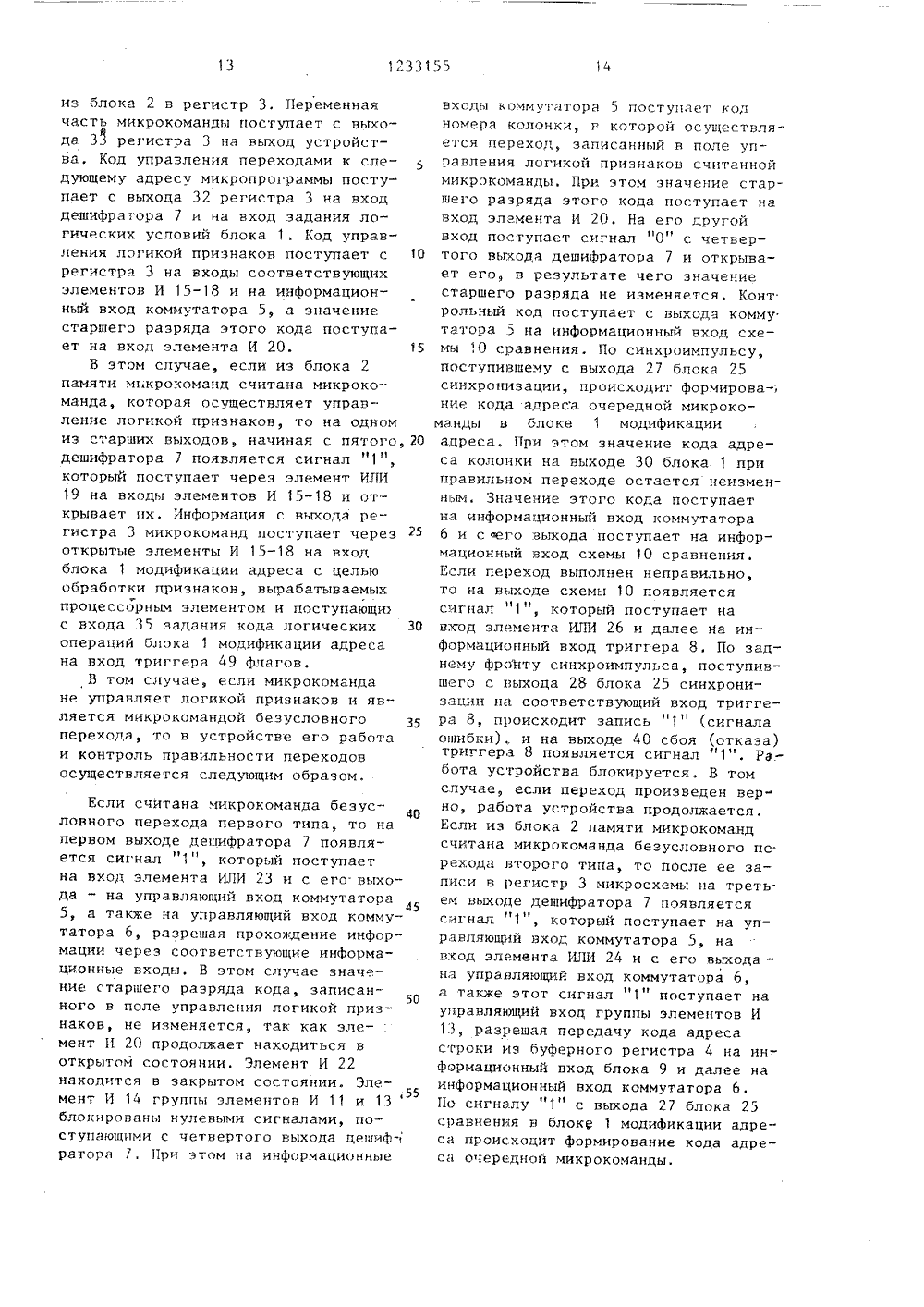

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСНРЕСПУБЛИН 19) 11 А 1) 4 С 06 Р 9/22, 11/00 ОПИСАНИЕ ИЗОБРЕТЕНИ ВТО Ъ( СВИДЕТЕЛЬСТВУ ТВО УПвтомаи моВ.С,Хаельство СССР Р 15/00, 198 Авторское сви 07109, кл. С ГОСУДАРСТВЕННЫЙ КОМИТЕТ СПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТ(57) Изобретечие относитсятике и вычислительной техни жет быть использовано при контроле процессоров, Цель изобретения - повышение достоверности контроля. Устройство содержит блок модификации адреса, выполненный на микропроцессоре, два коммутатора, сумматор, триггер, группу элементов И, блок синхронизации, две схемы сравнения. Это позволяет повысить достоверность функционирования путем органиэации контроля правильности реализации переходов при выполнении микро- -ф команд безусловных переходов за счет использования свободного поля управления логикой признаков в форма те считываемых микрокоманд. 5 ил, 1233 155ходе открытого по входу сигналом с четвертого выхода дешифратора 7 эле - мента И 22 устанавливается сигнал "1", который поступает на вход элемента ИЛИ 26. Если на выходе схемы 10 сравнения устанавливается сигнал "1", то он поступает на вход элемента ИЛИ 2 б. Сигнал "1" с выхода этого элемента поступает на информационный вход триггера 8, Однако триггер 8 в состояние "1" не переходит, поскольку синхросигнал на выходе блока 25 синхронизации отсутствует. По синхроимпульсу, поступившему с выхода 27 блока 25 синхронизации на вход блока 1 модификации адреса, на его информационных выходах устанавливается код адреса микрокоманды перехода. До появления синхроимпульса на выходе 28 блока 25 синхронизации в устройстве происходит контроль правильности перехода к новому адресу по описанному способу. При этом, если адрес строки соответствует адресу 25 строки, записанному в трех младших разрядах поляуправления логикой признаков, а номер разрешенной зоны не соответствует значению старшего разряда, этого кода или, наоборот, номер разрешенной зоны соответствует, а адрес строки в зоне не совпадает с требуемым его значением, то на выходах схемы 10 сравнения или элемента И 22, соответственно, устанавлива 5 ется сигнал "1", который через элемент ИЛИ 2 б поступает на информационный вход триггера 8.По заднему фронту синхроимпульса, поступившего с выхода 28 блока 25, триггер 8 переходит в состояние "1", и на выходе 40 устройства устанавливается сигнал "1" сбоя (отказа). В том случае, если переход к очередной45 микрокоманде происходит правильно, работа устройства продолжается.Формула изобретения50Микропрограммное устройство управ.ления с контролем, содержащее блок памяти микрокоманд, блок синхронизации, буферный регистр, регистр микро- команд, первый и второй коммутаторы, дешифратор, триггер, первый,второй,55 третий и четвертый элементы И, первый элемент ИЛИ и блок модиФикации адреса, причем вьгоды блока памяти микрокоманд соединены с информационными входами регистра микрокоманд, первый выход блока синхронизации соединен с входом синхронизации регистра микрокоманд, второй выход блока синхронизации соединен с входом синхронизации буферного регистра, группа выходов признака кода логических условий регистра микрокоманд соединена с группой информационных входов дешифратора, выход первого элемента ИЛИ соединен с информационным входом триггера, вход пуска устройства соединен с входом пуска блока синхронизации, о т л и ч а ю щ е е с я тем, что, с. целью повышения достоверности контроля оно содержит первую и вторую схемы сравнения, второй, третий, четвертый и пятый элементы ИЛИ, первую, вторую и третью группы элементов И, блок элементов ИЛИ, пятый, шестой, седьмой, восьмой и девятый элементы И, причем второй выход блока синхронизации соединен с входом синхронизации триггера и первым входом первого элемента И, первая группа адресных входов блока памяти микрохоманд соединена с первой группой выходов поля адресов блока модификации адреса и первой группой информационных входов первого коммутатора, вторая группа адресных входов блока памяти микрокоманд соединена с второй группой выходов поля адресов блока модификации адреса, с группой вхо.дов второго элемента ИЛИ, с информационными входами буферного регистра и первой группой информационных входов второго коммутатора, выходы признака модифицируемого адреса строки поля адресов блока модификации адреса соединены с первыми входами элементов И первой группы, выходы которых соединены с первой группой входов блока элементов ИЛИ, выходы которого соединены с второй группой информационных входов первого коммутатора, группа выходов которого соединена с первой группой входов схемысравнения, вьгход "Равно" которой сое -динен с первым входом первого элемента ИЛИ, группа выходов признака кода логических условий регистра микрокоманд соединена с группой входов кодалогических условий блока модификацииадреса, вход синхронизации которогосоединен с третьим выходом блока синхронизации, первый выход дешифраторасоединен с вторым входом второго элемента И, второй выход дешифратора соединен с первым входом третьего элемента ИЛИ, третий выход дешифраторасоединен с первым управляющим входомвторого коммутатора, первым входомчетвертого элемента ИЛИ и с первымивходами элементов И второй группы,выходы которых соединены с второй 10группой входов блока элементов ИЛИ,четвертый выход дешифратора соединенс вторым входом четвертого элементаИЛИ, с вторым входом третьего элемента ИЛИ, с инверсным входом шестого 15элемента И, с вторыми входами элементов И первой группы и первым Входомседьмого элемента И, группа выходовдешифратора соединена с группой входов пятого элемента ИЛИ, выход которого соединен с первыми входами второго , третьего, четвертого и пятогоэлементов И, выходы которых соединены с адресными входами блока модификацйи адреса, группа входов задания 25кода логической операции которогосоединена с входом задания кода логической операции устройства, выходпризнака следующей микрокоманды регистра микрокоманд соединен с вторым 30вхоцом пятого элемента И, с прямымвходом шестого элемента И и первымвходом второй схемы сравнения, выход Равно" которой соединен с вторым входом седьмого элемента И, выход которого соединен с вторым входом первого элемента ИЛИ, третий вход которого соединен с выходом первого элемента И, выходы признака перехода к следующему адресу микрокоманды регистра микрокоманд соединены с вторыми входами второго, третьего и четвертого элементов И, выход третьего элемента ИЛИ соединен с первым управляющим входом первого коммутатора и вторым управляющим входом второго коммутатора, группа выходов которого соединена с второй группой входов первой схемы сравнения, вьрсод четвертого элемента ИЛИ соединен с вторым управляющим входом первого коммутатора, выход шестого элемента И соединен с третьим управляющим входом второго коммутатора, выходы признака немодифицируемой части адреса регистра микрокоманд соединены с вто рой группой информационных входов второго коммутатора, выход второго элемента ИЛИ соединен с третьим входом первого элемента И, выходы буфер. ного регистра соединены с вторыми входами элементов И второй группы, второй вход второй схемы сравнения соединен с выходом первого элемента И первой группы, выход триггера- является выходом отказа устройг ства.1233155 Составитель А,СиротскТехред О.Сопка актор Н.Рогул орректор Е.Сирохма каз 2772/5 Тираж 671о П ВНИИПИ Гос"ударственного комитета СССР по делам изобретений и.открытий 113035, Москва, Ж, Раушскав наб., д. 415 2 С 25 ЗО 34; Изобретение относится к вычислительной технике и может быть использовацо при проектировании самоконтролируемых микропроцессоров.Цель изобретения - повышение достоверности контроля.Сущность изобретения заключается в повышении достоверности Функционирования путем организации контроля правильности реализации переходов при выполнении микрокоманд безусловных переходов за счет использования свободного поля управления логикой признаков в Формате считываемых микрокоманд.Устройство функционирует следую-. щим образом.Блок модификации адреса, выполненный на микропроцессоре, производит управление формированием адресов микрокоманд, считываемых из блока памяти микрокоманд, а также обработку признаков, поступающих от центрального процессорного элемента. По сформированному адресу микрокоманды из блока памяти микрокоманд происходит ее считывание. Считанная микрокомакда записывается в регистр микрокоманд, Информация с выхода этого регистра, в зависимости от ее назначения, используется следующим образом, Управляющая часть микрокомакды поступает на объект управления, а информация, управляющая переходом к очередному адресу микропрограммы - в блок модификаций адреса, В зависимости от того, какая микрокоманда считана и каким образом осуществляется переход к адресу очередной микрокоманды, в устройстве происходит контроль правильности переходов в микропрограмме на основании сравнения адреса микро- команды перехода и того адреса, к которому необходимо перейти. В предлагаемом устройстве в множе" стве команд реализуется четыре типа команд безусловных переходов: переход в текущей колонке; переход в текущей строке; переход в нулевую строку; переход в любую строку в заданкой колонке в ограниченной области строк.Формат считываемых микрокомакд из блока памяти микрокоманд состоит из следующих полей: поля кода микрооперапкй; поля управления логикой признаков; поля кода Функпий перехода к следующему адресу микропрограммы и нескольких полей переменной части микрокоманды. В первом поле задается код микроопераций, во второмполе содержится информация, управляющая логикой записи признаков и их считывания, в третьем поле - информация о типе перехода к следующему адресу микропрограммы и в полях переменной части микрокоманды - информация о коде маски, константы и т,д.Устройство функционирует с блокомпамяти микрокоманд матричного типа.Для задания адреса ячейки такого блока памяти необходимо задаватьадрес строки и адрес колонки, Блокипамяти матричного типа содержат 32строки и 1 б колонок, чем обеспечивается хранение 512 микрокоманд. Дляадресации ячеек памяти такого блокадостаточно использовать девятиразрядкый код, в котором первые четыреразряда задают адрес колонки, а оставшиеся пять разрядов - адрес строки. В процессе реализации заданныхмикропрограмм из блока памяти микрокоманд могут считываться микрокоманды как условных так и безусловныхпереходов, При этом независимц от типа считьваемых микрокоманд может выполняться или ке выполняться управлекие логикой признаков. При выполнении микрокоманд, реализация которыхтребует управления признаками микрокоманды арифметических операций илогического сдвига), в соответствующем поле записывается управляющаяинформация, В остальных микрокомандах это поле полезной информации дляреализации тех или иных микрокомандне несет. При считывании из блока памяти микрокоманд беэусловныхпереходов такого типа в свободном поле задается контрольная информация, которая определяется типом микрокоманды безусловного перехода, При выполнении перехода к очередной микрокоманде по микрокоманде безусловного перехода первого типа переход осуществляется только;в пределах той колонки, которая определяет адрес микрокомакды безусловного перехода, В этом случае в поле управления логикой призкаков записывается код адреса колонки.При считывании из блока памяти микрокомакд безусловного перехода второго и третьего типов разрядность поля управления логикой признаков не позволяет записывать в кем контроль 123.3155ныи код, поскольку в этом случае длязаписи контрольного кода требуетсяпятиразрядный кад.При считывании из блока памяти микрокоманд безусловного перехода четвертого типа в соответствующем поле этой микрокоманды записывается следующая информация: значения трех младших разрядов контрольного кода определяют адрес строки микрокоманды 10 . перехода, а значение старшего четвер. того разряда - тип разрешенной зоны строк, в которой осуществляется переход. Следовательно, при выполнении микрокоманд безусловных переходов 15 первого типа адрес очередной микро- команды формируется за счет применения адресов строк. Код адреса колонки в этом случае остается без изменений. Поэтому при реализации микро команд этого типа код адреса колонкиостается неизменным в течение времени Т определяемого выражениемТ= (и+1)с,где п - число выполняемых последавательно микракоманд безусловных переходов первого типа;время выполнения одной микро.команды.Контроль правильности реализации ЗО микрокаманд этого типа заключается в проверке равенства кодов, записанных в третьем поле регистра микрокоманд, и выставленного на выходе первого блока магистральных элементов блока модификации адреса.При реализации микрокаманд безусловных переходов второго типа переход к очередной микрокоманде можетбыть осуществлен только в пределаходной и тай же строки. При этом кодадреса строки также остается без изменения в течение времени Т = (и ++ 1)1. Адрес микрокоманды, к которойосуществляется переход, определяетсятолько кодом адреса колонки. Контроль правильности реализации микрокаманд безусловных переходов второготипа заключается в проверке неизменности кода адреса строки в течение времени Т.При реализации микрокаманд третьего типа переход к очередной микрокоманде осуществляется па адресу, который определяется нулевой строкой и Ы одной из возможных шестнадцати колонок. В этом случае правильность перехода к очередной микрокоманде контралируется путем проверки равенства на нуль кода адреса строки микрокоманды перехода.При реализации микрокаманд четвертого типа переход .осуществляется в одной иэ четырех возможных зан строк в заданной колонке к любой строке в выбранной области. При этом номер эоны, в которой выполняется переход, указывается в двух старших разрядах кода адреса строки, а номер строки в указанной области определяется тремя оставшимися разрядами кода адреса стракй. Области, в которых осуществляется переход, подразделяются на два типа: области с четными номерами и нечетными. К областям с четными номерами относятся области, задаваемые следующими комбинациями двух старших разрядов кода адреса строки: 00 и 10; к областям с нечетными номерами относятся области, задаваемые следующими комбинациями: 01 и 11. Области с четными номерами характеризуются нулевым значением в младшем разряде указанных кодовых комбинаций. ,Области с нечетными номерами характеризуются единичным значением в младшем разряде указанных кодовых комбинаций, Старший разряд выхода регистра микракоманд при выполнении микро- команд безусловных переходов этого типа используется для определения одного из двух типов областей: "0" - значение старшего разряда соответствует областям с четными номерами, а ю и1 - областям с нечетными номерами, Три младшие разряда выхода поля адресов регистра микракаманд определяют номер одной из восьми строк в разрешенной области. Контроль правильности реализации микрокаманд этого типа заключается в определении садт ветствия между старшим разрядом выхода регистра микракоманд и младшим разрядом кодовой комбинации, указывающей номер разрешеньай зоны с одной стороны и проверке равенства кода адреса строки в области, записанного в трех младших разрядах кода адреса, выдаваемого с выхода блока магистральных элементов блока модификации адреса, и кода, записанного в трех младших разрядах поля адреса регистра микракаманд. На фиг. 1 представлена микрапро"граммнае устройство управления сконтролем; на фиг, 2 - блок мадифи кации адреса; на фиг. 3 - блок синхронизации; на фиг. 4 - формат микро- команды; на фиг. 5 - области разрешен - кых адресов микрокаманд при организации переходов в микропрограммах привыполкении микрокоманд безусловныхпереходов четырех типов: переход втекущей колонке; переход в текущейстроке, переход ка нулевую строку, 1 Опереход в колонке в ограниченнойобласти строк.Микропрограммное устройство управления с контролем (фиг. 1) содержитблок 1 модификации адреса, блок 2 15памяти микрокоманд, регистр 3 микрокоманд, буферный регистр 4, коммутаторы 5 и 6, дешифратор 7, триггер 8,блок 9 элементов ИЛИ, схему 10 сравнения, группу элементов И 11, элемект ИЛИ 12, группу элементов И 13элементы И 14-18, элемент ИЛИ 19,элемент И 20, схема 21 сравнения,элемент И 22, элементы ИЛИ 23 и 24,блок 25 синхронизации, элемент ИЛИ26, выходы 27-29 блока синхронизации, выходы 30 поля адреса. (столбцы),выходы 31 поля адреса (строки), выходы 32 кода логических условий регистра микрокоманд, выходы 33 поля управпения регистра микрокоманд, выхоцы34 элементов И 15-18,:вход 35 выдачи адреса блока модификации адреса,входы 36 задания кода операции, выход 39 поля управления блока модифи- З 5кации адреса, выход 40 отказа устройства.Блок 1 модификации адреса (Фиг.2)содержит схему 41 определения следующего адреса микропрограммы, регистрЩ42 адреса, регистр 43 признаков, регистр 44 младших разрядов кода команды магистральные элементы 45-47,группу элементов И 48, триггер 49Флагов и элемент И 50.4Блок 25 синхронизации (фиг. 3)содержит триггер 51 пуска и генератор 52 тактовых импульсов с тремявыходами. Вход 37 пуска усгройстваедсоединен с единичным входам тригге дра 51 пуска, единичный выход которого соединен с входом снятия блокировки генератора 52 тактовых импульсов.Блок 1 модификации адреса предназначен для оргакизапии формирования адресов микрокоманд микропрограммы иуправления обработкой логикой приз".накав,Блок 2 памяти микрокоманд предназначен для хранения кодов микрокоманд.Регистр 3 микрокомакд предназначен для записи и хранения считываемых микрокомакд и выделения из ихформатов инФормационных и управляюцех полеиДешифратор 7 предназначен для определения типа микрокоманды безусловного перехода и формирования сигнала управления передачи кода поляуправления логикой признаков в блок,Буферкый регистр 4 гредназкачендля хранения кода адреса строки блока 2 памяти микрокоманд.Коммутаторы 5 и 6 предназначеныдля передачи кодов адресов микрокоманд в схему 10 сравнения, а последняя - для сравнения поступающихкодов,Триггер 8 предназначен для фиксации факта отказа (сбоя) в работе устройства,Блой 25 синхронизации предназначен для формирования сигналов синхронизации блока 1 модификации адреса, регистра 3 микрокоманд и контрольного оборудования.Группа элементов И 11 предназначена для передачи кода адреса строкиблока 2 .йамяти микрокоманд при выполнении микрокоманды безусловного перехода четвертого типа.Группа элементов И 13 предназначена для передачи кода адреса строкиблока 2 памяти микрокоманд при считывании микрокоманд второго типа,Элемент И 14 предназначен для формирования сигнала ошибки при ее возникновении в случае считывания микрокоманды безусловного перехода третьего типаЭлемент И 20 предназначен для маскирования старшего разряда кода адреса строки, записанного в поле управления логикой признаков регистра3 мнкрокомакд ка "0", при считываниимикрокомакды безусловного переходачетвертога типа. Элементы И 13-18 предназначены цня передачи соответствующих разрядов кода управления логикой признаков при выполнении микрокаманд, управляющих обработкой признаков.Элемент И 22 пуедназначен для передачи сигнала ошибки при неправильном переходе к адресу очередной мик 1233155рокоманды в случае реализации микро- команды безусловного перехода четвертого типа.Блок 9 элементов ИЛИ предназначен для передачи кодов адресов строк блока 2 памяти микрокоманд с выхода буферного регистра 4 и с выхода элементов И 11. О Элемент ИЛИ 12 предназначен для определения ошибки при переходе к строке с ненулевым адресом при выполнении микрокоманды безусловного перехода третьего типа. 15Элементы ИЛИ 23 и 24 предназначе-ны для формирования сигналов управления коммутаторами 5 и 6 соответственно.Элемент ИЛИ 19 предназначен для формирования сигнала управления рабо-, той элементов И 15-18.Элемент ИЛИ 26 предназначен для передачи сигнала сбоя (отказа) на ин формационный вход триггера 8 в случае его возникновения на выходах соответствующих элементов.Схема 21 сравнения предназначена для сравнения признака зоны строк, в которой выполняется переход с признаком разрешения зоны, в которой разрешается такой переход.Блок 25 синхронизации предназначен для выработки сигналов синхронизации устройства.В устройстве осуществляется контроль правильности реализации микро- команд безусловных переходов следующим образом.В поле управления логикой призна 40 ков каждой микрокоманды безусловного перехода записывается контрольньй код, который в зависимости от типа реализуемой микрокоманды может быть кодом адреса строки или колонки, При45 этом, если из блока 2 памяти микро- команд считывается микрокоманда безусловного перехода первого типа, то в соответствующем поле регистра 3 считанной микрокоманды записывается код адреса колонки, в которой происходит переход. Условием правильного перехода считается переход по одной и той же колонке. При этом код адреса колонки не изменяется, После формирования кода55 адреса очередной микрокоманды происходит сравнение кода адреса колонки, записанного в соответствующем поле регистра 3 микрокоманд, и адреса поступающего с выхода 30 блока 1 модификации адреса. Код с выхода соответ ствующего поля регистра 3 микрокоманд поступает на вход синхронизаФ ции коммутатора 5.Дешифратор 7 на основании информации, записанной в поле управленияпереходами к следующему адресу микропрограммы, возбуждает один из первых четырех выходов, тем самым подает управляющий сигнал на вход коммутатора 5 и на управляющий вход коммутатора 6. Код адреса колонки блока 2памяти микрокоманд поступает с выхода 30 блока 1 модификации адреса,тем самым на вход схемы 10 сравненияподаются два кода адреса колонки. Втом случае, если микрокоманда безусловного перехода первого типа выполнена правильно, то на входы схемы10 сравнения поступают два одинаковых кода, и сигнал ошибки на ее выходе отсутствует, Если переход вьптолнен неправильно, то единичный сигналс выхода схемы 10 сравнения поступает на вход триггера 8 отказа, и работа устройства блокируется,В случае реализации микрокомандыбезусловного перехода второго типа,переход к следующему адресу производится в текущей строке. При этом адрес строки блока 2 памяти микрокоманд адреса микрокоманды безусловного перехода второго типа и адресстроки микрокоманды, в которой происходит переход, должны быть одинаковыми. Дешифратор 7 возбуждает одиниз соответствующих первых четырехвыходов и подает единичный сигнална управляющий вход коммутатора 5 иуправляющий вход коммутатора 6. Кодадреса строки блока 2 памяти микрокоманд микрокаманды безусловного перехода перед считыванием ее из этогоблока запишется в регистр 4. Этоткод поступает с выхода буферного регистра 4 через группу элементов И13 и блок 9 на информационный входкоммутора 6. А код адреса строки микрокоманды, в которой происходит переход, поступает с выхода 31 блока 1модификации адреса на информационньйвход коммутатора 5. Условием правильного перехода является равенствокодов, поступивших с выходов коммутатора 5 и 6, на соответствующие входды схемы 10 сравнения. В случае неправильного перехода единичный сигнал с выхода схемы 10 сравнения поступает на вход триггера 8, и работаустройства блокируется.В случае считывания микрокомандыбезусловного перехода третьего типа условием правильного перехода кадресу следующей микрокоманды является нулевое значение кода адресастроки блока 2 памяти микрокомандытой микрокоманды, в которой происходит переход.Код адреса строки той микрокоманды,в.которой происходит переход, поступает на вход элемента ИЛИ 12. В томслучае, если поступивший код имеетдействительно нулевое значение, тона выходе этого элемента единичныйсигнал не сформирован, и сигнал неправильного перехода на выходе элемента И 14 также не сформирован.В том случае, если переход происходит по адресу, расположенному не в нуле- р 5вой строке, а в любой другой, то навыходе элемента И 14 появляется единичный сигнал, который поступает навход триггера 8,При считывании микрокоманды безус-оловцого перехода четвертого типа правильность перехода определяется проверкой соответствия номера разрешенной зоны строк и номера строки в нейблока 2 памяти микрокоманд, запис.анного в поле управления логикой признаков регистра 3 микрокоманд, и номера зоны и номера строки в них, поступающих с выхода 31 блока 1 модификации адреса. Значение старшегоразряда кода, записанного в поле управМция логикой признаков разрядакода, записанного в поле управлениялогикой признаков регистра 3 микрокоманд, равное цОц и соответствуетзонам строк с номерами 0 и 2,а со зцачением "1" - зонам строкс номерами 1 и 3. Соответствиеномеров зон строк блока 2 памяти мик.ракомацд проверяется путем сравнениязначений четвертого разряда кода адреса строки, поступающего с выхода31 блока модификации адреса и старшего разряда кода, записанного в соответствующем ноле регистра 3 микроко 55мацд. Это с.равнение производится всхеме 21 сравнения. Сравнение адресов стр к в разрешенных зонах производится следующим образом. Значение старшего разряда кода, записанного ч поле управления логикой признаков регистра 3 микрокомацд, маскируется "0" на элементе И 20. Значение кода с выхода этого поля регистра 3 поступает на информационный вход коммутатора 5.Дешифратор 7 возбуждает соответствующий один из первых четырех своих выходов и подает единичный сигнал на управляющий вход коммутатора 5 и коммутатора 6. Значения трех младших разрядов кода адреса строки разрешенной зоны с выхода 31 блока 1 модиификации адреса поступают через группу элементов И 11 на информацинный вход блока 9. С выходов элементов И 13 группы на информационный вход блока 9 поступает нулевой пятиразрядный код. В результате на информационный вход коммутатора 6 поступает пятиразрядный код, в котором значения двух старших разрядов равны нулю. На коммутаторе 5 происходит формирование кода из четырехразрядного и маскирование старшего разряда "0" путем подачи сигнала запрета на его управляющий вход, в результате чего уже пятиразрядные коды с выходов коммутаторов 5 и 6 поступают на соответствующие входы схемы 10 сравнения, Если адреса строк в зонах совпадают, что свидетельствует о правильном переходе то работа устройства продолжается, В противном случае единичный сиг. нал с выхода схемы 10 сравнения поступает через элемент ИЛИ 26 на вход триггера 8, и работа устройства блокируется. Блок 1 модификации адреса осуществляет адресацию микрокоманд, считываемых на блоке 2 памяти микрокоманд и анализирует сигналы переноса и переполнения, поступающие из центрального процессорного элемента. Организация адресации в блоке 1 осуществляется схемой 41 формирования следующего адреса микропрограммы на основе коца команды, поступающего с входа 36, кода текущего адреса, поступающего с выходов регистра 42 адреса, кода управления переходом к следующему адресу микропрограммы, и поступающего с выхода 32 регистра 3 микро- команд. Для формирования кода адреса первой микрокоманды соответсявующей микропрограммы используется значениестарших четырех разрядов кола комацды, поступающего, на вход 36 блока 1.Значения четырех младших разрядов кода команды, записанные в регистр 44, определяют код операции. По значениям четырех старших разрядов кода команды, поступившего с входа 36 блока 1 на схему 41 формирования следующего адреса, и значениям адресов 1 О строк и столбцов, поступающим с выходов регистра 42 на входы схемы 41, происходит определение адреса первой микрокоманды, реализуемой микропрограммы. Адрес первой микрокомацды 15 микропрограммы с выхода схемы 41 поступает на вход регистра 42, В последнем происходит выделение из кода адреса микрокоманды адреса строки и столбца блока 2 памяти микрокоманд, которые поступают на входы соответствующих магистральных элементов 46 и 47 и на входы схемы 41.После считывания микрокоманды из блока 2 памяти микрокоманд код управ-,5 ления переходом к следующему адресу микропрограммы с выхода 32 регистра 3 поступает на вход схемы 41. В схеме 41 происходит формирование адреса микрокоманды перехода по значениям, поступающим с входа 32 и с выходов регистра 42 адресов микрокоманд.Выдача кода адреса микрокоманды с выходов регистра 42 адресов осуществляется через блоки 46 и 47 магистральных элементов. Код адреса микрокоман 35 ды по синхроимпульсам, поступающим на синхровход блока 1 модификации адреса, производит выдачу кода адреса микрокоманлы с выходов магистраль 40 ных элементов 46 и 47, При этом разрешающим сигналом на выдачу кода адреса колонки является синхроимпульс, поступающий ца управляющую группу входов Е блока 4 б магистральных эле 45 ментов. Условием выдачи кода адреса строки является наличие единичного сигнала, поступающего с входа 35 блока 1 модификации адреса ца вход элемента И 50 с выхода блока приоритет 50 ного прерывания ца разрешение выдачи адреса строки и наличие того же синхросигцала.Устройство функционирует следующим образом.В исходном состоянии все элементы55 памяти находятся в состоянии "0". На вход 37 устроцства посту 1 ает сигнал "Пуск" и ца выхоле 27 блока 25 синф ц хронизации появляется сигцал 1 который поступает на вход синхронизации блока 1 модификации адреса, По коду команды, поступившему с входа 36 устройства ца первый информационный вход этого блока, в схеме 41 блока 1 происходит формирование адреса первой микрокоманды микропрограммы и запись сформированного адреса в регистр 42 адресов микрокомацд по переднему фронту того же синхроимпульса. После записи адреса первой микрокоманды в регистр 42 адресов код адреса колонки поступает на вход блока 46 магистральных элемецтов и.на четвертый информационный вход схемы 4 1. Код адреса строки поступает на вход блока 47 магист- . ральных элементов и на пятый информационный вход схемы 4 1. По сигналу "1" синхроимпульса, поступающему на первый вход элемента И 50 и на вход Е блока 46, код адреса колонки поступает на выход 30 блока 1. При наличии сигнала "1" разрешениясчитывания кода адреса строки, поступающего с третьего входа блока 1 на второй вход элемента И 50, на его выходе сформируется сигнал "1", который поступает на вход Е блока 47, разрешая тем самым выдачу кода адреса строки на выход 31 блока 1. По коду адреса микрокоманды (коду адреса колонки и коду адреса строки) происходит считывание микрокоманды из блока 2 памяти микрокоманд.Код адреса микрокоманды поступает ца вход блока 2 памяти микрокоманд, код адреса колонки - на информационный вход коммутатора 6, а код адреса строки - на вход элемента ИЛИ 12 и на информационный вход буферного регистра 4, при этом три младших раэря да этого кода поступают на входы элементов И 11 группы, а значение четвертого разряда - на вход схемы21 сравнения.По синхроимпульсу, поступающему с выхода 28 блока 25 синхронизации на синхровход буферного регистра 4 и триггера 8, происходит запись кода адреса строки микрокоманды в буферный регистр 4 и подтверждение первого состояния триггера 8. Через времяпо синхроимпульсу, поступившему с выхода 29 блока 25 на синхровход регистра 3 микрокоманд, происходит запись считанной микрокомацдыиз блока 2 в регистр 3, Переменная часть микрокоманды поступает с выхода 33 регистра 3 на выход устройства, Код управления переходами к следующему адресу микропрограммы поступает с выхода 32 регистра 3 на вход дешифратора 7 и ка вход задания логических условий блока 1, Код управления логикой признаков поступает с 1 О регистра 3 на входы соответствующих элементов И 15-18 и на информационный вход коммутатора 5, а значение старшего разряда этого кода поступает на вход элемента И 20. 15В этом случае, если из блока 2 памяти микрокоманд считана микрокоманда, которая осуществляет управление логикой признаков, то на одном из старших выходов, начиная с пятого, 2 О дешифратора 7 появляется сигкал "1", который поступает через элемент ИЛИ 19 на входы элементов И 15-18 и открывает их. Информация с выхода регистра 3 микрокоманд поступает через открытые элементы И 15-18 на вход блока 1 модификации адреса с целью обработки признаков, вырабатываемых процессорным элементом и поступающи с входа 35 задания кода логических ЗО операций блока 1 модификации адреса на вход триггера 49 Флагов.В том случае, если микрокоманда не управляет логикой признаков и является микрокомандой безусловного перехода, то в устройстве его работа и контроль правильности переходов осуществляется следующим образом. Если считана микрокоманда безусловного перехода первого типа то на первом выходе дешифратора 7 появляется сигнал "1", который поступает на вход элемента ИЛИ 23 и с его выхода - на управляющий вход коммутатора45 5, а также на управляющий вход коммутатора 6, разрешая прохождение информации через соответствующие информационные входы, В этом случае значение старшего разряда кода, записан 5 О ного в поле управления логикой признаков, не изменяется, так как элемент И 20 продолжает находиться в открытом состоянии. Элемент И 22 находится в закрытом состоянии. Эле,55 мент И 14 группы элементов И 11 и 13 блокированы нулевыми сигналами, поступающими с четвертого выхода дешиф- ратора 7. 11 ри этом на информационные входы коммутатора 5 поступает код номера колонки, г которой осуществляется переход, записанный в поле управления логикой признаков считанной микрокомакды. При этом значение старшего разряда этого кода поступает на вход элемента И 20. На его другой вход поступает сигнал "0 с четвер - того вьгхода дешифратора 7 и открывает его, в результате чего значение старшего разряда не изменяется. Конт рольный коц поступает с выхода комму татора 5 на информационный вход схемы ,0 сравнения. По синхроимпульсу, поступившему с выхода 27 блока 25 синхронизации, происходит формирование кода ацреса очередной микрокомакды в блоке 1 модификации адреса, При этом значение кода адреса колонки на выходе 30 блока 1 при правильном переходе остается неизменньм. Значение этого кода поступает на икформациокный вход коммутатора 6 и с ж.го выхода поступает на информационный вход схемы 10 сравнения. Если переход выполнен неправильно, то ка выходе схемы 10 появляется сигнал "1", который поступает на вход элемента ИЛИ 26 и далее на информационный вход триггера 8. По заднему фрокту синхроимпульса, поступившего с выхода 28 блока 25 синхронизации на соответствующий вход триггера 8, происходит запись "1" (сигнала ошибки) и на выходе 40 сбоя (отказа)триггера 8 появляется сигнал "1". Ра.- бота устройства блокируется. В томслучае, если переход произведен вер"ко, работа устройства продолжается.Если из блока 2 памяти микрокомандсчитана микрокоманда безусловного пе.рехода второго типа, то после ее записи в регистр 3 микросхемы на треть.ем выходе дешифратора 7 появляется1сит н ал 1 , который поступает на управляющий вход коммутатора 5 , навх ад элемента. ИЛИ 2 4 и с е го выхода -на управляющий вход коммутатора 6,а также э тот сигнал " 1 " пос т упа ет наупра вляющий вход группы элементов И1 3 , разрешая передачу кода адресастроки и з б уф ер но г о регистра 4 н а инФ ормационный вход блока 9 и дал е е н аинФормационный вход коммутатора б .По сигналу " 1 " с выхода 2 7 блока 2 5с р ав ке ния в блоке 1 модификации адр ес и происходит Формир ов ание кода адр ес а оч ер едко й ми кр о к ома нды .При этом код адреса строки микро- команды перехода поступает на информационный вход открытого коммутатора 5 и с его выхода - для сравнения на информационный вход схемы 10 сравнения, В этом случае, если переход произведен неправильно, т.е. происходит обращение к строке с другим адресом, то на выходе схемы 10 сравнения появ О ляется сигнал "1", который поступает на вход элемента ИЛИ 26 и далее на информационный вход триггера 8. По заднему фронту синхроимпульса, поступившего с входа 27 блока 25 синхрони зации на синхровход триггера 8, проис. ходит его установка в состояние" "1", и на выходе 40 устройства появляется сигнал сбоя (отказа).20 Если формирование кода адреса очередной микрокоманды происходит правильно, то работа устройства продолжается.Если в регистр 3 микрокоманд запи.25 сана микрокоманда безусловного перехода третьего типа, то на третьем выходе дешифратора 7 устанавливается сигнал "1", который поступает на вход элемента И 14, который закрыт нулевым сигналом с выхода 28 блока 25 синхронизации. По синхроимпульсу, поступившему с выхода блока 25 синхронизации на вход синхронизации блока 1, на его информационных выходах 35 устанавливается код адреса очередной микрокоманды. Если значение кода адреса строки не равно 0", это говорит о неправильном переходе к очередной микрокоманде, то на выходе эле мента ИЛИ 12 появляется сигнал "1", который поступает на вход элемента И ф 14. По переднему фронту синхроимпульса, поступившего с выхода 28 блок 25 синхронизации на другой вход этого элемента, сигнал "1" с его выхода по ступает на вход элемента ИЛИ 26 и че. рез него на информационный вход триггера 8. По заднему фронту этого импульса триггер Я переходит в состояние "1", и на выходе 40 устройства устанавливается сигнал "1" отказа (сбоя). В том случае, если переход произведен правильно, то на выходе элемента ИЛИ 12 устанавливается сигнал "0", который блокирует по-второму входу элемент И 14, и на выходе последнего тоже устанавливается сигнал "0", Работа устройства в томслучае продолжается. Если из блока 2 считана микрокоманда безусловного перехода четвертого типа, то работа устройства заключается в следующем. На четвертом выходе дешифратора 7 устанавливается сигнал "1", который поступает на входы элементов ИЛИ 24 и 23, на вход элемента И 20 и на управляющий вход группы элементов И 11 и открывает ее. В.,результате этого на выходе элемента И 20 устанавливается сигнал "0", с выходов элементов И1 группы значения трех младших разрядов кода адреса строки поступают на информационный вход блока 9 и е его выхода на информационный вход коммутатора 6. С выхода элемента ИЛИ 24 на управляющий вход коммутатора 6 поступает сигнал , который открывает его. Поскольку другой информационный вход этого коммутатора закрыт сигналом "0" с третьего выхода дешифратора 7, то на выходе коммутатора 6 находится пятиразрядный код, в котором два старших разряда равны "0, и этот код поступает на информационный вход схемы 10 сравнения, С выходов регистра 3 микрокоманд четырехразрядный код поступает на информационные входы, коммутатора 5, Поскольку другой информационный его вход закрыт сигналом "0 с третьего выхода дешифратора 7, то на выходе коммутатора 5 присутствует пятиразрядный код, в котором два старших разряда равны "0". Этот код поступает на информационный вход схемы 10 сравнения. При этом на ее выходе может находиться сигнал "1", поскольку формирование адреса микрокоманды перехода еще не произошло. Кроме того, значение старшего разряда кода адреса строки этой микрокоманды, записанной в регистре 3 микрокоманд, поступает на другой вход схемы 21 сравнения. Значение старшего разряда кода, поступающего ,с выхода регистра 3, поступает на вход схемы 21 сравнения, выходной сигнал которой поступает на вход элемента И 22. Значение этого сигнала также может быть равно "1" или "0", так как формирование адреса микрокоманды еще не произошло в блоке 1. Если значение сигнала на выходе схемы 21 сравнения равно "1", то на вы

СмотретьЗаявка

3720859, 04.04.1984

ПРЕДПРИЯТИЕ ПЯ М-5156

СИДОРЕНКО НИКОЛАЙ ФЕДОРОВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, САМАРСКИЙ ВИКТОР БОРИСОВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, ОСТРОУМОВ БОРИС ВЛАДИМИРОВИЧ

МПК / Метки

МПК: G06F 11/36

Метки: контролем, микропрограммное

Опубликовано: 23.05.1986

Код ссылки

<a href="https://patents.su/14-1233155-mikroprogrammnoe-ustrojjstvo-upravleniya-s-kontrolem.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления с контролем</a>

Предыдущий патент: Устройство для возведения чисел в квадрат по модулю

Следующий патент: Устройство для контроля цифровых блоков

Случайный патент: Многоконтурный магнитный фильтр