Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

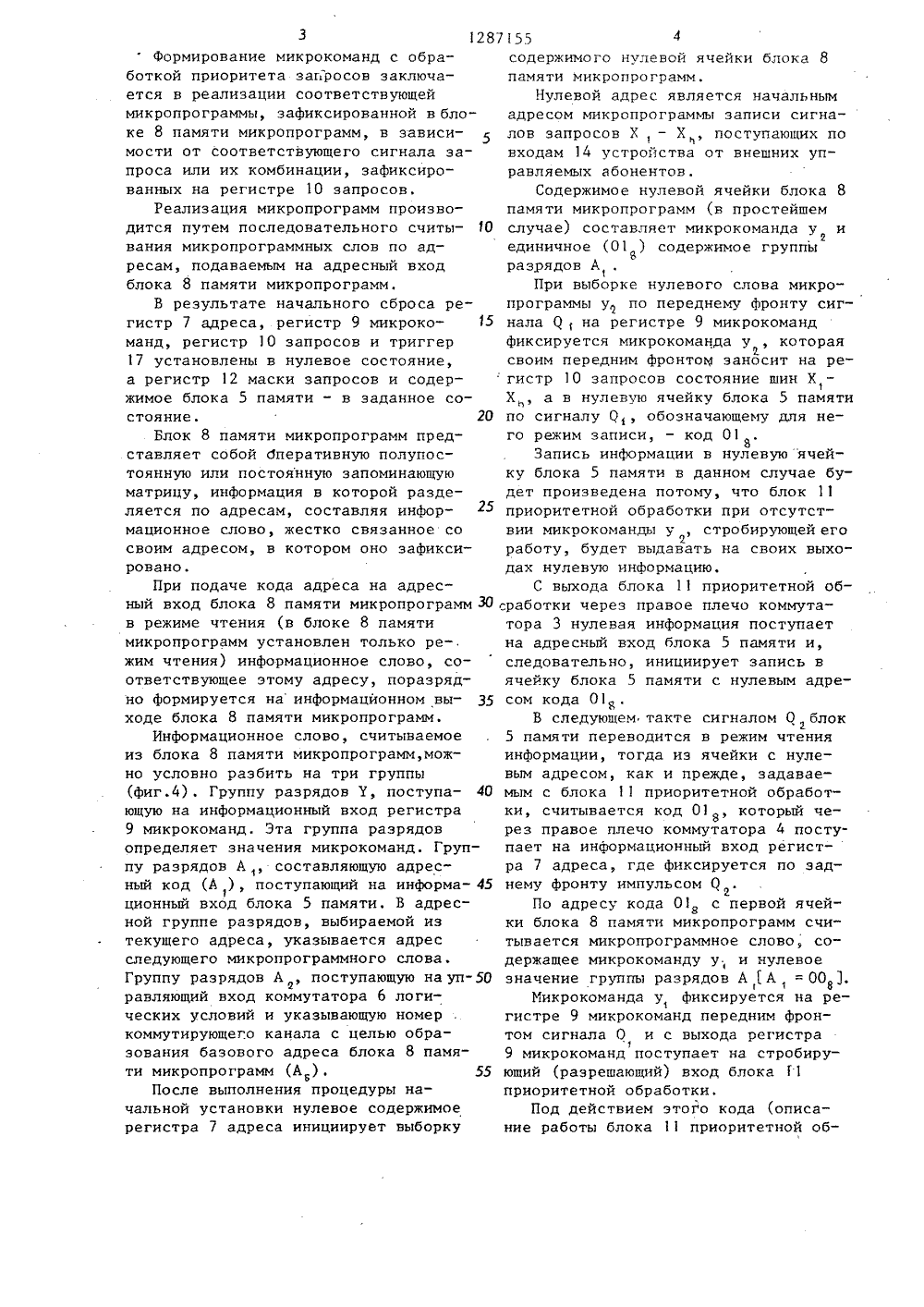

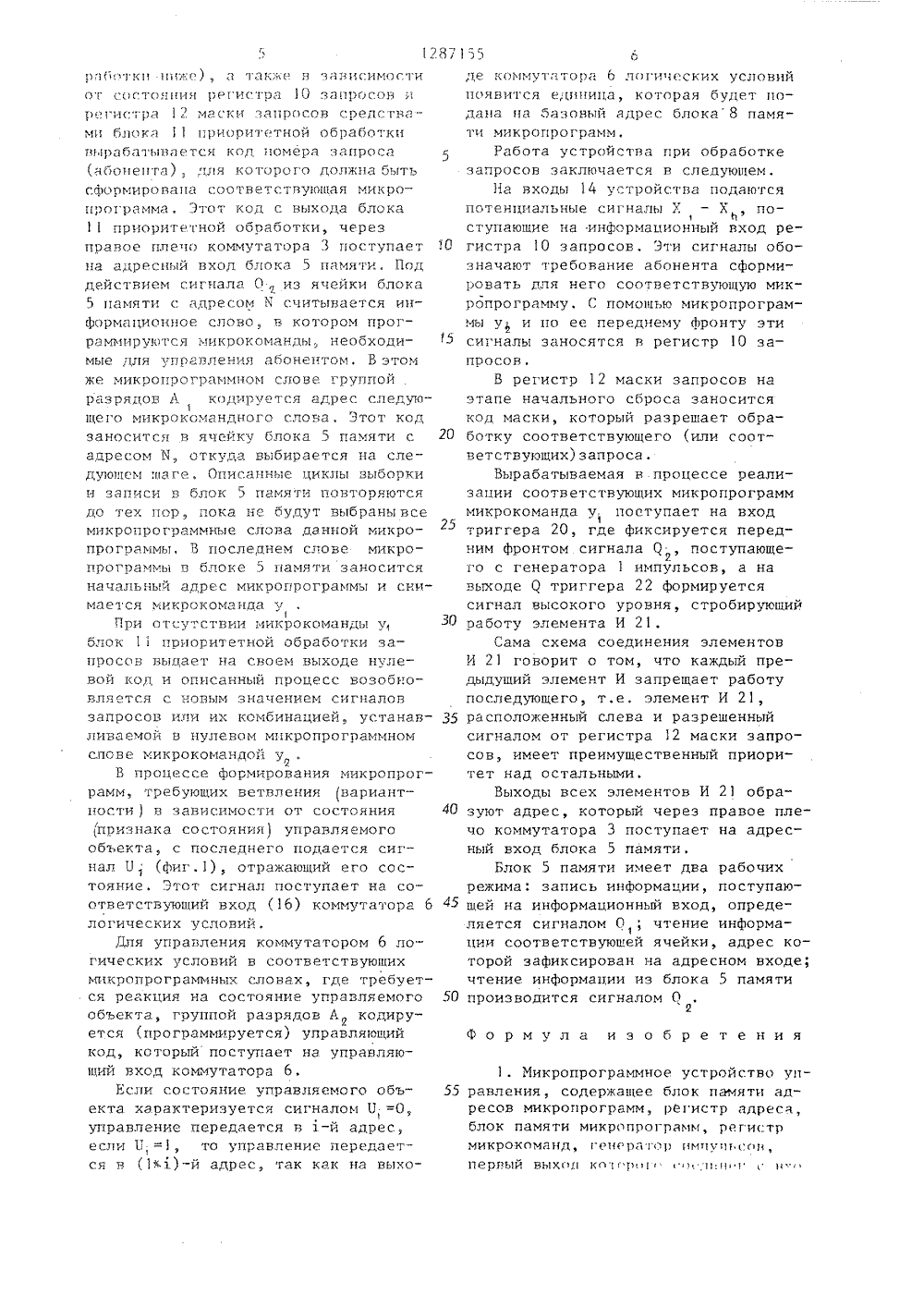

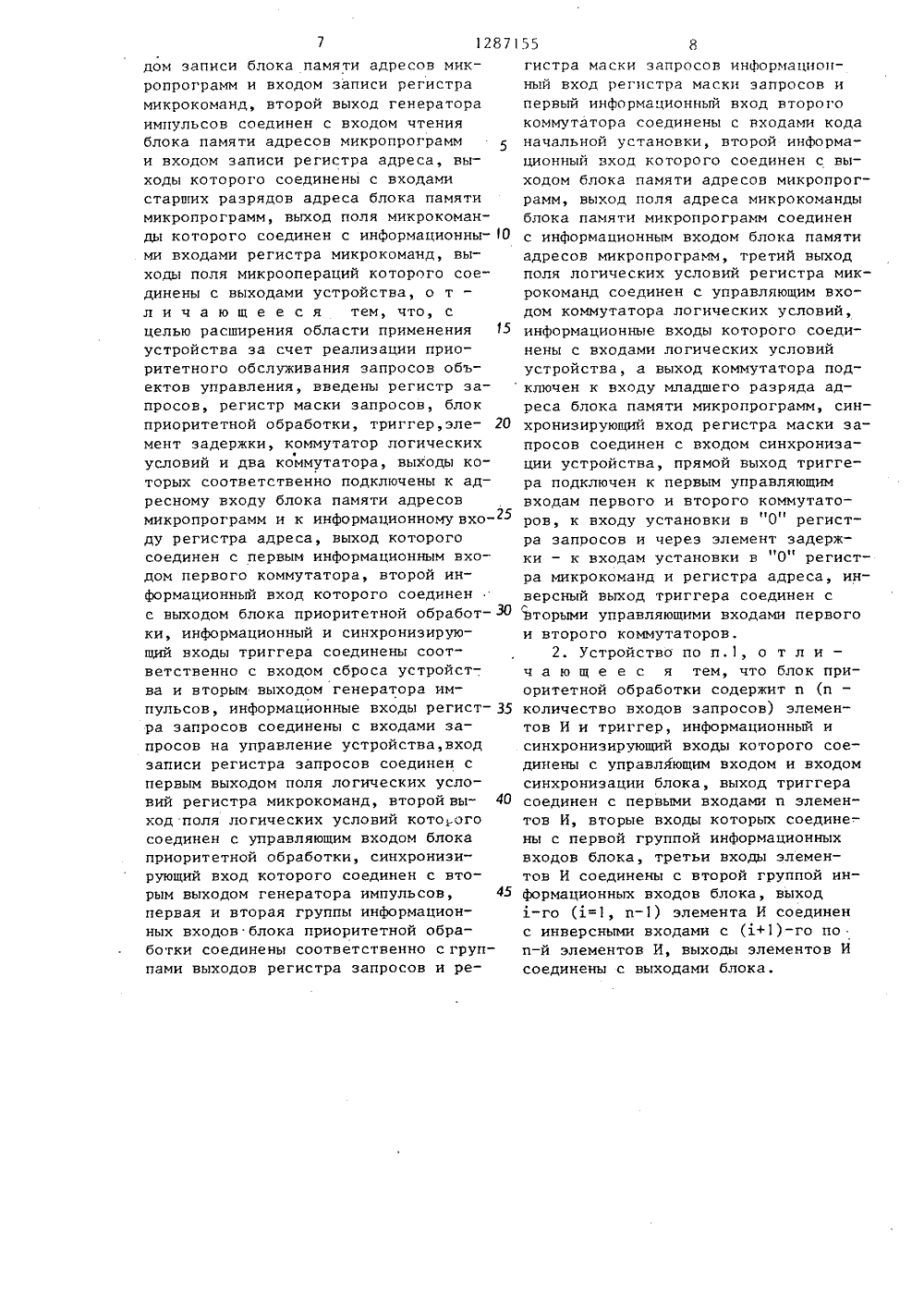

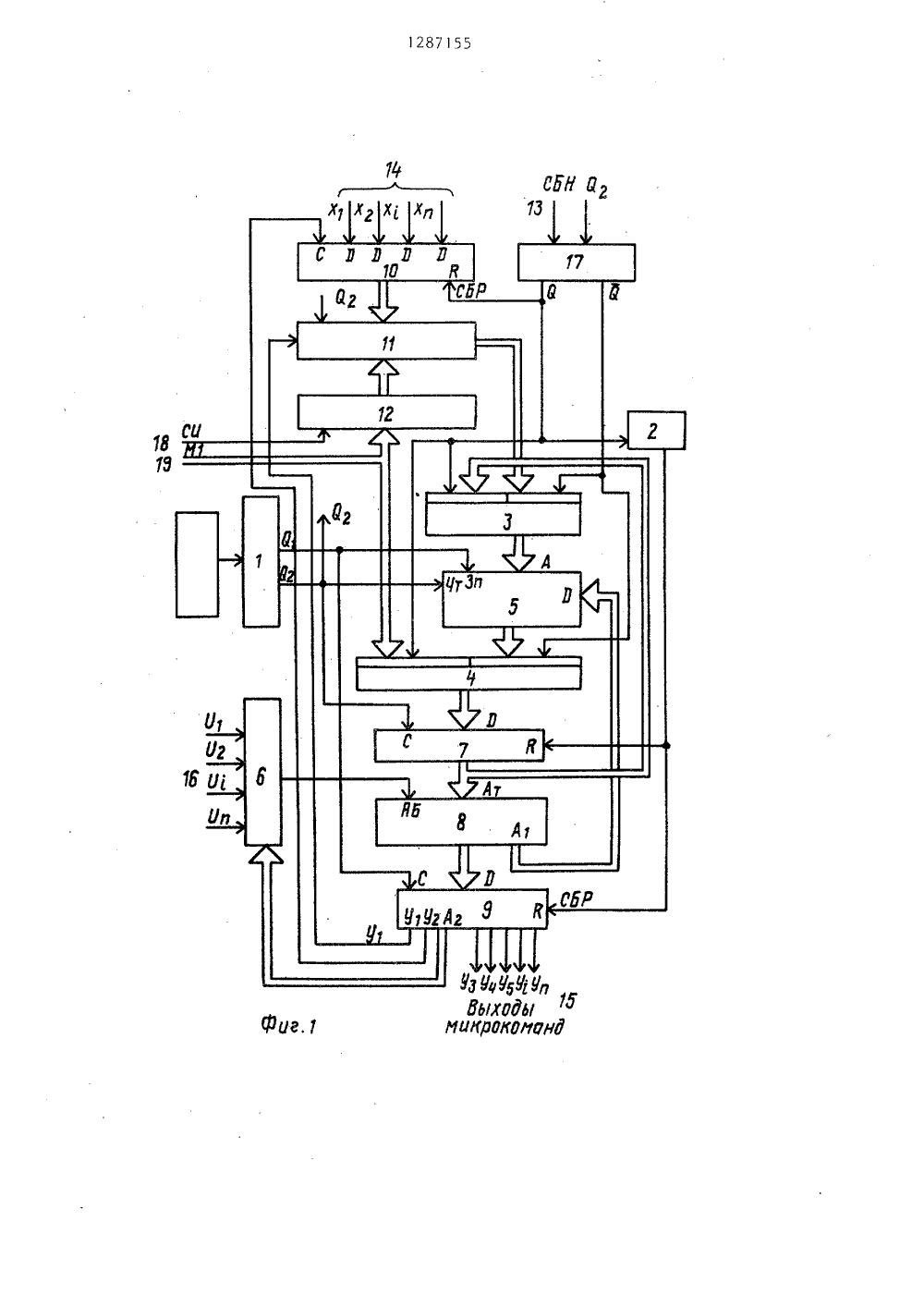

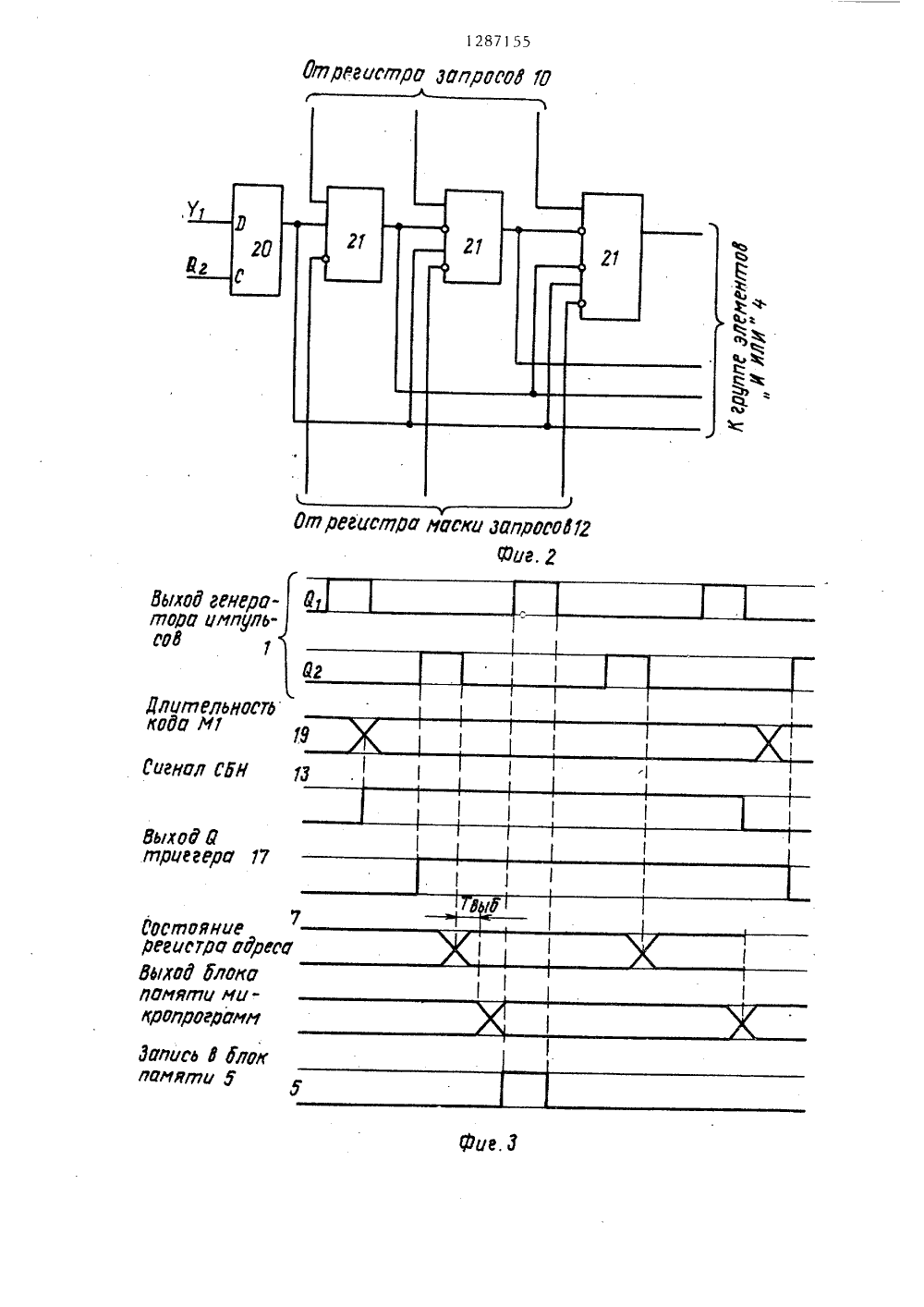

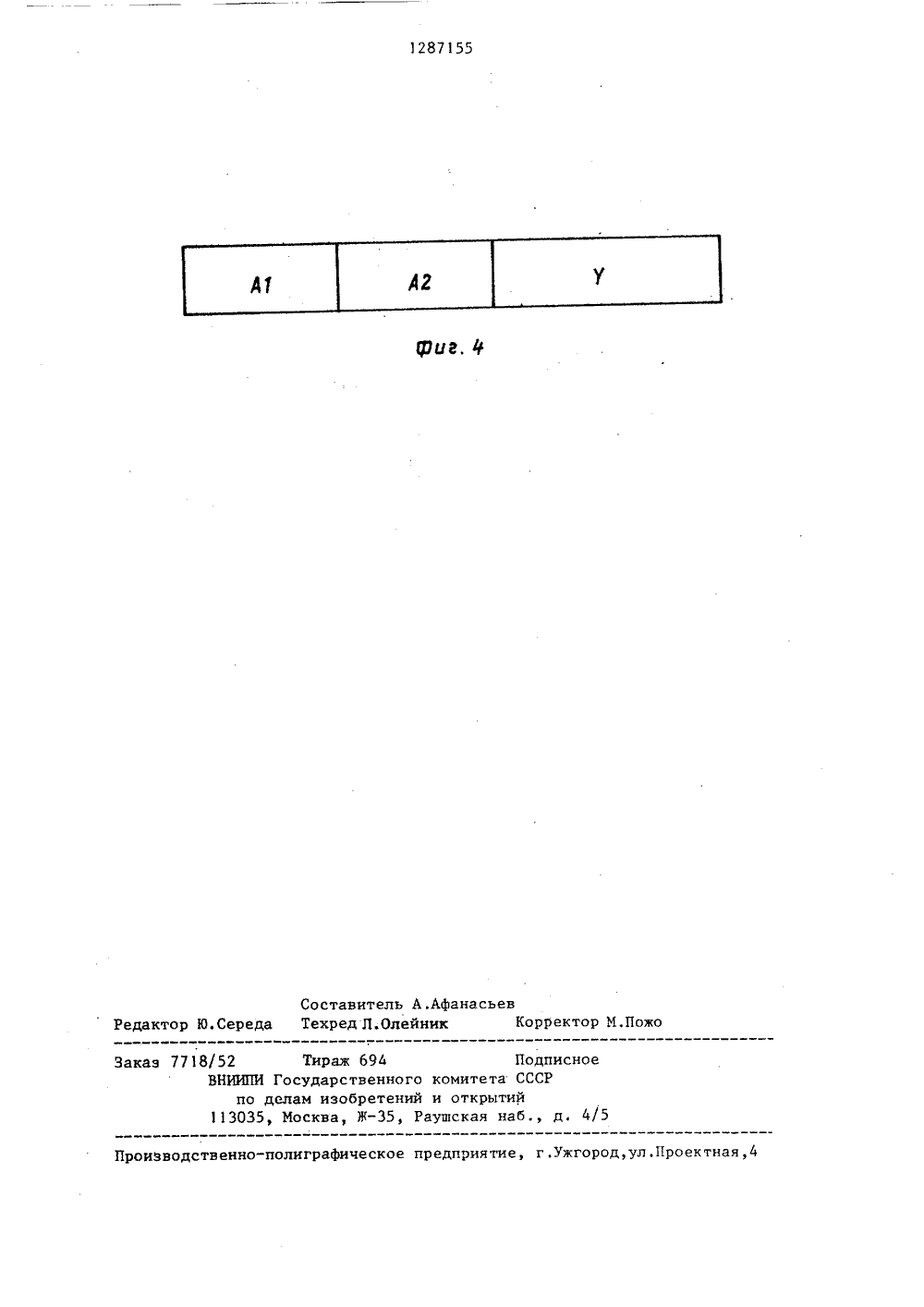

1 1287Изобретение относится к цифровойвычислительной технике и может бытьиспользовано в качестве устройствасинхронизации и управления в многоканальных вычислительных устройствахи многопрограммных вычислительных системах,Цель изобретения - расширение области применения микропрограммногоустройства за счет реализации приоритетного обслуживания запросов обьектов управления.На Фиг.1 представлена функциональная схема предлагаемого устройства;на Фиг. 2 - блок приоритетной обработки; на Фиг.З - временная диаграмма работы устройства в режиме начальной установки; на фиг.4 - формат микропрограммного слова.Микропрограммное устройство управ-ления (фиг.1) содержит генератортактовых импульсов, элемент 2 задержки, два коммутатора 3 и 4, блок 5памяти адресов микропрограмм, коммутатор 6 логических условий, регистр, 7 адреса, блок 8 памяти микропрограмм,регистр 9 микрокоманд, регистр 10 запросов, блок 11 приоритетной обработки, регистр 12 маски запросов,вход 13 СБН (начального сброса),входы 14 запросов, выходы 15 микрокоманд, входы 16 логических условий,триггер 17, вход 18 синхроимпульса,вход 19.Блок приоритетной обработки (фиг.2) Зсодержит триггер 20 и и (и - число запросов) элементов И 21 и предназна-.,чен для обеспечения обработки запросов в порядке их приоритетности.В работе микропрограммного устройства управления можно выделитьследующие режимы: режим начальной установки; режим формирования микрокоманд с обработкой приоритетности запросов.,В режиме начальной установки наустройство параллельно-последовательно поступают сигналы СБН на вход 3и коды начальной установки на вход19 (фиг.З). В режиме начальной установки происходит занесение в блок 5памяти адресов микропрограмм адресов А, являющихся начальными длякаждой из подпрограмм, зафиксированных блоком 8 памяти микропрограмм,Записью сигнала СБН на триггер 17производится синхронизация сигналаСБН передним фронтом тактирующего 55 2импульса ( от генератора 1 импульсов (Фиг,З),Сигналом с выхода Ц триггера 17открываются левые плечи коммутаторов3 и 4, Через левое плечо коммутатора 4 кодовая информация с входа 19поступает на информационный вход регистра 7 адреса, где фиксируетсязадним фронтом того же сигнала Цу.Этот код, зафиксированный на регистре 7 адреса, через левое плечо коммутатора 3 поступает на адресный входблоке 5 памяти адресов микропрограмм.Под действием этого адресного кода с соответствующей ячейки блока 8памяти микрокоманд считывается информация, содержащая код начальногоадреса. соответствующей микропрограммы. Этот код с задержкой ТюыГ(времявыборки информации из блока 8 памяти)поступает на информационный вход блока 5 памяти адресов микропрограмм,где Фиксируется сигнал (ф от генератора 1 импульсов в соответствующуюячейку блока 5 памяти по адресу, который поступает на адресный вход блока 5 памяти, т.е. по адресу, которыйпоступает на вход 19 и зафиксированна регистре 7 адреса.По окончании сигнала СБН на Я-выходе триггера 17 устанавливается нулевой потенциал (Фиг.З, строка 6),который закрывает левые плечи коммутаторов 3 и 4, На Я-выходе триггера 17 устанавливается высокий потенциал, который открывает правые плечи обеих коммутаторов 3 и 4.По заднему фронту сигнала, формируемого на Я-выходе триггера 17, налинии 2 задержки выделяется импульс,который поступает на К-вход регистра7 и устанавливает регистр в нулевоесостояние. С этого момента начинается работа устройства в режиме формирования микрокоманд, Для записи начальных адресов других микропрограммописанный процесс записи адресногокода должен повториться.Таким образом, в соответствующиеячейки блока 5 памяти будут занесенывсе адресные коды, обозначающие начало микропрограмм, зафиксированныхв блоке 8 памяти микрокоманд,Кроме того, сигнал с Ц выходатриггера 17 поступает на К-входы регистра 9 микрокоманд и регистра 10запросов, чем обеспечивается их сбросв нулевое состояние.128Формирование микрокоманд с обработкой приоритета запросов заключается в реализации соответствующей микропрограммы, зафиксированной в блоке 8 памяти микропрограмм, в зависимости от соответствующего сигнала запроса или их комбинации, зафиксированных на регистре 10 запросов.Реализация микропрограмм производится путем последовательного считы вания микропрограммных слов по адресам, подаваемым на адресный вход блока 8 памяти микропрограмм.В результате начального сброса регистр 7 адреса, регистр 9 микроко манд, регистр 10 запросов и триггер 17 установлены в нулевое состояние, а регистр 12 маски запросов и содержимое блока 5 памяти - в заданное состояние. 20Блок 8 памяти микропрограмм представляет собой оперативную полупостоянную или постоянную запоминающую матрицу, информация в которой разделяется по адресам, составляя информационное слово, жестко связанное со своим адресом, в котором оно зафиксировано.При подаче кода адреса на адресный вход блока 8 памяти микропрограмм 30 в режиме чтения (в блоке 8 памяти микропрограмм установлен только режим чтения) информационное слово, соответствующее этому адресу, поразрядно формируется на информационном вы ходе блока 8 памяти микропрограмм.Информационное слово, считываемое из блока 8 памяти микропрограмм,можно условно разбить на три группы (фиг.4) . Группу разрядов У, поступа ющую на информационный вход регистра 9 микрокоманд. Эта группа разрядов определяет значения микрокоманд. Группу разрядов Асоставляющую адресный код (А,), поступающий на информа ционный вход блока 5 памяти. В адресной группе разрядов, выбираемой из текущего адреса, указывается адрес следующего микропрограммного слова. Группу разрядов А , поступающую на управляющий вход коммутатора 6 логических условий и указывающую номер коммутирующего канала с целью образования базового адреса блока 8 памяти микропрограмм (А). 55После выполнения процедуры начальной установки нулевое содержимое регистра 7 адреса инициирует выборку 7155 4 содержимого нулевой ячейки блока 8памяти микропрограмм.Нулевой адрес является начальным адресом микропрограммы записи сигналов запросов Х, - Х , поступающих по входам 14 устройства от внешних управляемых абонентов.Содержимое нулевой ячейки блока 8 памяти микропрограмм (в простейшем случае) составляет микрокоманда у и2 единичное (01 ) содержимое группы8разрядов А, .При выборке нулевого слова микропрограммы у по переднему фронту сигнала (, на регистре 9 микрокоманд фиксируется микрокоманда у , котораяй своим передним фронтом заносит на регистр 10 запросов состояние шин Х -1Х, а в нулевую ячейку блока 5 памяти по сигналу Ц, обозначающему для него режим записи, - код О 1Запись информации в нулевую ячейку блока 5 памяти в данном случае будет произведена потому, что блок 11 приоритетной обработки при отсутствии микрокоманды у, стробирующей его работу, будет выдавать на своих выходах нулевую информацию. С выхода блока 11 приоритетной обсработки через правое плечо коммутатора 3 нулевая информация поступаетна адресный вход блока 5 памяти и,следовательно, инициирует запись вячейку блока 5 памяти с нулевым адресом кода О 1,В следующем такте сигналом 0 блок5 памяти переводится в режим чтенияинформации, тогда иэ ячейки с нулевым адресом, как и прежде, задаваемым с блока 11 приоритетной обработки, считывается код 01 з, который через правое плечо коммутатора 4 поступает на информационный вход регистра 7 адреса, где фиксируется по заднему фронту импульсом (По адресу кода 01 з с первой ячейки блока 8 памяти микропрограмм считывается микропрограммное слово, содержащее микрокоманду у, и нулевоезначение группы разрядов АА, = 00Микрокоманда у, фиксируется на регистре 9 микрокоманд передним фронтом сигнала О и с выхода регистра9 микрокоманд поступает на стробирующий (разрешающий) вход блока 11приоритетной обработки,Под действием этого кода (описание работы блока 11 приоритетной об1287155 р 11 бо гк 11 1 ижГ), а таккР в завиГимости от ГИГтоянис рР 1 иГтоя 10 запроГов и регистра 12 маски запросов средствами бл 11 ка 1 приоритетной обработки вь 1 рабатывается код номера запроса (асоие 1 гга), для которого должна быть сформирована соответствуюп 1 ая микропрограмма. Этот код с выхода блока 11 приоритетной обработки, черезправое плечо коммутатора 3 поступает О на адресный вход блока 5 памяти. Под ДРЙствиРм сигнала Оиз ячейки блока 5 памяти с а,цресом Ы считывается информационное слово, в котором программируются микрокоманды неооходи мые для управления абонентом. В этом жР микропрограммном слоне гругпой разрядов Л кс 1 дируется адрес следующего микрокомандного слова. Этот код заносится в ячейку блока 5 памяти с 20 адресом Н, откуца выбирается на следующем:паге. Описанные циклы выборки и записи в блок 5 памяти повторяются до тех пор, пока не будут выбраны все микропрограммные слова да.иной микропрограммы, В после, пнем слове микропрограммы в блоке 5 памяти заносится начальный адрес микропрограммы и снимается микрокоманда уПри отс.утствии микрокоманды у30 блок 11 приоритетной обработки завляется с новым значением сигналовзапросов или их комбинацией, устанавливаемой в нулевом микропрограммномспсве микрокомандой уВ процессе Формирования микропрограмм, требующих ветвления 1 вариантности ) в зависимости от состояния 40признака состояния) управляемогообъекта, с последнего подается сигнал 11 (Фиг.1), отражающий его состояние. Этот сигнал поступает на соответствующий вход (16) коммутатора б 5логических условий,Для управления коммутатором б логических условий в соответствующихмикропрограммных словах, где требуется реакция на состояние управляемого 50объекта, группой разрядов А кодируется (программируется) управляющийкод, который поступает на управл 1 яющий вхо,ц коммутатора б,Если состояние управляемого объекта характеризуется сигналом 0; =О,управпение передается в ь-й адрес.,если П, =1, то упранление передается в (1111.)-Й адрес, так как на ныхо 1. Микропрограммное устройство уп равления, содержащее блок памяти адресов микропрограмм, регистр адреса,блок памяти микропрограмм, регистрмикрокоманд, ГРИРратор имт 1 уи 1 сов,первый выхол ко 1 в 1 просов выдает на своем выходе нулевой код и описанный процесс возобноде коммутатора 6 лс 1 гических условий появится единица, которая будет подана на базовый адрес блока 8 памяти микропрограмм,Работа устройства при обработкезапросов закл 1 очается в следующем.На входы 14 устройства подаютсяпотенциальные сигналы Х - Х по 3ступающие на -информационный вход регистра 1 О запросов. Эти сигналы обозначают требование абонента сформировать для него соответствующую микропрограмму. С помощью микропрограммы у и по ее переднему фронту этисигналы заносятся в регистр 10 запросов.В регистр 12 маски запросов наэтапе начального сброса заноситсякод маски, который разрешает обработку соответствующего (или соответствующих)запроса.Вырабатываемая н процессе реализации соответствующих микропрограмммикрокоманда у поступает на входтриггера 20, где фиксируется передним Фронтом сигнала 0 , поступающего с генератора 1 импульсов, а навыходе Я триггера 22 формируетсясигнал высокого уровня, стробирующийработу элемента И 21.Сама схема соединения элементовИ 21 говорит о том, что каждый предыдущий элемент И запрещает работупоследующего, т.е, элемент И 21,расположенный слева и разрешенныйсигналом от регистра 12 маски запросов, имеет преимущественный приоритет над остальными.Выходы всех элементов И 21 образуют адрес, который через правое плечо коммутатора 3 поступает на адресный вход блока 5 памяти.Блок 5 памяти имеет два рабочихрежима: запись информации, поступающей на информационный вход, определяется сигналом О,; чтение информации соответствующей ячейки, адрес которой зафиксирован на адресном входе;чтение информации из блока 5 памятипроизводится сигналом О2 Формула изобретениядом записи блока памяти адресов микропрограмм и входом записи регистрамикрокоманд, второй выход генератораимпульсов соединен с входом чтенияблока памяти адресов микропрограмми входом записи регистра адреса, выходы которого соединены с входамистарших разрядов адреса блока памятимикропрограмм, выход поля микрокоманды которого соединен с информационны- Оми входами регистра микрокоманд, выходы поля микроопераций которого соединены с выходами устройства, о тл и ч а ю щ е е с я тем, что, сцелью расширения области применения 15устройства за счет реализации приоритетного обслуживания запросов объектов управления, введены регистр запросов, регистр маски запросов, блокприоритетной обработки, триггер,элемент задержки, коммутатор логическихусловий и два коммутатора, выходы которых соответственно подключены к адресному входу блока памяти адресовмикропрограмм и к информационному вхо ду регистра адреса, выход которогосоединен с первым информационным входом первого коммутатора, второй информационный вход которого соединенс выходом блока приоритетной обработ- ЗОки, информационный и синхронизирующий входы триггера соединены соответственно с входом сброса устройства и вторым выходом генератора импульсов, информационные входы регистра запросов соединены с входами запросов на управление устройства, входзаписи регистра запросов соединен спервым выходом поля логических условий регистра микрокоманд, второй выход поля логических условий котоогосоединен с управляющим входом блокаприоритетной обработки, синхронизирующий вход которого соединен с вторым выходом генератора импульсов, 45первая и вторая группы информационных входов блока приоритетной обработки соединены соответственно с группами выходов регистра запросов и регистра маски запросов информационный вход регистра маски запросов ипервый информационный вход второгокоммутатора соединены с входами коданачальной установки, второй информационный вход которого соединен с выходом блока памяти адресов микропрограмм, выход поля адреса микрокомандыблока памяти микропрограмм соединенс информационным входом блока памятиадресов микропрограмм, третий выходполя логических условий регистра микрокоманд соединен с управляющим входом коммутатора логических условий,информационные входы которого соединены с входами логических условийустройства, а выход коммутатора подключен к входу младшего разряда адреса блока памяти микропрограмм, синхронизирующий вход регистра маски запросов соединен с входом синхронизации устройства, прямой выход триггера подключен к первым управляющимвходам первого и второго коммутаторов, к входу установки в О регистра запросов и через элемент задержки - к входам установки в "О" регистра микрокоманд и регистра адреса, инверсный выход триггера соединен сВторыми управляющими входами первогои второго коммутаторов,2. Устройство по п.1, о т л ич а ю щ е е с я тем, что блок приоритетной обработки содержит и (иколичество входов запросов) элементов И и триггер, информационный исинхронизирующий входы которого соединены с управляющим входом и входомсинхронизации блока, выход триггерасоединен с первыми входами и элементов И, вторые входы которых соединены с первой группой информационныхвходов блока, третьи входы элементов И соединены с второй группой информационных входов блока, выход-го (=1, и) элемента И соединенс инверсными входами с (+1)-го поп-й элементов И, выходы элементов Исоединены с выходами блока.От регислР сна гапросоРФцг Г код геиераода цмпупьВыход Р щрцегера Дпцтепьностбкода м 1Сцгнап он Состояние рееистра адре аоод длою памяти ми- кропрограмм 12873 55Ьдрегисщра дпросй Ю1287155Составитель А.АфанасьевРедактор Ю.Середа Техред Л.Олейник Корректор М,Пожо Заказ 7718/52 Тираж 694 Подписное ВНИИПИ Государственного комитета СССРпо делам изобретений и открытий113035, Москва, Ж, Раушская наб д. 4/5 Производственно-полиграфическое предприятие, г.ужгород,ул,Проектная,4

СмотретьЗаявка

3897335, 20.05.1985

ПРЕДПРИЯТИЕ ПЯ А-7162

КРИВЕГО ВЛАДИМИР АЛЕКСАНДРОВИЧ, ГАЙДАЙ ВЕРА АЛЕКСЕЕВНА, ГЛОНТИ ЕВГЕНИЙ ВЛАДИМИРОВИЧ, КРИВЕГО ВАДИМ ВЛАДИМИРОВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 30.01.1987

Код ссылки

<a href="https://patents.su/8-1287155-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Устройство микропрограммного управления

Следующий патент: Устройство микропрограммного управления

Случайный патент: Трековый детектор