Микропроцессор для управления памятью микрокоманд

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 803700

Авторы: Белоус, Болдырев, Горовой, Кляшторный, Красницкий, Кузьменко, Смолов, Хвощ, Шкроб

Текст

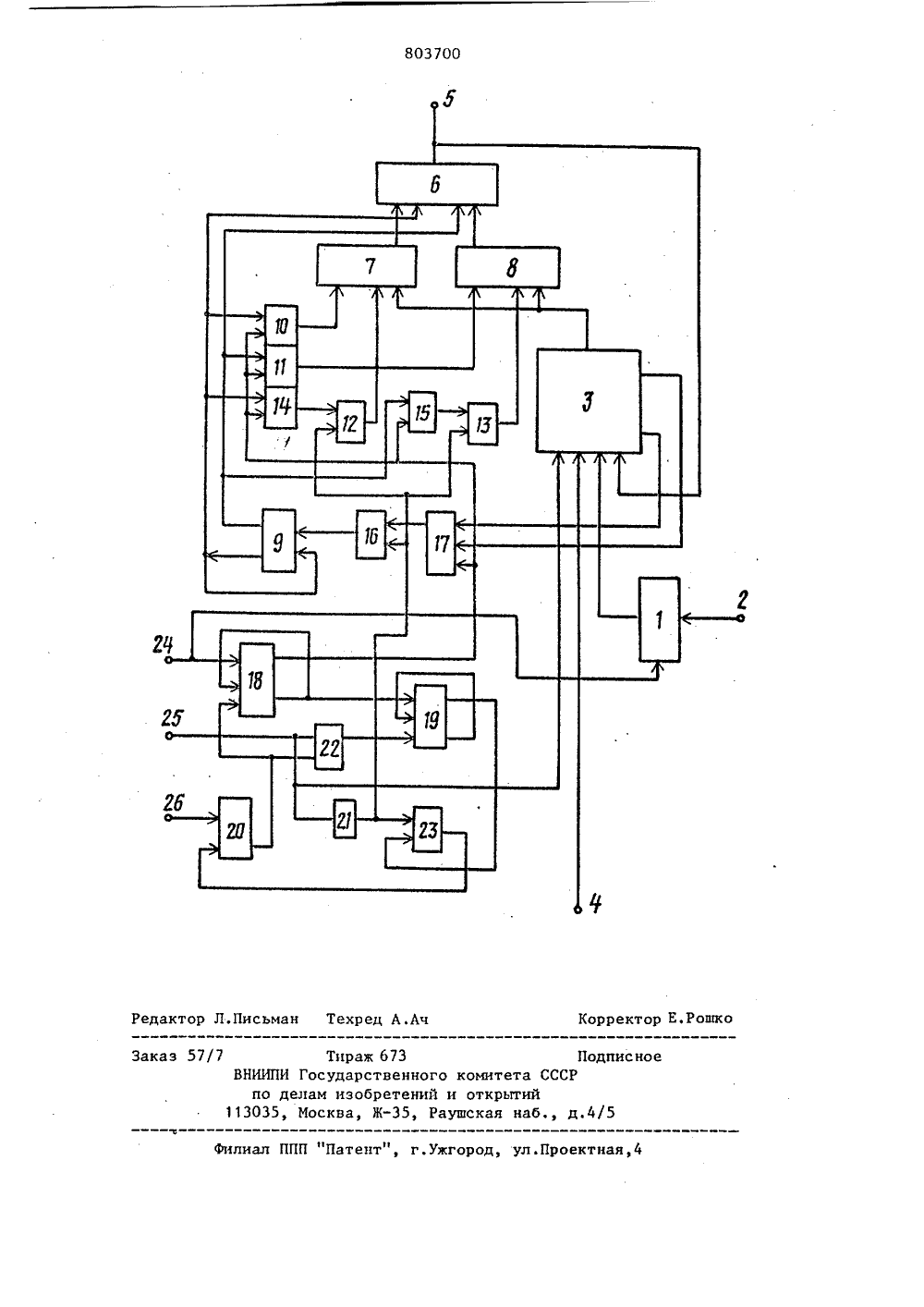

,ЯО б 04 С 06 Р 15 ОПИСАНИЕ ИЗОБРЕТЕНИ АВТОРСКОМУ СВИДЕТЕЛЬСТВУ.Смолов681.325 (088.8)Микропроцессорныйдиодами Шоттки.очные данные, 197кропроцессор дляью микрокоманд. Тние, Ленинград, 1 М.Красницкий,В.В.Горовой,П.Болдырев А.И и В (53 омплект БИСрия К 589,Л правленияхническое79. памя пис ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТ(54)(57) МИКРОПРОЦЕССОР ДЛЯ УПРАВЛЕНИЯ ПАМЯТБЮ МИКРОКОМАНД, содержащий регистр микрокоманд, блок формирования адреса, первый регистр адреса микрокоманд, причем информационный вход регистра микрокоманд соединен с входом микрокоманд микропроцессора, а выход регистра микрокоманд соединен с первым входом блока формирования адреса, второй вход которого соединен с информационным входом микропроцессора, первый выход блока формирования адреса соединен с адресным входом первого регистра адреса макрокоманд, о т л и ч а ю - щ и й с я тем, что, с целью расширения функциональных воэможностей микропроцессора за счет осуществления обработки прерываний на микропрограммном уровне и повышения его быстродействия, в него введены второй регистр адреса микрокоманд,коммутатор, управляющий триггер, элементы И, ИЛИ, НЕ, И-НЕ, два счетных триггера, триггер прерываний, причем выходы первого и второго регистровадреса микрокоманд соединенысоответственно с первым и вторым информационными входами коммутатора, выходкоторого соединен с выходом адресамикропроцессора и третьим входомблока формирования адреса, первыйвыход которого соединен с адреснымвходом второго регистра адреса микрокоманд, прямой выход управляющеготриггера соединен с первыми входамипервых элементов И-НЕ и ИЛИ н первымуправляющим входом коммутатора, инверсный выход управляющего триггерасоединен со своим информационнымвходом и с первыми входами вторыхэлементов И-НЕ и ИЛИ и с вторымуправляющим входом коммутатора, выходы первого и второго элементовИ-НЕ соединены соответственно с входами установки первого и второгорегистров адреса микрокоманд, выходвторого элемента ИЛИ соединен с первым входом третьего элемента И-НЕ,выход которого соединен с синхровходом второго регистра адреса микрокоманд, выход первого элемента ИЛИсоединен с первым входом четвертогоэлемента И-НЕ, выход которого соединен с синхровходом первого регистраадреса микрокоманд, второй и третийвыходы блока формирования адреса соединены с первым и вторым входами третьего элемента ИЛИ соответственно,выход которого соединен с первымвходом первого элемента И, выход которого соединен с синхровходом управляющего триггера, синхровход первогосчетного триггера соединен с входомпервого синхроимпульса микропроцессора и с тактовым входом регистра803700 микрокоманд, прямой выход первого счетного триггера соединен с вторыми входами первых и вторых элементов, И-НЕ и ИЛИ и с третьим входом третьего элемента ИЛИ, инверсный выход первого счетного триггера соединен со своим информационным входом и син. хровходом второго счетного триггера, инверсный выход которого соединен со своим информационным входом, а прямой , выход соединен с первым входом пятого элемента И-НЕ, первый вход второго элемента И соединен с входом элемент а НЕ, с входом второго синхроимпульс,.1 микропроцессора и с четвертымИзобретение относится к областицифровой вычислительной техники, аименно к проектированию цифровых вычислительных машин на основе большихинтегральных, схем (БИС) микропроцесс.оров,Известны микропроцессорные наборыБИС, отличительной чертой которыхявляется наличие микропрограммногоустройства управления, предназначенные для конструирования цифровых вычислительных машин.Общим недостатком БИС БМУ перечисленных серий является невозможностьорганизации обработки запросов напрерывание на микропрограммном уровне.Наиболее близким по техническойсущности к изобретению является микропроцессор для управления памятьюмикрокоманд. 20Микропроцессор для управления памятью микрокоманд содержит: регистрмикрокоманд, вход микрокоманд ШМК,блок формирования адреса, регистрадреса микрокоманд, вход адреса и 25вход синхронизации. К недостаткам известного микро- процес. сора относится невозможность организации прерывания на микропрограммном уровнеотсутствие стекаодля хранения адреса прерванной микро- команды, большое время ожидания на обработку прерывания (на программном уровне) и как следствие, низкбе быст родействие по прерываниям. входом блока формирования адреса, второй вход второго элемента И соединен с входом сброса первого счетного триггера и с инверсным выходом триггера прерываний, а выход второго элемента И соединен с входом сброса второго счетного триггера, выход элемента НЕ соединен с вторыми входами с третьего по пятый элементов И - НЕ и первого элемента И, выход пятого элемента И -НЕ соединен с входом сбросатриггера прерываний, вход уста-новки которого соединен с входом прерываний микропроцессора. ьЦель изобретения - расширение функциональных возможностей микропроцессора за счет осуществления обработкипрерываний на микропрограммном уровне и повьшение его быстродействия. Цель достигается тем, что в микро. процессор для управления памятью микрокоманд введены: второй регистр адреса микрокоманд, коммутатор, управляющий триггер, два счетных триггера, триггеры прерываний, элементы И, ИЛИ, НЕ, И-НЕ, причем выходы первого и второго регистров адреса микрокоманд соединены соответственно с первым и вторым информационными входами коммутатора, выход мультиплексора соединен с выходом адреса микропроцессора и .третьим входом блока формирования адреса, первый выход которого соединен с адресным входом второго регистра адреса микрокоманд; прямой выход управляющего триггера соединен с первыми входами первых элементов И-НЕ и ИЛИ и с первым управляющим входом коммутатора, инверсный выход управляющего триггера соединен со своим информационным входом и с первыми входами вторых элементов И-НЕ и ИЛИ и с вторым управляющим входом коммутатора выходы первого и второго элементов И-НЕ соединены соответственно с входами установки первого и второго регистров адреса микрокоманд, выход второго элемента ИПИ соединен с первым входом третьего элемента И-НЕ, выход которого соединен с синхровходом второго регистра адреса микро- команд, выход первого элемента ИЛИ соединен с первым входом четвертого элемента И-НЕ, выход которого соединен с синхровходом первого регистра адреса микрокоманд, второй и третий выходы блока формирования адреса соединены с первым и вторым входами третьего элемента ИЛИ соответственно, выход которого соединен с первым входом первого элемента И, выход которого соединен с синхровходом управляющего триггера, сицхровход первого счетного триггера соединен с входом первого синхроимпульса микропро-. цессора и с тактовым входом регистра микрокоманд, прямой выход первого счетного трцгтера соединен с вторым входом первых и вторых элементов И-НЕ и ИЛИ и с третьим входом третьего элемента ИЛИ, ггнверсцый выход первого счетного триггера соединен с своим информационным входоми с синхровходом второго счетного триггера, инверсный выход которого соединен с своим информационным входом, а прямой выход соединен с первым входом пятого элемента И-ИЕ, первый вход второго элемента И соединен с входом второго синхроимпульса микропроцессора, с входом элемента НЕ и с четвертым входом блока формирования адреса, второй вход второго элемента И соединен с инверсным выходом триггера прерываний и с входом сброса первого счетного триггера, а выход второго элемента И соединен с входом сброса второго счетного триггера, выход элемента НЕ соединен с вторыми входами с третьего цо пятый элементов И-НЕ и первого элемента И, выход пятого элемента И-НЕ соединен с входом сброса триггера прерываний, вход установки которого соединен с входом прерываний микропроцессора.Блок-схема микропроцессора для управления памятью микрокоманд приведена на чертеже.Микропроцессор для управления памятью микрокоманд содержит регистр 1 микрокоманд, вход 2 микрокоманд,блок 3 формирования адреса, информационный вход 4, выход 5 адреса, коммутатор б, два регистра 7 и 8 адреса микрокомацд, управляющий триггер 9, второй и первый элементы И-НЕ 10 и 11, третий и четвертый элементы И-НЕ 12 и510 15 20 13, второй и первьдг элементы ИЛИ 14 и 5, первый элемент И 16, третий элемент ИЛИ 17, два счетных триггера 18 и 19 триггер прерываний 20, элемент НЕ 21,второй элемент И 22, пятьпг элемент И-НЕ 23, вход 24 первого синхроимпульса, вход 25 второго синхроимпульса и вход 26 прерываний.Микропроцессор для управления памятью микрокоманд работает следующим образом.В нормальном режиме работы (отсутствие запросов на прерывание) счетный триггер 18 находится .в пулевом состоянии и сицхроимпульсы с входа 25 проходят через элемент НЕ 21 и один из элементов И-НЕ 12 или 13 в соответствии с состоянием управляющего триггера 9. Допустим, что управляющий триггер 9 находитсяв единичном состоянии, тогда синхооимпульсы проходят через элемент И-НЕ 13 на регистр адреса микрокоманд 8, коммутатор 6 подключит регистр адреса микрокомацд к выходу адреса 5. Таким образом, текущий адрес с блокаформирования адреса 3 подается ца регистр адреса 8 и на выход адреса 5.В этом случае работа микропроцессорадля управления памятью лпгкрокоманданалогична работе прототипа.Если управляющий триггер 9 находится в нулевом состоянии, то текущий адрес с блока 3 формирования адреса поступает на регистр 7 адреса ина выход 5 адреса. Таким образом,управляющий триггер 9 осуществляетподключение регистров 7 и 8 адресак коммутатору 6 и подачу синхроимпульсов с входа 25 к выбранномурегистру.В режиме запроса на прерываниезапрос поступает по входу 26 прерывания ца вход триггера 20 прерывания иустанавливает его в ноль, при этом 45 со счетного триггера 18 снимаетсясигнал установки и счетньгй триггер18 начинает считать сццхроимпульсы,приходящие по входу 24. По первомусинхроилгпульсу счетцьпг триггер 18устанавливается в единицу. Этот высо.кий потенциал подается на элементыИЛИ 17, 14 и 5, элементы И-НЕ 10, 11и разрешает прохождение сицхронмпульсов с входа 25 через элемент НЕ 55 21, элементы И-НЕ 12 и 13 сразу к адвум регистрам 7 и 8 адреса. По переднему фронту сицхронмпульса, проходящего через элемент НЕ 21 и эле 8037 аомент И 16 управляющего триггера 9, происходит переключение управляющего триггера 9 в другое состояние.Допустим, управляющий триггер 9 находится в нулевом состоянии, т.е, в, работе находится регистр 7 адреса. При проходе синхроимпульса происходит переключение управляющего триггера 9 и к выходу 5 адреса подключает 1 О ся регистр 8 адреса, при этом элемент И-НЕ 11 вырабатывает сигнал установки регистра 8 адреса в единичное состояние и по заднему фронту синхроимпульса адрес с блока 3 формирования5 адреса записьвается в регистр 7 адреса, а регистр 8 адреса устанавливается в единичное состояние и этот адрес выдается на выход 5 адреса. Регистр 8 адреса устанавливается в единицу, не смотря на то, что на его20 информационные входы тоже подан текущий адрес с блока 3 формирования адреса, Это происходит потому, что сигнал установки перебивает информацию на входе. По второму синхроимпульсу с входа 24 счетный триггер 18 устанавливается в ноль и снимается единица элементов И-НЕ 10, 11 и элементов ИЛИ 14, 15 и 17, тем самым открьвая только один путь для прохождения синхроимпульсов с входа 25, а именно, к регистру 8 адреса.Единица с инверсного выхода счетного триггера 18 устанавливает счетный триггер 19 в единичное состоя ние, разрешая синхроимпульсам с входа 25 проходить через элемент И-НЕ 23. Передний фронт синхроимпульса с входа 25, пройдя через элемент НЕ 21 и элемент И-НЕ 23, установит 40 триггер 20 прерываний в единичное состояние. Единица с триггера 20 прерывания будет удерживать счетный триггер 18 в нулевом состоянии, так как подается на вход. По заднему 45 фронту синхроимпульса с входа 25 элемента И 22 счетный триггер 19 уста-,новится в нулевое состояние. При этом счетные триггеры 18,19 и триггер 20 прерываний установятся в исходное состояние.Таким образом происходит следующее.Если мы работали с регистром 7 адреса, то после всего происшедшего в регистре 7 адреса оказался следующий адрес, а с регистра 8 адреса выдался на выход 5 адреса единичный адрес. Значит мы спасли текущий адрес и перешли к начальной ячейке программы обработки прерьвания,В режиме возврата к прерванной программе возврат происходит программно, При этом блок 3 формирования адреса вырабатывает сигнал переключения управляющего триггера 9, который с выхода два или три блока 3 поступает на входы элемента ИЛИ 17 и на элемент И 16. По синхроимпульсу с входа 25 происходит переклю. чение управляющего триггера 9 и к выходу 5 адреса подключается тот регистр адреса, который был отключен, в нашем случае это регистр 7 адреса. С регистра 7 адреса текущий адрес, на котором была прервана программа, поступает на выход 5 адреса и продолжается выполнение прерванной программы.Наличие второго регистра адреса, входа прерываний и схем управления регистрами адреса позволяет организовать прерывание на программном уровне без дополнительных затрат оборудования и времени. Кроме того, при этом не нужно спасать текущий адрес. Это позволяет значительно уменьшить объем программы обработки прерываний и соответственно объемтПЗУ микрокоманд, что выгодно отличает предлагаемый микропроцессор для управления памятью микрокоманд от известных устройств аналогичного назначения.803700 ектор Е.Рошко Редактор Л.Письман Техред А .Ач Тираж 673 ПодписНИИПИ Государственного комитета СССРпо делам изобретений и открытий3035, Москва, Ж, Раушская наб., д.4/5 каз 5 юлиал ППП "Патент", г.ужгород, ул.Проектная,4

СмотретьЗаявка

2846971, 04.12.1979

ПРЕДПРИЯТИЕ ПЯ Р-6155, ЛЕНИНГРАДСКИЙ ЭЛЕКТРОТЕХНИЧЕСКИЙИНСТИТУТ ИМ. B. И. УЛЬЯНОВА, ПРЕДПРИЯТИЕ ПЯ P-6007

КЛЯШТОРНЫЙ М. Ю, КРАСНИЦКИЙ Б. М, ХВОЩ С. Т, КУЗЬМЕНКО Н. Г, ГОРОВОЙ В. В, БЕЛОУС А. И, ШКРОБ В. С, БОЛДЫРЕВ В. П, СМОЛОВ В. Б

МПК / Метки

МПК: G06F 9/46

Метки: микрокоманд, микропроцессор, памятью

Опубликовано: 23.01.1986

Код ссылки

<a href="https://patents.su/5-803700-mikroprocessor-dlya-upravleniya-pamyatyu-mikrokomand.html" target="_blank" rel="follow" title="База патентов СССР">Микропроцессор для управления памятью микрокоманд</a>

Предыдущий патент: Сигнализатор помпажа

Следующий патент: Накопитель для постоянного запоминающего устройства

Случайный патент: Многоканальный преобразователь аналоговой величины в код