Устройство микропрограммного управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1287156

Автор: Ланцов

Текст

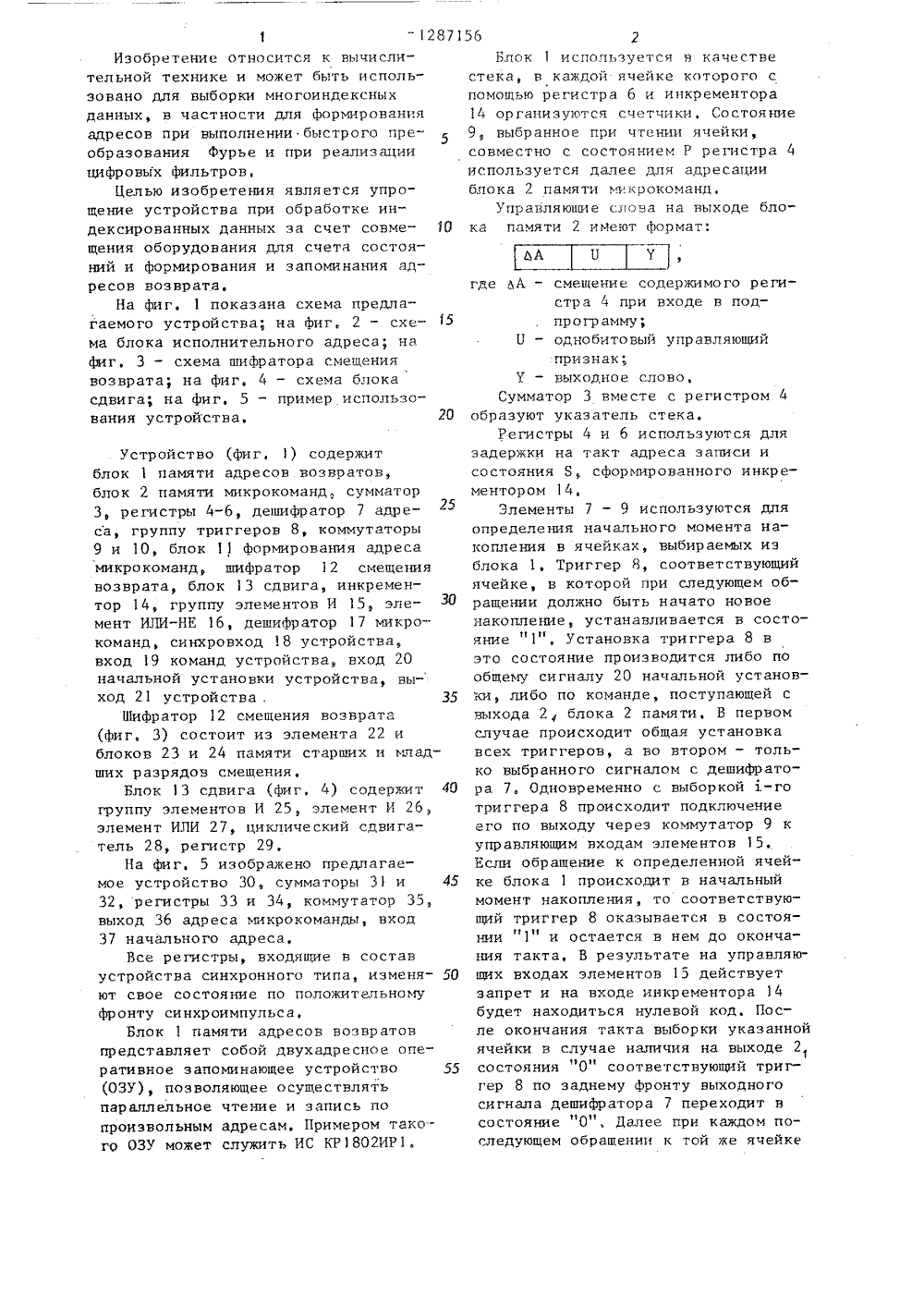

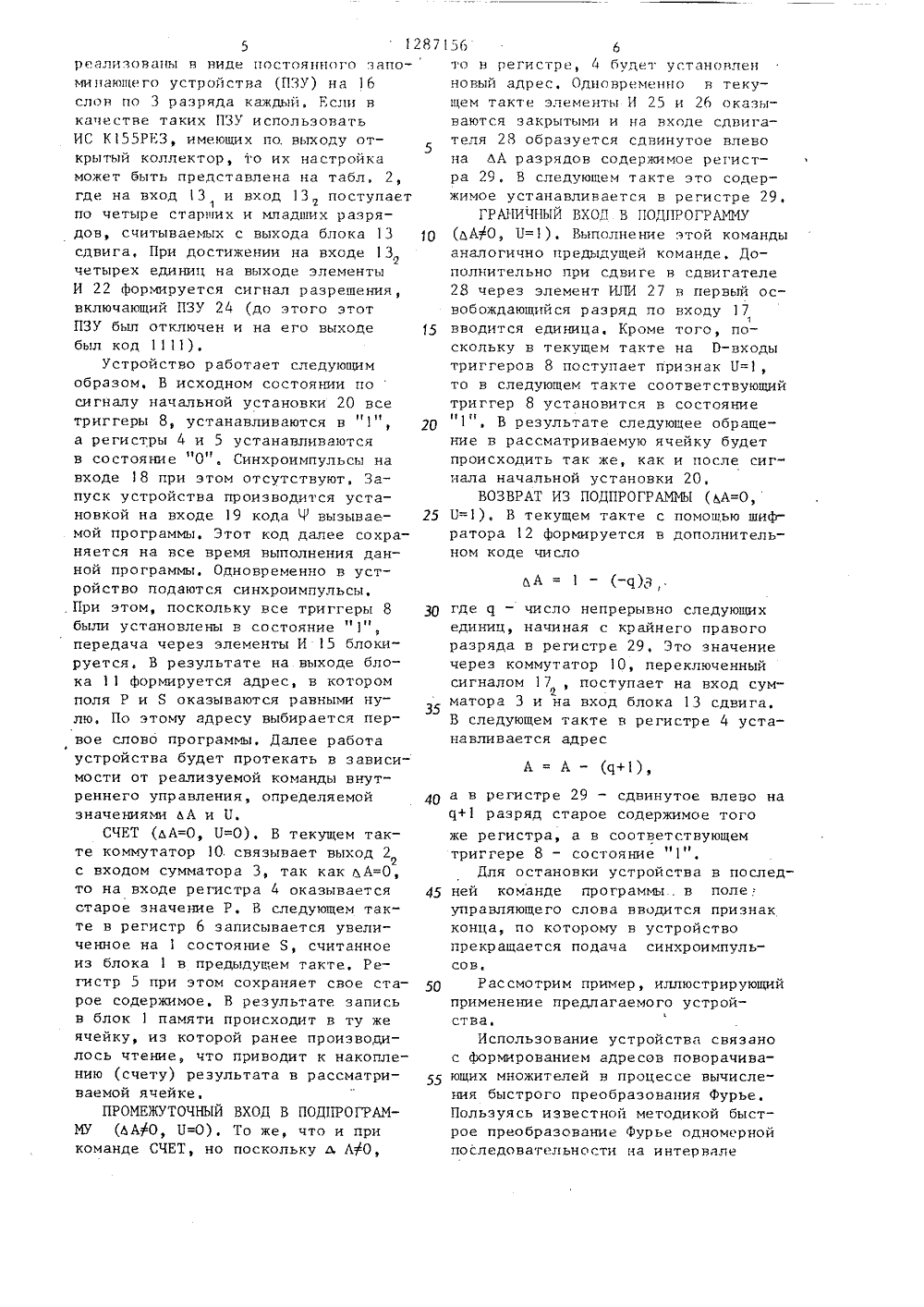

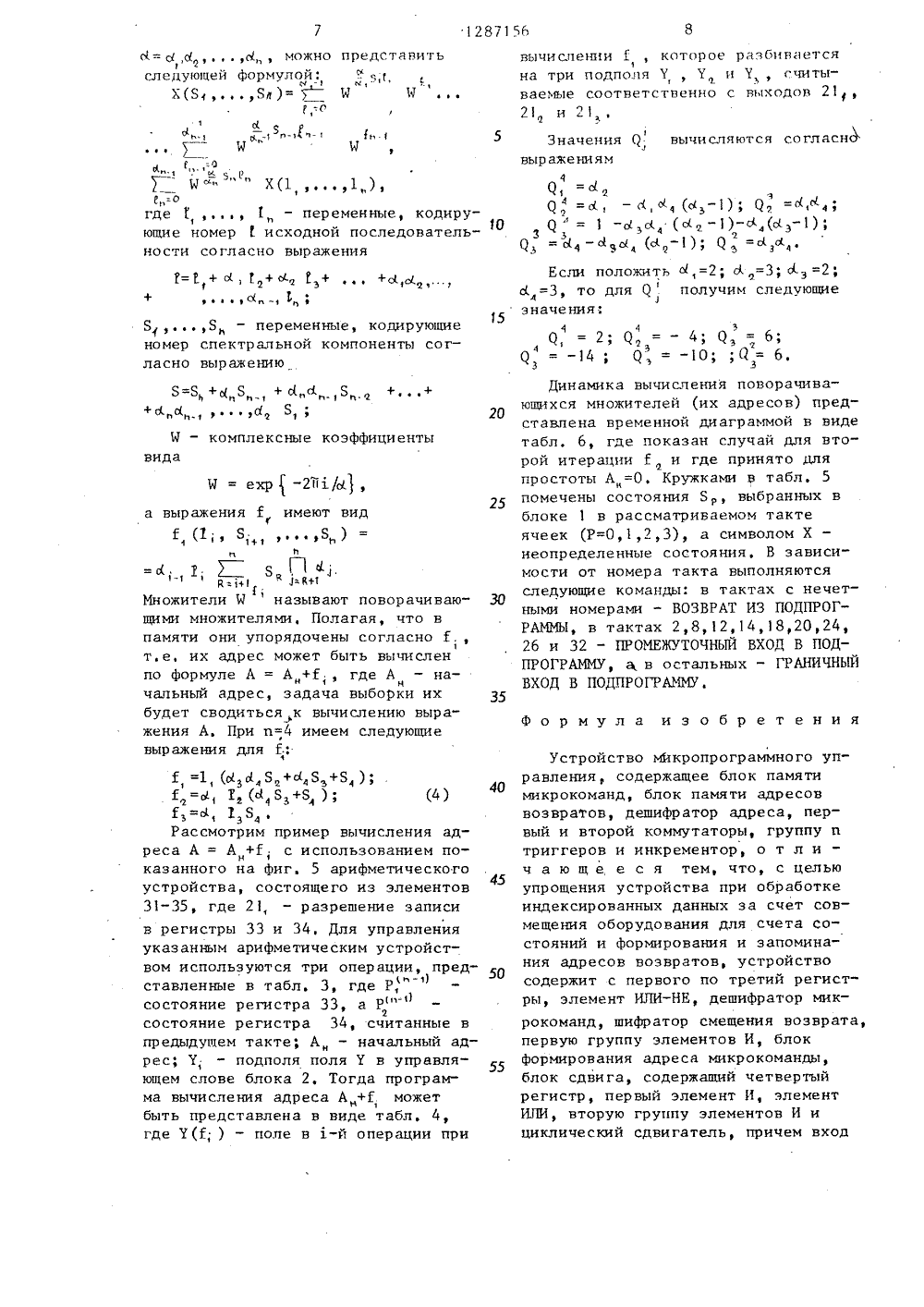

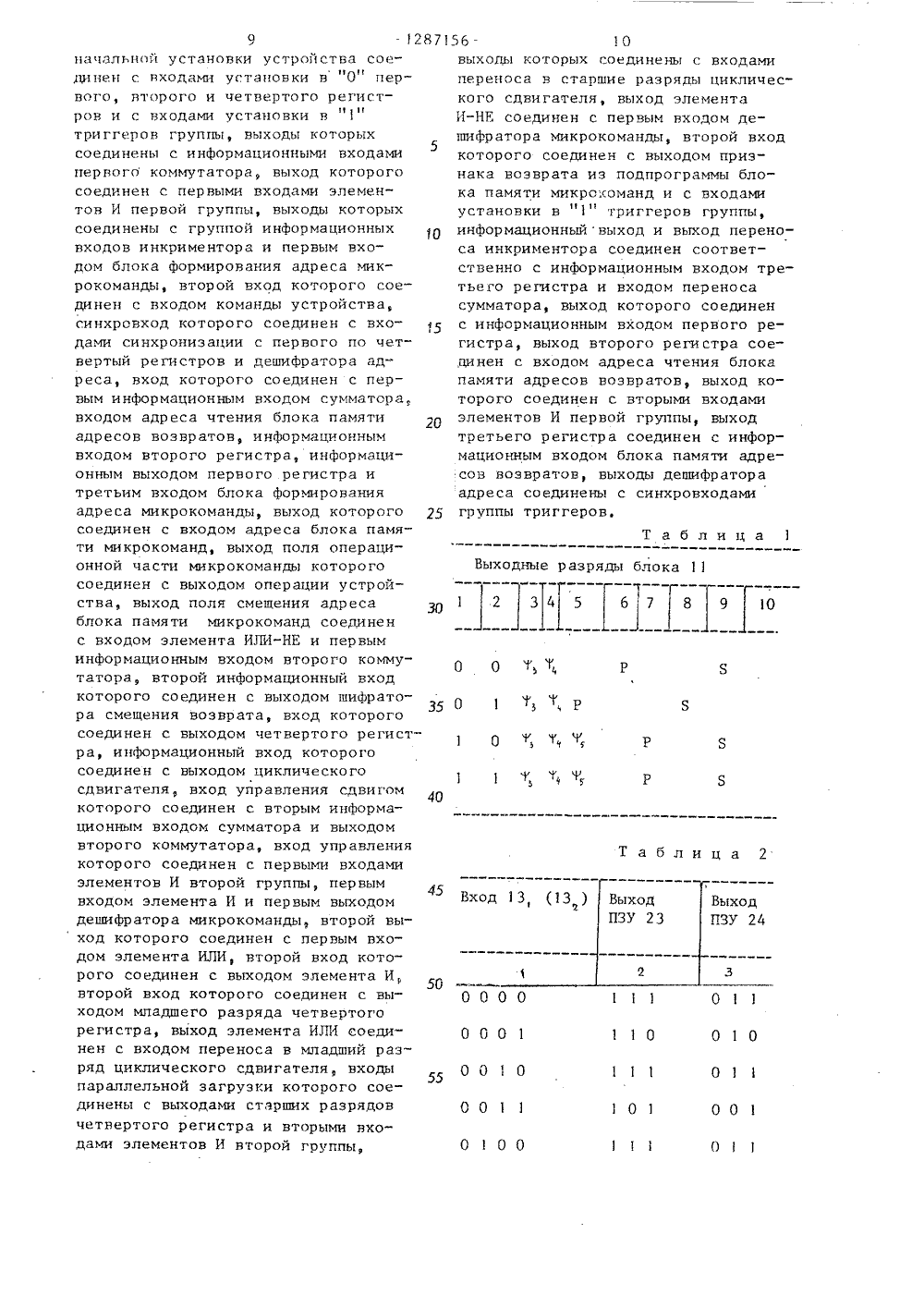

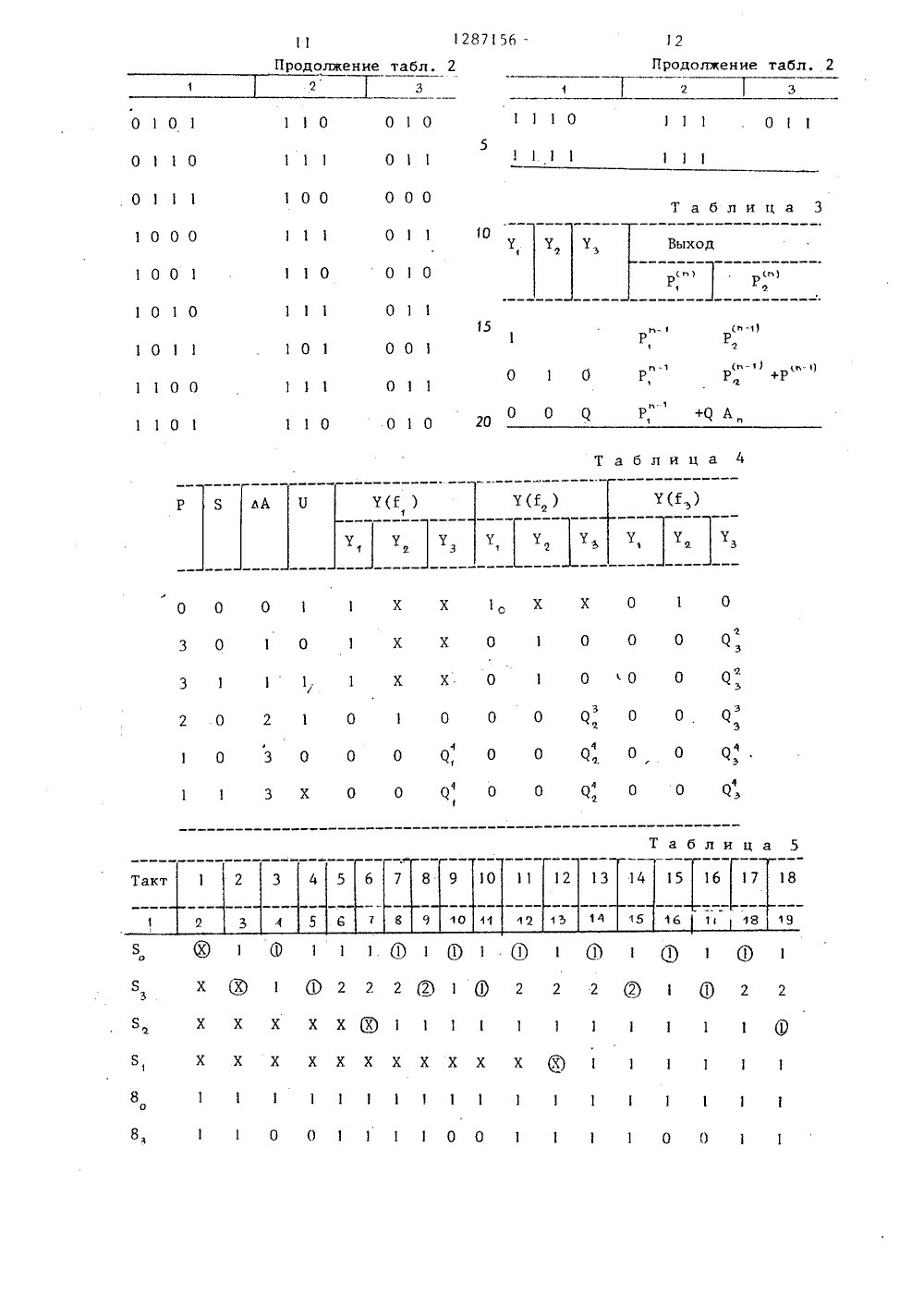

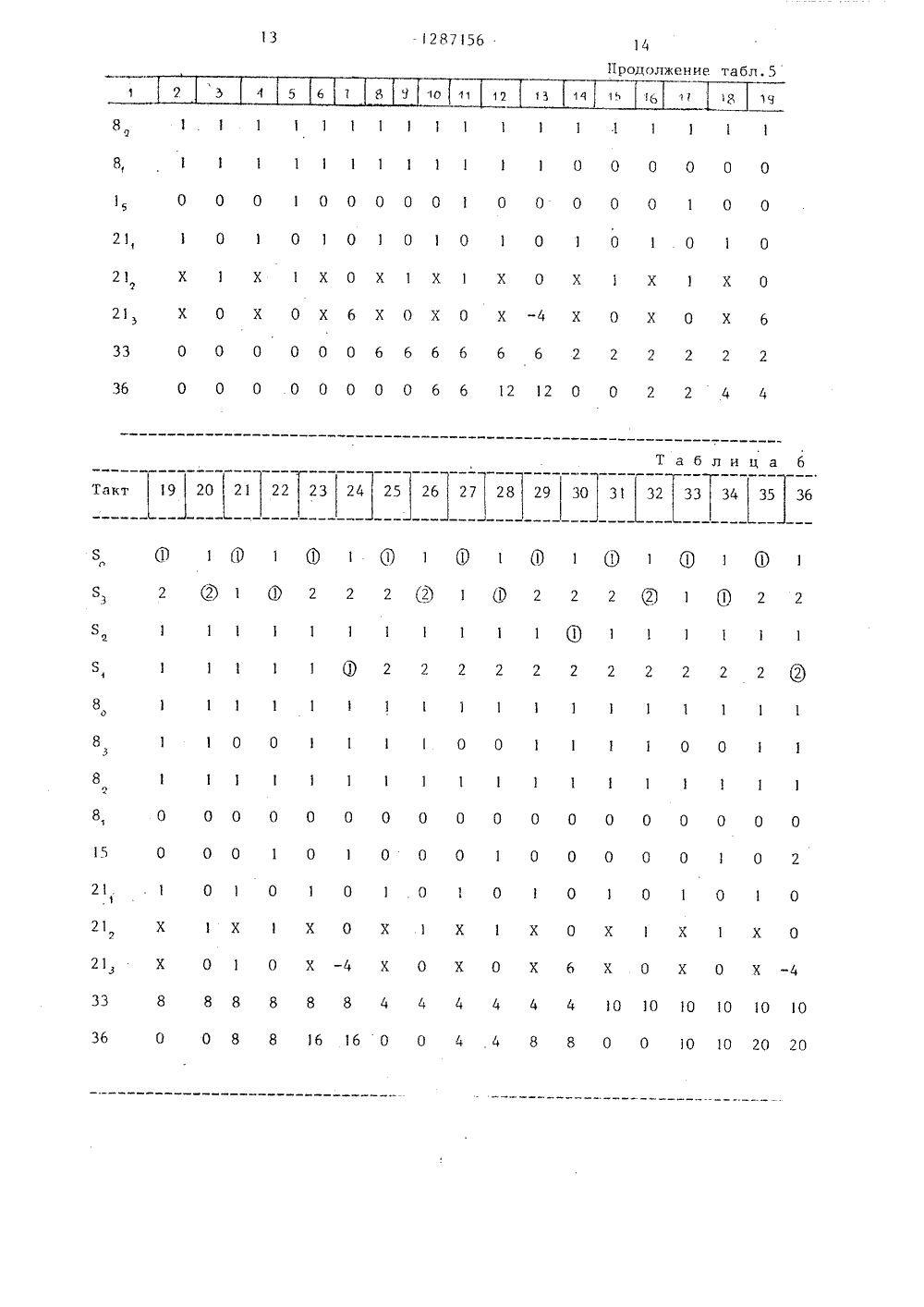

"съ У ГО ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ ОПИСАНИЕ ИЗО К АВТОРСКОМУ СВИДЕТЕЛ(56) Авторское свидетельствво СССР В 807290, кл, С 06 Р 9/22, 1978.Авторское свидетельство СССР Ф 1239715, 1985.(57) Изобретение относится к области вычислительной техники и может быть использовано для выборки многоиндексных данных, в частности, для фор мирования адресов при выполнении быстрого преобразования Фурье. Цель 801287156 А 1 изобретения - сокращение оборудования устройства при обработке индексированных данных путем совмещенияоборудования для счета состояний иформирования и запоминания адресоввозвратов. Устройство содержит блокпамяти адресов возвратов, блок памяти микрокоманд, сумматор, три ре-,гистра, дешифратор адреса, группу итриггеров, два коммутатора, блок формирования адреса микрокоманды, шифратор смещения возврата, блок сдвига, инкрементор, группу элементовИ, элемент ИЛИ - НЕ, дешифратор микрокоманд. Введение трех регистров,дешифратора нулевого смещения, группы элементов И, блока формированияадреса микрокоманды, дешифраторамикрокоманд, формирователя смещениявозврата и блока сдвига обеспечиваетдостижение цели, 5 ил 5 табл.1287156 ставитель А, АфанасьевхредЛ.Олейник Корректор Л. Пнлипен ереда тор Подписиета СССР Заказ 7718/52ВНИИПИ ткрыт 130Тираж 694Государственно о дел ам изобр ет Москва, Ж, Р го комиений иаушская оизводственно-полиграфическое предприятие город, ул, Проектная, 1287Изобретение относится к вычислительной технике и может быть использовано для выборки многоиндексных данных, в частности для формирования адресов при выполнении быстрого пре 5 образования Фурье и при реализации цифровых Фильтров,Целью изобретения является упрощение устройства при обработке индексированных данных за счет совме щения оборудования для счета состояний и формирования и запоминания адресов возврата.На фиг, 1 показана схема предлагаемого устройства; на фнг. 2 - схе ма блока исполнительного адреса; на фиг. 3 - схема шифратора смещения возврата; на фиг. 4 - схема блока сдвига; на Фиг. 5 - пример использования устройства. 20 Устройство (фиг. 1) содержитблок 1 памяти адресов возвратов,блок 2 памяти микрокоманд, сумматор3, регистры 4-6, дешифратор 7 адреса, группу триггеров 8, коммутаторы9 и 10, блок 11 формирования адресамикрокоманд, шифратор 12 смещениявозврата, блок 13 сдвига, инкрементор 14, группу элементов И 15, эле- -фмент ИЛИ-НЕ 16, дешифратор 17 микрокоманд, синхровход 18 устройства,вход 19 команд устройства, вход 20начальной установки устройства, выход 21 устройства . 35Шифратор 12 смещения возврата(фиг, 3) состоит из элемента 22 иблоков 23 и 24 памяти старших и младших разрядов смещения,Блок 13 сдвига (Фиг. 4) содержит 40группу элементов И 25, элемент И 26,элемент ИЛИ 27, циклический сдвигатель 28, регистр 29,На Фиг. 5 изображено предлагаемое устройство 30, сумматоры 31 и 4532, регистры 33 и 34, коммутатор 35,выход 36 адреса микрокоманды, вход37 начального адреса.Все регистры, входящие в составустройства синхронного типа, изменяют свое состояние по положительномуфронту синхроимпульса,Блок 1 памяти адресов возвратовпредставляет собой двухадресное оперативное запоминающее устройство 55(ОЗУ), позволяющее осуществлятьпараллельное чтение и запись попроизвольным адресам, Примером такого ОЗУ может служить ИС КР 1802 ИР 1. 156 2Блок 1 используется н качестве стека, в каждой ячейке которого с помощью регистра 6 и инкрементора 14 организуются счетчики. Состояние 9, выбранное при чтении ячейки, совместно с состоянием Р регистра 4 используется далее для адресации блока 2 памяти макрокоманд.Управляющие слова на выходе блока памяти 2 имеют формат:где 6 А - смещение содержимого регистра 4 при входе в подпрограмму;П - однобитовый управляющийпризнак;У. - выходное слово,Сумматор 3 вместе с регистромобразуют указатель стека,Регистры 4 и 6 используются длязадержки на такт адреса записи исостояния Я, сформированного инкрементором 14,Элементы 7 - 9 используются дляопределения начального момента накопления в ячейках, выбираемых изблока 1, Триггер 8, соответствующийячейке, в которой при следующем обращении должно быть начато новоенакопление, устанавливается в состо -яние "1", Установка триггера 8 вэто состояние производится либо пообщему сигналу 20 начальной установки, либо по команде, поступающей свыхода 2 блока 2 памяти, В первомслучае происходит общая установкавсех триггеров, а во втором - только выбранного сигналом с дешифратора 7. Одновременно с выборкой д-готриггера 8 происходит подключениеего по выходу через коммутатор 9 куправляющим входам элементов 15,Если обращение к определенной ячейке блока 1 происходит в начальныймомент накопления, то соответствующий триггер 8 оказывается в состоянии "1" и остается в нем до окончания такта, В результате на управляюпжх входах элементов 15 действуетзапрет и на входе инкрементора 14будет находиться нулевой код, После окончания такта выборки указаннойячейки в случае наличия на выходе 2состояния чОп соответствующий триггер 8 по заднему фронту выходногосигнала дешифратора 7 переходит всостояние 0, Далее при каждом последующем обращении к той же ячейке128713триггер 8 будет оставаться в состоянии "0" пока вновь не поступит сигнал входа 20 начальной установкиили состояние 1 на выходе 2Блок 11 формирования адреса микро 5команды предназначен для формирования из кода Ч программы, поступающего на вход 19, состояния Р регистра 4 и состояния 3 ячейки,выбранной в блоке 1, адреса чтения 10в блоке 2, В табл, 1 приведен пример получения адреса микрокоманды,где каждая строка представляет собой определенный адресный формат,Из данных табл. 1 видно, что первые 15два разряда Р и 9 образуют первые2два разряда адреса и задают разрядность компонент Р и Б считываемыхсоответственно с регистра 4 и блока 1, В результате достигается более 20полное использование памяти в блоке2 в зависимости от диапазонов изменения Р и Б, Например, если глубинавложения подпрограмм равна треммаксимальное число управляющих слов 25в каждой из подпрограмм не превышает семи, что наиболее полно памятьбудет использована в программе с Ч =1;Ч =1, Если же указанную программупоместить в область памяти с Ф =0З 0Ч = О, то по крайней мере 32 ячейки окажутся неиспользованными,Элементы 12 и 13 используют дляорганизации возврата иэ подпрограммы и служат для формирования необходимого смещения относительно содержимого регистра 4. В. отличие оттрадиционного возврата, сводящегосяк изменению на единицу указателястека адресов возврата, т,е. использованию фиксированного смещения, равного единице, здесь возможно получение сквозного возврата через рядвложенных друг в друга подпрограмм,если в каждой из них последней командой служит команда перехода на подпрограмму. В этом случае адресноесмешение оказывается равным длинесквозного перехода. Для обеспечениятакого перехода используется блок 13 50сдвига, который управляется следующим образом,При входе в подпрограмму, длякоторой смещение адреса в регистре4 должно быть равно 6 А производится сдвиг в блоке 13 влево на А Аразрядов. В освобождающиеся разрядыпри этом вводятся нулиЕсли входв подпрограмму производится в последней команде внешней подпрограммы то на месте первого (младшего) освобождающегося разряда в блок 13 вводится единица, а на место последующих разрядов - нули, При возврате из подпрограммы с помощью формирователя 12 анализируется число непрерывно следующих на выходе сдвигателя единиц, начиная с крайнего правого разряда, Если число таких единиц равно ц то производится сдвиг содержимого блока 13 сдвига на ц+1 разряд вправо, Например, если исходное состояние в блоке 13 имеет виД00110100,то при входе в подпрограмму по промежуточной команде со смещением А=1 получаем следующее выходное состояние блока 13 сдвигаО 1 1 0 1 О 0 О, (1) а при входе по последней команде -О 11 О 1 ОО 1(2)Тогда возврат из подпрограммы, находящейся в состоянии (1), будет сводиться к сдвигу вправо на один разряд00110100,а при возврате из состояния (2) - ксдвигу вправо на два разряда00011010.Блок 13 сдвига выполнен в виде параллельного регистра 29 и циклического сдвигателя, 28, что позволяет обеспечить выполнение произвольного сдвига за один такт, Для упрощения схемы сдвигателя 28 последнее реализует сдвиги только в одну сторону - влево, Сдвиг вправо на и разрядов заменяется циклическим сдвигом на и-ц разрядов, где и - разрядность регистра 29При этом выбор обычного или циклического сдвигов осуществляется путем управления цепью циклического переноса с помощью группы элементов И 25 и элемента И 26, Ввод единицы при входе в подпрограмму по последней команде производится через элемент ИЛИ 27, Дпя вычисления требуемого смещения при возврате из подпрограммы используется формирователь 12, На фиг, 3 показан пример выполнения блока 12 для случая п=8 в виде двухступенчатого формирователя, где блоки 23 и 24 могут быть12871реализованы в ниде постоянного запоми нающе го устройства (ПЗУ) на 1 бслов по 3 разряда каждый, Если вкачестве таких ПЗУ использоватьИС К 155 РЕЗ, имеющих по. выходу от -крытый коллектор, то их настройкаможет быть представлена на табл, 2,где на вход 13 и вход 13 поступаетпо четыре старших и младших разря -дов, считываемых с выхода блока 13 рсдвига, При достижении на входе 13четырех единиц на выходе элементыИ 22 Формируется сигнал разрешения,включающий ПЗУ 24 (до этого этотПЗУ был отключен и на его выходе 5был код 1111),Устройство работает следующимобразом. В исходном состоянии посигналу начальной установки 20 всетриггеры 8, устанавливаются в "1", 20а регистры 4 и 5 устанавливаютсяв состояние 0, Синхроимпульсы навходе 18 при этом отсутствуют, Запуск устройства производится установкой на входе 19 кода Ч вызываемой программы. Этот код далее сохраняется на все время выполнения данной программы. Одновременно в устройство подаются синхроимпульсы,, При этом, поскольку все триггеры 8 Зрбыли установлены в состояние "1",передача через элементы И 5 блокируется, В результате на выходе блока 1 1 Формируется адрес, в которомполя Р и Я оказываются равными нулю, По этому адресу выбирается первое слово программы, Далее работаустройства будет протекать в зависимости от реализуемой команды внутреннего управления, определяемой 4 рзначениями ьА и П,СЧЕТ (лА=О, У=О), В текущем такте коммутатор 10. связывает выход 22с входом сумматора 3, так как ьА=О,то на входе регистра 4 оказываетсястарое значение Р, В следующем такте в регистр 6 записывается увеличенное на 1 состояние Б, считанноеиз блока 1 в предыдущем такте, Регистр 5 при этом сохраняет свое старое содержимое, В результате записьв блок 1 памяти происходит в ту жеячейку, из которой ранее производилось чтение, что приводит к накоплению (счету) результата в рассматриваемой ячейке,ПРОМЕЖУТОЧНЫЙ ВХОД В ПОДПРОГРАММУ (ЛАО, 11=0). То же, что и прикоманде СЧЕТ, но поскольку ь АО,56 6то н регистре, 4 будет установленновый адрес, Одновременно в текущем такте элементы И 25 и 26 оказываются закрытыми и на входе сдвигателя 28 образуется сдвинутое влевона ЬА разрядов содержимое регистра 29, В следующем такте это содержимое устанавливается в регистре 29,ГРАНИЧНЫЙ ВХОД В ПОДПРОГРАММУ(ААО, 0=1), Выполнение этой командыаналогично предыдущей команде, Дополнительно при сдвиге в сдвигателе28 через элемент ИЛИ 27 в первый освобождающийся разряд по входу 171вводится единица, Кроме того, поскольку в текущем такте на р-входытриггеров 8 поступает признак 0=1,то в следующем такте соответствующийтриггер 8 установится в состояние"1", В результате следуюцее обращение в рассматриваемую ячейку будетпроисходить так же, как и после сигнала начальной установки 20,ВОЗВРАТ ИЗ ПОДПРОГРАММЫ (А=О,0=1), В текущем такте с помощью шифратора 12 Формируется в дополнительном ходе числоА = 1 - (-с ) Ргде и - число непрерывно следующих единиц, начиная с крайнего правого разряда в регистре 29. Это значение через коммутатор О, переключенный сигналом 17 , поступает на вход сумматора 3 и на вход блока 13 сдвига. В следующем такте в регистре 4 устанавливается адресА = А - (ч+1),а в регистре 29 - сдвинутое влево нас+ разряд старое содержимое тогоже регистра, а в соответствующемтриггере 8 - состояние "1",Для остановки устройства в последней команде программы . в поле:управляющего слова вводится признакконца, по которому в устройствопрекращается подача синхроимпульсов,Рассмотрим пример, иллюстрирующийприменение предлагаемого устройства.Использование устройства связанос Формированием адресов поворачивающих множителей в процессе вычисления быстрого преобразования Фурье,Пользуясь известной методикой быстрое преобразование Фурье одномернойпоследовательности на интервале10 56 Т аблица 1 9 1 О Т абл 2 ВыходПЗУ 24 500000 1 1 1 001 110 111 О О 0 1 1 0 9 . 12871 цачальцой установки устройства сое 11 ди цец с входами угтацовки в 0 перного, второго и четвертого регист 1 11 ров и с входами установки втриггеров группы, выходы которых5 соединены с информационными входами первого коммутатора, выход которого соединен с первыми входами элементов И первой группы, выходы которых соединены с группой информационных входов инкриментора и первым входом блока формирования адреса микрокоманды, второй вход которого соединен с входом команды устройства, сицхровход которого соединен с входами синхронизации с первого по четвертый регистров и дешифратора адреса, вход которого соединен с первым информационным входом сумматора, входом адреса чтения блока памяти адресов возвратов, информационным входом второго регистра, информационным выходом первого регистра и третьим входом блока формирования адреса микрокоманды, выход которого соединен с входом адреса блока памяти микрокоманд, выход поля операционной части микрокоманды которого соединен с выходом операции устройства, выход поля смещения адреса 30 блока памяти микрокоманд соединен с входом элемента ИЛИ-НЕ и первым информационным входом второго коммутатора, второй информационный вход которого соединен с выходом шифратора смещения возврата, вход которого соединен с выходом четвертого регистра, информационный вход которого соединен с выходом циклического сдвигателя, вход управления сдвигом которого соединен с вторым информационным входом сумматора и выходом второго коммутатора, вход управления которого соединен с первыми входами элементов И второй группы, первым входом элемента И и первым выходом дешифратора микрокоманды, второй выход которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом элемента И, второй вход которого соединен с выходом младшего разряда четвертого регистра, выход элемента ИЛИ соединен с входом переноса в младший разряд циклического сдвигателя входы параллельной загрузки которого соединены с выходами старших разрядов четвертого регистра и вторыми входами элементов И второй группы,выходы которых соединены с входамипереноса в старшие разряды циклического сдвигателя, выход элементаИ-НЕ соединен с первым входом дешифратора микрокоманды, второй входкоторого соединен с выходом признака возврата из подпрограммы блока памяти микрокоманд и с входамиустановки в "1" триггеров группы,информационныйвыход и выход переноса инкриментора соединен соответственно с информационным входом третьего регистра и входом переносасумматора, выход которого соединенс информационным входом первого регистра, выход второго реги стра соецинен с входом адреса чтения блокапамяти адресов возвратов, выход которого соединен с вторыми входамиэлементов И первой группы, выходтретьего регистра соединен с информационным входом блока памяти адресов возвратов, выходы дешифратораадреса соединены с синхровходамигруппы триггеров,Выходные разряды блока 11 1 2 3 4 5 6 7 8 0 0 з "4 Р

СмотретьЗаявка

3908279, 17.06.1985

СПЕЦИАЛЬНОЕ КОНСТРУКТОРСКО-ТЕХНОЛОГИЧЕСКОЕ БЮРО ФИЗИКО МЕХАНИЧЕСКОГО ИНСТИТУТА ИМ. Г. В. КАРПЕНКА

ЛАНЦОВ АЛЕКСАНДР ЛАВРЕНТЬЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммного

Опубликовано: 30.01.1987

Код ссылки

<a href="https://patents.su/10-1287156-ustrojjstvo-mikroprogrammnogo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство микропрограммного управления</a>

Предыдущий патент: Микропрограммное устройство управления

Следующий патент: Устройство для управления запуском программ

Случайный патент: Разнога для посадки туши на подвесной путь