Система передачи и приема цифровых сигналов с обнаружением ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1221759

Автор: Сафаров

Текст

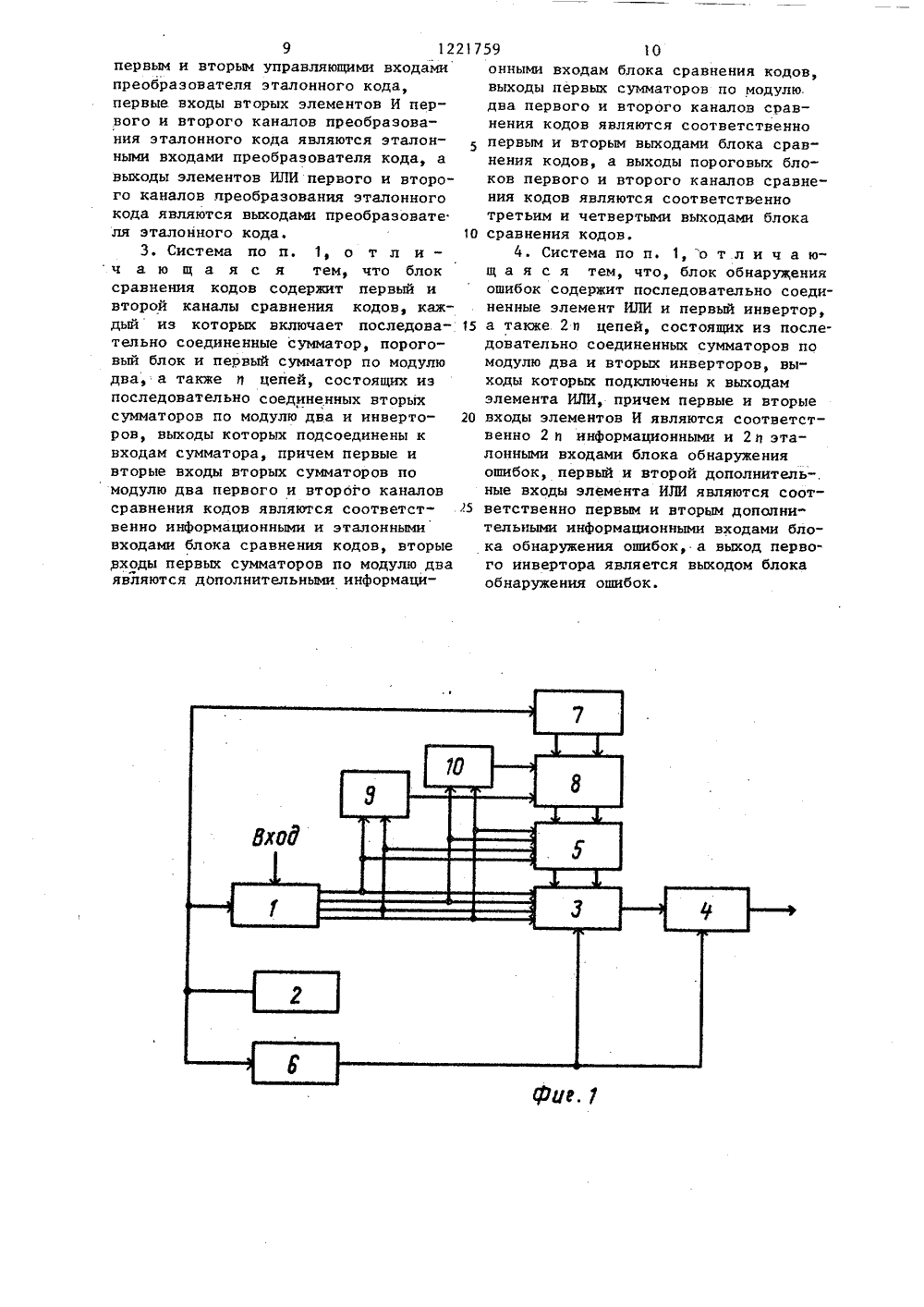

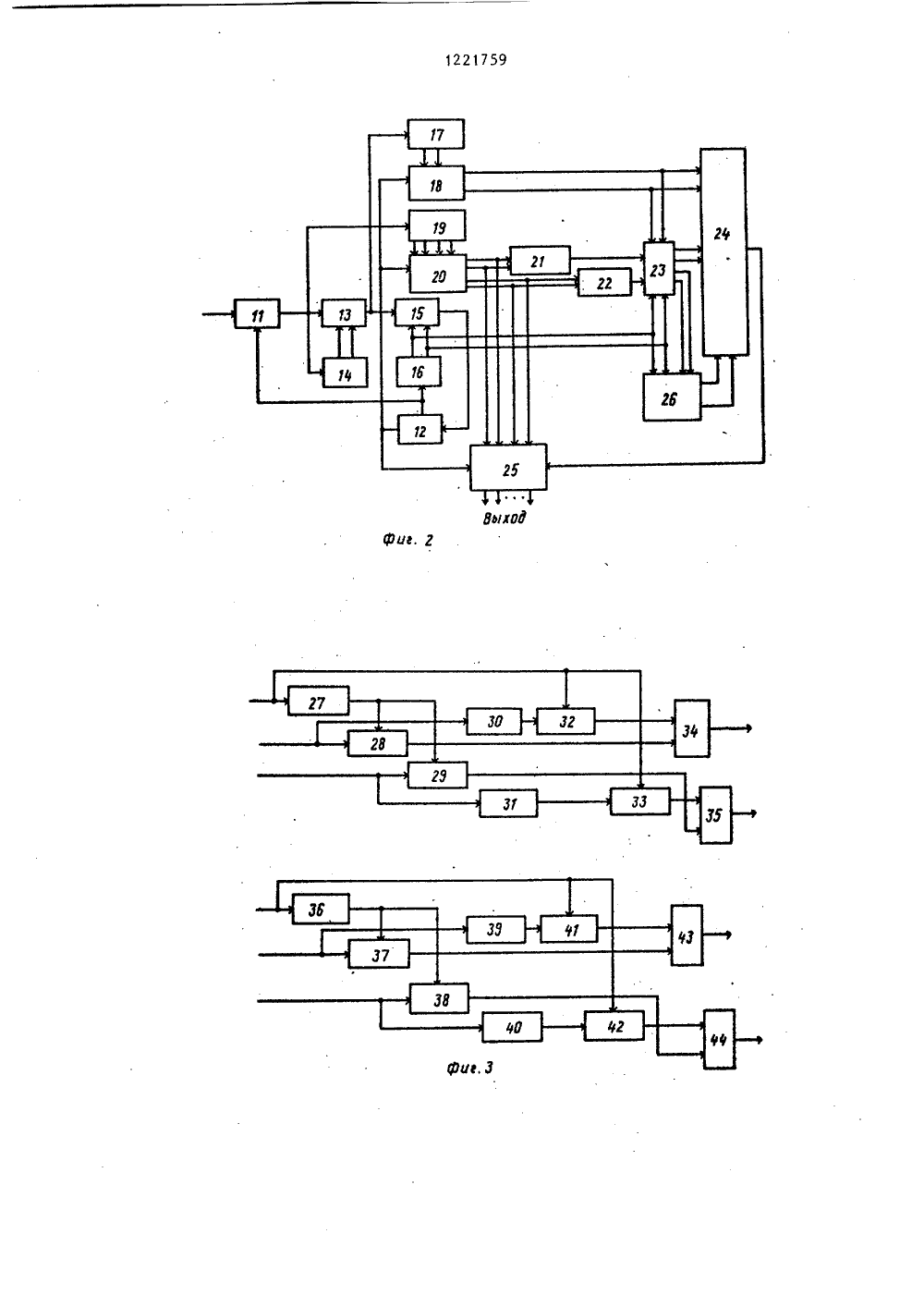

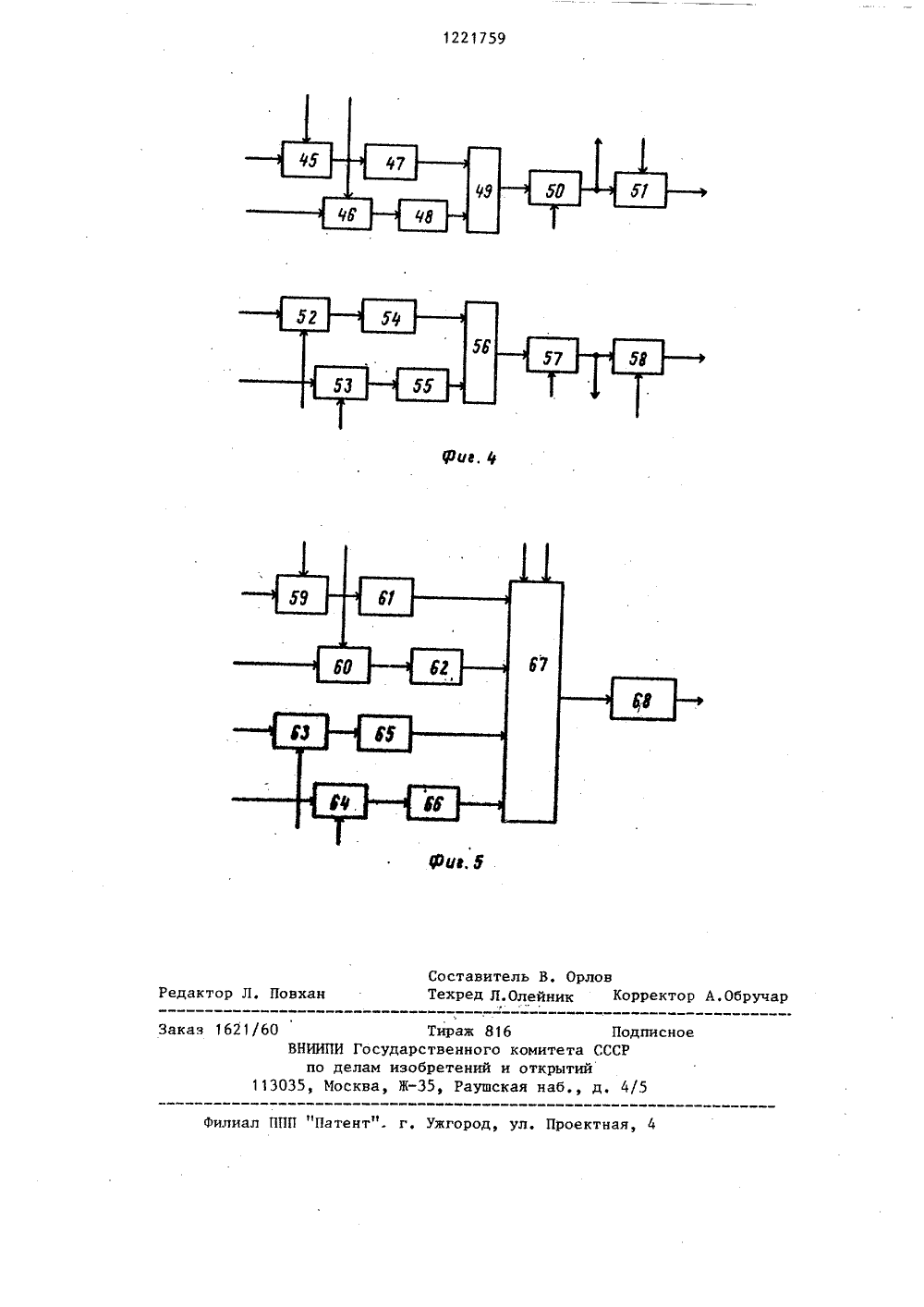

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИРЕСПУБЛИК 119) 4 НОЗМ 13/ ИСАНИЕ ИЗОБРЕТЕНИЯ КА СКОМУ СВИДЕТЕ В Св ОСУДАРСТВЕННЫЙ КОМИТЕТ ССПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИ(7 1) Ленинградский электротехнический институт связи им.проф. М.А. Бонч- Бруевича(56) Шляпоберский В.И. Основы техники передачи дискретных сообщений, М.:язь, 1973, с. 318-320.Авторское свидетельство СССР Ф 1123111, кл, Н 04 Ь 1/10, 1982. (54) СИСТЕМА ПЕРЕДАЧИ И ПРИЕМА ЦИФРОВЫХ СИГНАЛОВ С ОБНАРУЖЕНИЕМ ОШИБОК (57) Изобретение относится к электросвязи и может быть использовано при передаче данных в системах с информационной обратной связью. Изобретение повышает пропускную способность сис- темы. Система содержит на передающей стороне - блок кодирования, синхронизатор, регистр сдвига, модулятор, блок сумматоров по модулю два, формирователь синхроимпульсов, генератор эталонного кода, преобразователь эталонного кода (ПЭК), два сумматора помодулю два; на приемной стороне -демодулятор, синхронизатор, сумматор по модулю два, блок задержки,коррелятор, генератор эталонногокода, два регистра сдвига, два дополнительных блока (ДБ) элементов И,два блока сумматоров 1 по модулю два,блок сравнения кодов (БСК), блокобнаружения ошибок, блок элементовИ, преобразователь эталонного кода,Цель достигается введением на передающей стороне - ПЭК, состоящегоиз двух каналов, включающих в себявходной инвертор и И цепей, состоящих из инвертора, двух элементов Ии элемента ИЛИ; на приемной стороне - двух ДБ элементов И, БСК состоящего из двух каналов, включающих всебя сумматор, пороговый блок, сумматор по модулю два и и цепей, состоящих из сумматоров по модулю дваи инверторов, и ПЭК. 3 з.п, ф-лы.5 ил.Изобретение относится к электросвязи и может быть использовано при передаче данных в системах с информационной обратной связью.Цель изобретения - повышение 5 пропускной способности.На фиг. 1 и фиг. 2 представлены соответственно структурные электрические схемы передающей и приемной сторон системы передачи и приема 1 О цифровых сигналов с обнаружением ошибок; на фиг. 3 - структурнаяэлектрическая схема преобразователя эталонного кода; на фиг. 4 в структур. ная электрическая схема блока сравнения кодов; на фиг. 5 - структурная электрическая схема блока обнаружения ошибок. 50 Система передачи и приема цифровыхсигналов с обнаружением ошибок содержит на передающей стороне - блок1 кодирования, синхронизатор 2, регистр 3 сдвига, модулятор 4, блок 5сумматоров по модулю два, формирователь 6 синхроимпульсов, генератор 725эталонного кода, преобразователь 8эталонного кода, первый сумматор 9по модулю два и второй сумматор 10по модулю два; на приемной стороне -демодулятор 11, синхронизатор 12,сумматор 13 по модулю два, блок 14задержки, коллектор 15, генератор 16эталонного кода, первый регистр 17сдвига, первый дополнительный блокэлементов И 18, второй регистр 19 35сдвига, второй дополнительный блокэлементов И 20, первый блок 21 сумматоров по модулю два, второй блок 22сумматоров по модулю два, блок 23сравнения кодов, блок 24 обнаружения 40ошибок, блок элементов И 25, преобразователь 26 эталонного кода.Преобразователь 8 (26) эталонногокода содержит входной инвертор 27,вторые элементы И 28 и 29, инверторы 4530 и 31, первые элементы И 32 и 33,элементы ИЛИ 34 и 35, входной инвертор 36, вторые элементы И 37 и 38,инверторы 39 и 40, первые элементыИ 41 и 42, элементы ИЛИ 43 и 44,Блок 23 сравнения кодов содержитвторые сумматоры 45 и 46 по модулюдва, инверторы 47 и 48, сумматор 49;пороговый блок 50, первый сумматор5 1 по модулю два, вторые сумматоры 5552 и 53 по модулю два, инверторы 54и 55, сумматор 56, пороговый блок57, первый сумматор 58 по модулю два, и а - нечетные элемен(и 1ты;1и а . - четные элементы.1 Фд где а;аЭти пары соседних слов вводятся врегистр 3. В первом и втором сумматорах 9 и10 по модулю два вычисляются суммыпо модулю два, лб =+с: а;ОфЕ а)к По сочетанию сигналов 8, и 52 в соответствии с табл. 1 определяется эталонный-разрядный код, который (В и 6 ) вырабатывается. генератором 7 эталонного кода. Таблица 1 кодыв,в,0 0 0 1 в, в,1 0 Двоичные эталонные коды, приведенные в табл. 1, имеют следующую структурун 127Ь 2 Блок 24 обнаружения ошибок содержит сумматоры 59 и 60 по модулю два,инверторы 61 и 62, сумматоры 63 и 64по модулю два, инверторы 65 и 66,элемент ИЛИ 67, инвертор 68.Система передачи и приема цифровыхсигналов с обнаружением ошибок работает следуацим образом,На передающей стороне 1 кодирования (фиг. 1) вырабатывает информационные слова из поступающих входныхинформационных сигналов. Эти информационные . слова разбиваются на группыиз 2-х слов (в каждом слове 2 и элементов).1а Йа;2 а;2 а1 (1 (н 12 (+12 641 ( 7В блоке 5 сумматоров по модулю дваопределяются элементы Си С. )к поправилу(111 к (1111 к(м 1 к Ям -(11)к (1)ка 55 Всего образуется 2 н символов С,иС .Для их формирования в преобра(1 1 кзователь 8 эталонного кода (фиг. 3)подается два эталонных и -разрядныхкодовых слова 81 и 82 (выражения 4и 6) и сигналы б; и 5первого ивторого сумматоров 9 и 10 по модулюдва. В зависимости от сигнала б 1(0или 1) и 5 (О или 1) на вход блока5 сумматоров по модулю два подаютсяс выхода блока 8 преобразованияэталонного кода кодовые комбинацииВ 1 или 81, Б или ЬКодовые символы С; и С,) двухсоседних слов записываются в ячейкахрегистра 3, емкость которого составляет 6 п ячеек.Два соседних слова, записанныхв регистре 3, имеют следующую структуру:аС;,а. а С а ,а а11 11 11 2 1 Х 11111 1 111 6+11 (11111а,а С(111" 1 и 1 к 1111 6 н 1Это сложное слово содержит 6 исимволовС помощью синхроимпульсов с выхода формирователя 6, управляемого .синхронизатором 2, производится пре-гобразование параллельного 6-тиразрядного двоичного сложного словав последовательность посылок, которая поступает в модулятор 4, такжеуправляемый синхроимпульсами формирователя 6.На приемной стороне демодулированые посылки с выхода демодулятора 11(фиг. 2) поступают непосредственнои с задержкой с и 2 с, где- длительность посылок, реализуемой блоком14 задержки,в сумматор 13 по модулюдва,в которомпутем суммирования элементовюнгде индекс Ф означает, что это принятые по каналу символы кодовогосигнала, определяются восстановленкные элементы 1 .и ,1 эталонногокода, т.е,5В последовательности выходных символов сумматора 13 по модулю двакаждый третий символ является элементом восстановленного эталонного кода.1Эта последовательность вводится вкоррелятор 15, на вторые 2 и входовкоторого подаются от генератора 16эталонного кода кодовые сигналы 6 иО 2 . Выделенные главные пики функцийвзаимной корреляции кодоых слов 81 ЙЬ а также 8 и В поступают в%виде синхросигнала для фазированйяколебаний синхронизатора 12.Последовательность посылок с выхода сумматора 13 по модулю два вводит-ся в первый регистр 17. В момент заполнения всех его ячеексимволами .11%1 Ки 5;1 восстановленного эталонногокода последние поступают на информационные входы первого дополнительногоблока элементов И 18, связанные с первыми входами, входящих в него элементов И. На тактовый вход первого дополнительного блока элементов И 18,связанный со вторыми входами входящихв него элементов И, поступает синхроимпульс с выхода синхронизатора 12.При этом кодовые комбинации б 1 и ВФ %восстановленного эталонного кодаподаются в блок 23 сравнения кодов(фиг, 5).Последовательность символов аС"и а из демодулятора 11 вводится во второй регистр 19, выходыпамяти которого связаны с информационными входами второго дополнительного блока элементов И 20, При заполнении второго регистра 19 на тактовыйвход второго дополнительного блока 45 элементов И 20 из синхронизатора 12подается синхроимпульс., 1 ЮПосылки а и оиз второго дополнительного блока 20 элементов подаются на входы блока элементов И 25, атакже на входы первого и второго блоков 21 и 22 сумматоров по модулю два.В первом блоке 21 сумматоров по модулю два вычитаются а 5", = Оф Е а",Ю Е а к" к а во втором блоке 22 сумматоров по модулю два(1+11 к ут.е, соответственно суммируются четные и нечетные информационные символы двух соседних слов. 5В логическом блоке 23 сравнения определяются нормы разности восстановленных эталонных кодов Ъ, и В; с кодами б; и В эталонного кода генератора 16- фЬ,-в",1 И,Если 1 г 6 Ьо (порог), то вырабатывается сигнал ,д =О. Если ц 7 цо15 то вырабатывается сигнал/ =1. Вели чина порога Ь =при нечетноми+1о гь, 1 =при четном и . При этом возможны 4 комбинации (табл. 2)20 Ьо ЬоЬ 2 Ьо Ь 1 Ьо ЬЬо При сигналах=О от генератора16 эталонного кода через преобразователь 26 эталонного кода на блок 24обнаружения ошибок поступают кодовыекомбинации б, и 6 (без инвертирования символов). При сигналах (31 д =1кодовые комбинации, поступающие отпреобразователя 26 эталонного кода 40в блок 24 обнаружения ошибок, будутинвертированными, т.е, поступят комбинации В, и ЙПреобразователь 26 эталонногокода имеет структуру аналогичнуюструктуре преобразователя 8 эталонного кода (фиг. 3).В блоке 24 обнаружения ошибок производится поразрядное суммирование элементов Ь и Ь; (или Ь ), а также элементов Ъи с Ь (или Ъ ),6 и)к (1+фР ак 6 н 1 к с 1 и 1 кЮЬкЭти сигналы поступают через элемент ИЛИ 67 блока 24 обнаружения ошибок 55 на его выход, На элемент ИЛИ 67 блока 24 обнаружения ошибок также подаются сигналы из блока 23 сравнения кодов.Если какой-либо из сигналов Ф;0 с(;+,)к илиравны "1, то навыходе блока обнаружения ошибоквозникает сигнал "О", который подается на управляющий вход блока элементов И 25. В этом случае информационная часть входного кода, состоящая из посылок аи ана выходне поступает,Сравнение предлагаемой системыс прототипом показывает, что онаобладает такой же обнаруживающейспособностью, что видно из приводимых формул числа необнаруживающейспособности ошибок 4-й кратности (1 )Нк =3 С,где и - число разрядов эталонногокода,Если в слове на входе приемника1П = 3 и элементов, то й, =зс,.Вместе с тем отпадает необходимость введения трех добавочных символов 8 8 и С+ за счет более полного использования имеющейся избыточности, что позволяет повы-, сить скорость передачи информации.Таким образом, предлагаемая система передачи и приема цифровых сигналов с обнаруживанием ошибок обеспе чивает более высокую пропускную способность по сравнейию с известной системой. формула изобретения 1. Система передачи и приема цифровых сигналов с обнаружением ошибок, содержащая на передающей стороне - последовательно соединенные син.хронизатор, блок кодирования,регистр сдвига и модулятор, а такжепервый и второй сумматоры по модулюдва, генератор . эталонного кода,блок сумматоров по модулю два и формирователь синхроимпульсов, выходсинхронизатора подсоединен непосредственно и через формирователь синхроимпульсов соответственно к тактовым входам генератора эталонногохода и регистра сдвига, нечетныеи четные выходы блока кодирования .подсоединены соответственно к выхо759 1221 7дам первого и второго сумматоров по модулю два, дополнительные информационные входы регистра сдвига подключены к соответствующим выхо,дам блока сумматоров по модулю два, входы которого подключены к соответствующим выходам блока кодирования, на приемной стороне - последовательно соединенные демодулятор, сумматор по модулю два, коррелятор, синхрони затор и генератор эталонного кода, последовательно соединенные блок обнаружения ошибок и блок элементов И, а также первый и второй регистры сдвига, первый и второй блоки сумма в 15 торов по модулю два и блок задержки, выход и вход которого подключены соответственно к второму входу сумматора по модулю два и выходу демодулятора, опорный вход демодулятора под в 20 ключен к выходу синхронизатора, а входы первого и второго блоков сумматоров по модулю два подключены к соответствующим входам блока, элементов И, причем информационный вход 25 блока кодирования на передающей стороне и выходы блока элементов И на приемной стороне являются соответственно информационными. входом и выходом системы, а выход модулятора и З 0 вход демодулятора являются соответственно канальными выходом и входом системы, о т л и ч а ю щ а я с я тем, что, с целью повышения пропускной способности, введены на передаю- З 5 ей стороне - преобразователь эталонного кода, на приемной стороне - первый и второй дополнительные блоки элементов И, блок сравнения кодов и преобразователь эталонного кода, 40 при этом на передающей стороне выходы первого и второго сумматоров по модулю два подсоединены соответственно к первому и второму управляющим входам преобразователя эталонного кода, 2 и .-талонных входов которого подключены к соответствующим выходам генератора эталонного кода, 2 и выходов преобразователя эталонного кода подсоединены к соответствующим 50 дополнительным входам блока сумматоров по модулю два, опорный вход моду пятора подключен к выходу блока форМирования синхроимпульсов, на приемной стороне выходы сумматора по модулю два идемодулятора подсоединены соответственно к входам первого и второго регистров сдвига, 2 и выходов первого регистра сдвига черезпервый дополнитейьный блок элементов И подсоединены к соответствующим 2 И информационным входам блокасравнения кодов и к 2 п информационным входам блока обнаружения ошибок,входы первого блока сумматоров помодулю два подключены к нечетнымвыходам второго дополнительногоблока элементов И, четные выходыкоторого подсоединены к входам второго блока сумматоров по модулю два,выходы первого и второго блоков сумматоров по модулю два подсоединенысоответственно к первому и второмудополнительным информационным входамблока сравнения кодов, первый и второй выходы которого подсоединенысоответственно к первому и второмудополнительным информационным входамблока обнаружения ошибок, третий ичетвертый выходы блока сравнения кодов подсоединены соответственно кпервому и второму управляющим входампреобразователя эталонного кода,211 выходов которого подсоединены ксоответствующим 2 и эталонным входамблока обнаружения ошибок, 2 и выходов генератора эталонного кода подсое.динены к соответствующим 2 и эталонным входам коррелятора и 2 и эталонным входам преобразователя эталонногокода, дополнительный выход синхронизатора подсоединен к тактовым чходамблока элементов И, первого и второгодополнительных блоков элементов И,адополнительный выход блока задержкиподсоединен к дополнительному входусумматора по модулю два. 2. Система по п. 1, о т л и ч а ю. щ а я с я тем, что преобразователь эталонного кода содержит первый и второй каналы преобразования эталонного кода, каждый из которых включает входной инвертор и и цепей, состоящих из последовательно соединеных инвертора, первого элемента И и элемента ИЛИ, а также второго элемента И, вход и выход которого подключены к входу инвертора и второму входу элемента ИЛИ, вход входного инвертора подключен к вторым входам первых инверторов и и цепей, выход входного инвертора подсоединен к вторым входам вторых элементов И И цепей, причем входы входных инверторов первого и второго каналов преобразования эталонного кода. являются9 1221759 1 Опервым и вторым управляющими входами онными входам блока сравнения кодов, преобразователя эталонного кода, выходы первых сумматоров по модулю, первые входы вторых элементов И пер- два первого и второго каналов сраввого и второго каналов преобразова- нения кодов являются соответственно ния эталонного кода являются эталон первым и вторым выходами блока сравными входами преобразователя кода, а нения кодов, а выходы пороговых бловыходы элементов ИЛИ первого и второ- ков первого и второго каналов сравнего каналов преобразования эталонного ния кодов являются соответственно кода являются выходами преобразовате третьим и четвертыми выходами блока ля эталонного кода. 1 О сравнения кодов.3. Система по п, 1, о т л и - 4. Система по п. 1, о т л и ч а юч а ю щ а я с я тем, что блок щ а я с я тем, что, блок обнаружения сравнения кодов содержит первый и ошибок содержит последовательно соедивторой каналы сравнения кодов, каж- ненные элемент ИЛИ и первый инвертор, дый из которых включает последова а также 2 и цепей, состоящих из после- тельно соединенные сумматор, порого- довательно соединенных сумматоров по вый блок и первый сумматор по модулю модулю два и вторых инверторов, выдва, а также и цепей, состоящих из ходы которых подключены к выходам последовательно соединенных вторых элемента ИЛИ, причем первые и вторые сумматоров по модулю два и инверто входы элементов И являются соответстров, выходы которых подсоединены к венно 2 и информационными и 2 п этавходам сумматора, причем первые и лонными входами блока обнаружения вторые входы вторых сумматоров по ошибок, первый и второй дополнитель-, модулю два первого и второго каналов ные входы элемента ИЛИ являются соотсравнения кодов являются соответст ветственно первым и вторым дополни" венно информационными и эталонными тельными информационными входами бловходами блока сравнения кодов, вторые ка обнаружения ошибок, а выход перво" входы первых сумматоров по модулю два го инвертора является выходом блока являются дополнительными информаци- обнаружения ошибок.1221759 Составитель В. ОрловТехред Л.Олейник Корректор А,Обручар Редактор Л, Повхан Тираж 816 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская наб., д. 4/5

СмотретьЗаявка

3737822, 04.05.1984

ЛЕНИНГРАДСКИЙ ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ СВЯЗИ ИМ. ПРОФ. М. А. БОНЧ-БРУЕВИЧА

САФАРОВ РИЗА ТАДЖИЕВИЧ

МПК / Метки

МПК: H03M 13/51

Метки: обнаружением, ошибок, передачи, приема, сигналов, цифровых

Опубликовано: 30.03.1986

Код ссылки

<a href="https://patents.su/8-1221759-sistema-peredachi-i-priema-cifrovykh-signalov-s-obnaruzheniem-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Система передачи и приема цифровых сигналов с обнаружением ошибок</a>

Предыдущий патент: Преобразователь двоично-десятичного кода в двоичный

Следующий патент: Преобразователь код-задержка пачки импульсных сигналов

Случайный патент: Капустоуборочная машина