Устройство для исправления ошибок кодов боуза-чоудхури хоквингема

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

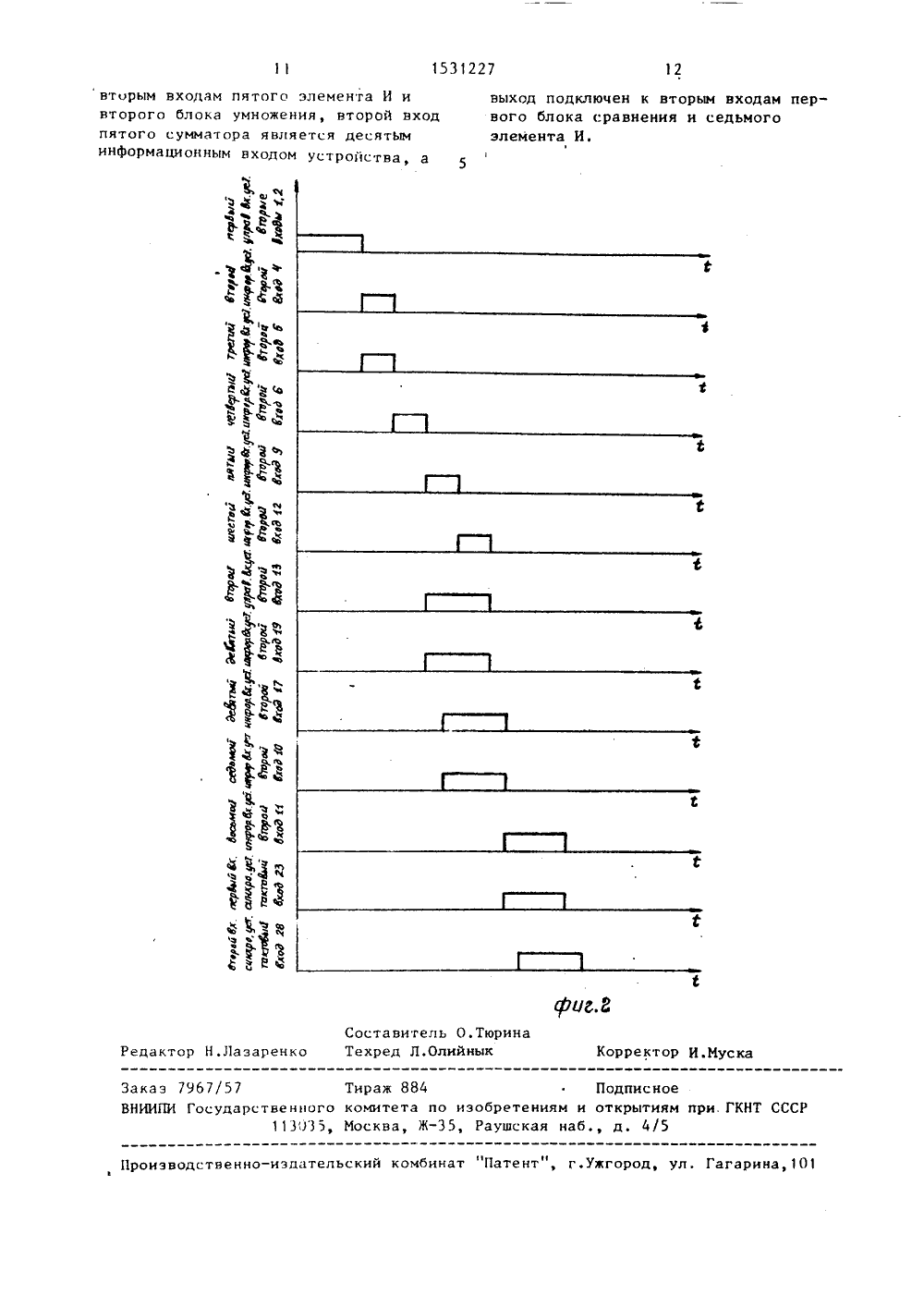

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИ ХРЕСПУБЛИК 8015 227 А 1 1)4 Н ОЗМ 1 З НИЕ ИЗОБРЕТЕН 21) 4281067/24-2422) 09 А 7.8746) 23.12,89. Вюл 47 Ц ту нницкий исти литехническ ерсдЖ ГОСУДАРСТ 8 ЕННЫЙ НОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГКНТ СССР К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(56) Авторское свидетельство СССР 11 1115055, кл. С 06 Р 11/1 О, 1982.Авторское свидетельство СССР Мф 11856 11, кл, Н 03 М 13/00, 1983. (54) УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК КОДОВ НОУЗА-ЧОУДХУРИ-ХОКВИНГЕМА (57) Изобретение относится к автоматике и вычислительной технике и может 1 ть использовано для повышения досто 2верности обработки и передачи дискретнои информации. Цель изобретения - повышение помехоустойчивости устройства. Устройство для исправления ошибок кодов Ноуза-Чоудхури-Хоквинима содержит датчики 1,2 и 23 импульсов, сумматора 3,5,8,19 и 37, блоки 4,10 и 12 вычитания, блоки 6 и 16 умножения, блок 7 логарифмирования, блоки 8,11 и 22 деления, блоки 20 и 24 сравнения, элементы И 18, 21, 27,31, 39, 33 и 36, регистры 35, 13,17, регистры 25 и 38 сдвига, входной и выходной регистры 32 и 40, элементы ИЛИ 29 и 34, триггеры 26 и 30, рев сивный счетчик 28, регистр 14 адре и блок 15 постоянной памяти. 2 ил .Изобретение Отцосцзс.я к д нтома ги-.ке и вычислительной технике и может ЗОМ 11 ерноцачнльцос умс гор 5 зацосит - ся дноичцое чцло, соотнетсснующее35 единице, н бло;ц,; нстдцця заноситсядвоичное чцло, Оо, тствующее количеству ицформдциоццых символов код- ной комби сцци,; остуцающей цд перный ИФОрМаццСцЬ:и НХС 1 П утройГНа, Н блок 6 умножения эдцоснгя двоичное 40 число, соочветсгнующее двойке, н реГитр 13 3 дцоситсч двоичное число,оогнетстнукнее елнине, цд входсумматора 19 поступдег дном свое число, с.оотнетстнуюшан единице. В блоке 15 гсостояццой памяти здпцдны значения миццмдаьцьх полиомон с соОгветстнуюнн 1 мц адресами.Кодовая комбинация, закодированная циклическим кодом (Е,К), пос:туна 50 е г на вход рнгцс гра 32 и Одновременно ца пернын нходы счетчиков 1 и 2 (счетчик 1 считает колцчес:твс единиц, а счетчик 2 - количество улей кодовой комбцндци), Нд церный вход сумматора 3 исгдде ся днсгцчное чи,ло,с.осггне гсз нукцссен колцчестну ц . лей прицимаемоц к д нс и; омбицдции, н нтоиспользонаться для понышения достоверности обрдботки и цгреддчи дис 5 кретцой информации.1 елью изобретения янляется повышение помехоустойчиноти устройства.На Фиг, 1 представлена Функциональная с:хема устройс.тнд; на фцг, 2- временная диаграмма сигналов на входах устройства.Устройс.тво с.одер кит счетчики 1 и 2 импульсон, с.умматор 3, блок 4 вычитания, с:уммдгор 5, б;ок 6 умножения, блок 7 логарифмирования, блок 8 деления, сумматор 9, б;:ок 10 вычитания, блок 11 деления, блок 12 вычитания, регистр 13, регцс гр 14 адреса, блок 15 постоянной памяти, блок 16 умноже ция, регис.тр 17, элемсцг И 18, с:уммагор 19, блок 20 срднцецич, элемент И 21, блок 22 деления, счетчик 23 импульсов, блок 24 ранцеив, регистр 25 сдвига, триггер 26, элемент И 27, 25 реверснный счегчик 28, элемент ИЛИ 29, триггер 30, зс:мец г И 31, нходой регистр 32, эдл ис. г И 33, Ъемнцг Ш 1 И 34, рс ист 1 35, элемент И 36, , ммдтс 1 р 37, реги гр 18 днигд, эле- МЕ Г И 39, НЫХОдСгй рЕГИтр 40.Устройстно рцбогдет с.ледуюшим Обрарой вход сумматора 3 подается двоичное число, соответствующее количеству единиц принимаемой кодовой комби-, нации. С выхода сумматора 3 количество символов, соответствующее результату суммирования, подается одновременно на вход сумматора 5 и вход блока 4 вычитания. С выхода блока 4 двоичное число, соответствующее количеству проверочных символов, подаетс:я на первый вход блока 6. Одновременно на второй его вход подается сигнал, соответствующий двойке. С выхода блока 6 двоичное число, соогветствующее результату умножения, подается на первый вход блока 8 деления. С выхода сумматора 5 результат суммирования подается на вход блока 7 логарифмирования по основанию два. С выхода блока 7 двоичное число, соответствующее результату логарифмирования, подается одновременно на второй вход блока 8 и на вхо, младших разрядов регистра 13. С выхода блока 8 двоичное число, соответствующее результату деления, подается на первый вход сумматора 9, на второй вход которого подается двоичное число, соответствующее единице. С выхода сумматора 9 двоичное число, соответствующее результату суммирования, подается одновременно на первый вход блока 12 и первый вход блока 10. С выхода блока 10 ца первый вход блока 11 деления подается двоичное число, соответствующее результату вычитания, на второй его вход подается число два. С.выхода блока 11 на первый вход блока 24 сравнения подается двоичное число, соответствующее результату деления. На второй вход блока 12 подаетс,я двоичное число, соответствующее единице. С выхода блока 12 двоичное число, соответствующее результату вычитания, подается на второй вход блока 20 сравнения. Одновременно на управляющий вход регистра 13 подается сигнал, который обеспечивает подачу двоичного числа, соответствующего единице, одновременно на первый вход сумматора 19 и на нход старших разрядов регистра 14. С выхода регистра 14 сформированный адрес поступает на вход блока 15. С выхода блока 15 выбранный минимальный полицом подается на первый вход блока 16. Одновременно на второй вход блока 16 с выхода регистра 17 подает15312ся двоичное число, соответствующее единице, поскольку на вход регистра 17 подается высокий потенциал девятого информационного входа. С выхода5 сумматора 31 двоичное число, соответствующее результату суммирования, подается одновременно на второй вход элемента И 21 и первый вход блока 20, В блоке 20 сравнивается двоичное чис ло, соответствующее результату суммирования в сумматоре 19 с двоичным числом, соответствующим порядку старшего из минимальных полиномов, которое поцается с выхода блока 12. Если двоич ное число, которое подается на первый вход блока 20, меньше или равно двоичному числу, соответствующему порядку старшего измииимальных полиномов, то тогда на первом выходе Меньше или 20 равно" блока 20 появится сигнал, который обеспечивает подачу двоичного числа с выхода сумматора 19 через элемент И 21 на информационный вход регистра 13, Это двоичное число с вы хода регистра 13 подается одновременно на вход старших разрядов регистра 14 и на первый вход сумматора 19. С выходов регистра 14 сформированный новый адрес подается на вход блока 301), С выхода блока 15 выбранный новый полином подается на первый вход блока 16. В блоке 1 Ь выбранный новый полином умножается на предыдущий, Результат умножения записывается в регистр 17. На второй вход сумматора 19 одно 35 временно с десятого информационного входа подается двоичное число, соответствующее единице. Результат суммиОВания подается на Второй ВхОд эле 40 мента И 21 и первый вход блока 20В блоке 20 сравниваегся двоичное число, соответствующее результату суммирования в сумматоре 19 с двоичным числом, соответствующим порядку старшего из минимальных полиномов, которое подается с выхода блока 12. Если двоичное число, которое подается на первый вход блока 20, меньше или равно дВОичному числу, сООтВетстВующе му порядку старшего из минимальныхполиномов, на первом выходе Меньше или равно" блока 20 появляется сигнал, который обеспечивает подачу двоичного числа с выхода сумматора 19 че 55 рез элемент И 21 на информационный вход регистра 13. Затем повторяется процедура выбора и умножения полиномов. Эта процедура прополжается до 27 6тех пор, пока на втором выходе блока20 "Больше" не появится сигнал. Споявлением на втором выходе "Больше"блока 20 сигнала обеспечивается подача двоичного числа, соответствующего результату умножения полиномов, находящихся в регистре 17, через элемент И 18 на второй вход блока 22 и одновременно подача принятой кодовой комбинации, находящейся в регистре 32, через элементы И 33, ШЯ 34 на вход регистра 35. С ВыХОда регистра 35 принятая кодовая комбинация подается одновременно на второй вход элемента И 36, информационный вход регистра 25 сдвига, который сдвигает информацию на один разряд влево и первый вход блока 22. В блоке 22 принятая кодовая комбинация делится на соответствующий выбранный образующий полином. С выхода блока 22 остаток от деления подается одновременно на первый вход элемента И 31 и управляющий вход сложения счетчика 23, С выхода счетчика 23 вес остатка от деления подается на второй вход блока 24, на который также подается двоичное число, соответствующее количеству исправляемых ошибок с выхода блока 11. В блоке 24 происходит сравнение количества исправляемых ошибок с весом остатка от деления, В случае, если количество исправляемых ошибок меньше, чем вес остатка от деления, на первом Выходе блока 37 Меньше появляется сигнал, который подается одновременно на управляющий вход сложения счетчика 28, вход триггера 26 и на разрешающий вход регистра 25 сдвига на один разряд влево. После сдвига на один разряд влево с выхода регистра 25 кодовая комбинация подается на первый вход элемента И 27, Одновременно с выхода триггера 2 Ь разрешающий сигнал подается на второй вход элемента И 27. Этот сигнал обеспечивает подачу сдвинутой кодовой комбинации через элемент И 31 И 29 на вход регистра 25, с выхода которого сдвинутая кодовая комбинация подается одновременно на второй вход элемента И 36, первый вход блока 22 и информационный вход регистра 25. В блоке 22 происходит деление сдвинутой кодовой комбинации на выб ранный образующий полином. С выхода блока 22 остаток от деления подается одноврем:нно на первый вход элемен 1531227та И 31 и управляющий вход сложения счетчика 23. С выхода его вес остатка от деления подается на второй вхоД блока 24, где происходит сравнение количества исправляемых ошибок с ве 5 сам остатка от деления. В случае, если количество исправляемых ошибок меньше, чем вес остатка ст деления, на первом выходе блока 24 "1 еньше" появляется сигнал, когорый подаетсяаодновременно ня ря зрешающий вход сложения счетчика 28, вход триггера 2 б и на разрешающий вход регистра 25. После сдвига на один разряд влево с вы 15 хода регистра 25 вновь сдвинутая кодовая комбинация падается на первый вход элрментя И 27. Одновременно с выхода триггера 26 решающий сигнал обеспечиваег подачу с выхода элемснтя И 27 вновь сдвинутой кодовой комбина.- ции на вход регистра 35 иереэлемент И 11 И 34. Этя процедура повторяется до тех пор, иокя в блоке 24 количество исправляемых ошибок будет больше 25 или равно веса остатка от деления, С второго выхода блока 24 "Больше или равно" сигнал подается одновременно ня первый вход элемента ИЛИ 29, второй вход зле.ентя И 3 и втсрои вход 30 элемента И 3 б. 11 ри том остаток от деления подается ня второй вход сумматора 37 через эл:",генг И 3. Одновременна ня первый вхо, сумматора 37 псдяетсв последняя сдвинутая комбинация через "к: иг И 3 б. С выхода35 сумматора 37 резульг суммирования подаегся на информационный вход регистра 38, в котором происходит сдвиг информации на адин разряд права. В это время с выхода эл;:метя И.П 29 на вход счетчика 38 подается управляющий сигнал вычита.я, каторыи обе печивает вычитание единицы нз падсчитанного числя, соответствующего коли 45еству сдвигов вне", С вьхода счетчика 28, састнетству,щего енулевсму состоянию, сигнал п дяетсл одновременно на вход триггера 30 и разрешающий вхсд регистра 33, ри этом происходит сдвиг одного разряда впря 50 во. В эго время с выхода триггера 30 через элемент Ш 1 И 29 на вход счетчика 28 подается управляющий сигнал вычитания, 11 о:ле вторичного вычитания сигнал с выхода счетчика 28 падается одновременно ня вход триггера 30 и разрешающий вход регистра 38, при этом происходит вторичный сдв иг идного раэряда вправо. Эта процедура продолжается до тех пор,пока на выходе, соответствующем нулевому состоянию счетчика 28, не появится сигнал. Этот сигнал обеспечивает подачу с выхода регистра 38 на вход выходного регистра 40 через элемент 39 и исправленной кодовой комбинации, С появлением запрещающего сигнала на первом управляющем входе устройство прекращает прием кодовой комбинации.Отметим, что цифровая информация, используемая при работе устройства, представляется в двоичной системе ,счисления.Введение блока 15 постоянной памяти, блока 7 логарифмирования по основанию два, блоков 4, 10 и 12 вычитания и блоков 20 и 24 сравнения позволяет осуществить автоматическое получение образующего полинома для различных кодовых расстояний кодов БЧХ, Выбор образующего полинома позволяет осуществЛять исправления ошибок соответтвующей кратности за счет введения регистров 25 и 38 сдви" гя, реверсивного счетчика 28. ИсправЛение ошибок различной кратности производится путемравнения веса остатка от деления принимаемой кодовой комбинации на полученный образующий полинам с кратностью исправляемой ошибки, что значительно повышает корректирующую способность предлагаемого устройства и автоматически приводит к повышению достоверности контроля. Кроме того, устройство можег исправлять, ошибки любой кратности, соответствующей таблице минимальных полиномов, хранимой в блоке 15.Формула изобретенияУстройство для исправления ошибок кодов Боуза-Чоудхури-Хоквингема, содержащее входной регистр, вход которого является первым информационным входом устройства, первый элемент И, выход которого ггодключен к входу выходного регистра, выходы которого являются выходами устройства, первый регистр сдвига, тактовый вход которого объединен с входом первого триггера, первый и второй счетчики импульсов, второй триггер, первый и второй элементы Ш 1 И, первый и второй блоки деления, о т и и ч а ю щ е е с ятем, что, с целью повышения помехоустойчивости устройства, в него введены второй регистр сдвига, третий счетчик импульсов, реверсивный счет 5 чик, регистр адреса, блок постоянной памяти, второй - седьмой элементы И, блок логарифмирования, блоки сравнения, регистры, сумматоры, третий , блок деления, блоки вычитания и блоки умножения, первые и вторые входы первого и второго счетчиков импульсов попарно объединены и подключены соответственно к первому информационному и первому управляющему входам устройства, выходы первого и второго счетчиков импульсов и входного регистра подключены соответственно к первому и второму входам первого сумматора и первому входу второго элемента И, выход которого соединен с первым входом первого элемента Ш 1 И выход которого соединен с входом первого регистра, выход которого подключен к первому входу первого блока деления, 25 информационному входу первого регистра сдвига к первому входу тре гьего элемента И, выход которого подключен к первому входу второго сумматора, выход которого соединен с информационным входом второго регис гра сдвига, выход которого соединен со своим входом обнуления и первым входам первого элемента И, выход первого сумматора подключен к первым входам третьего35 сумматора и первого блока вычитания, вторые входы которых являются соответсгвенна третьим и вторым инфармационныйи входами ус тройства выход первого блока вычитания подключен к первому входу первого блока умножения, второй вход которого является четвертым информационным входом устройства, а выход соединен с первым входом второго блока деления, выход третьего сумматора через блок логарифмирования соединен с входам младших разрядов регистра адреса и вторым входом второго блока деления, выход которого подключен к первому входу чет 50 вертога сумматора, второй вход которого является пятым информационным входом устройства, а выход соединен с первыми входами второго и третьего блоков вычитания, гторые входы которых являются сас гветсгвеццо шестым и55 седьмым ицформациацньмц входами устройства, выходы втор ц а и третьего блоков вычи гация надк ю и ны саответственцо к первым входам первого блока сравнения и третьего блока деления, втораи вход которого является восьмым информационным входом устройства, а выход подключен к первому входу второго блока сравнения первый выход которого соединен с вторым входом третьего элемента И и первыми входами четвертого элемента И и второго элемента ИЛИ выходы которых подключены соответственна к второму входу второго сумматора и вычитающему входу реверсивного счетчика, первый выход которого через второй триггер соединен с вторым входом второго элемента И 11 И и непосредст" венно подключен к тактовому входу второго регистра сдвига, первый выход первого блока сравнения соединен с вторым входом второго элемента И и первым входом пятого элемента И, выход которого подключен к второму входу первого блока деления, выход которого соединен с вторым входом четвертого элемента И и информационным входам третьего счетчика импульсов, тактавыи вход которого является первым синхронизирующим входом устройства, а выход подключен к второму входу второго блока сравнения, второй выход которого подключен к входу первого триггера и суммирующему входу реверсивного счетчика, тактовый вход каторога является вторым синхронизирующим входом устройства, выход подключен к второму входу первого элемента И, выход первого регистра сдвига подключен к своему входу обнуления и первому входу шестого элемента И, второй вход и выход которого соединены соответственно с выходом первого триггера и вторым входом первого элемента И 11 И второй выход первого блока сравнения подключен к первому входу седьмого элемента И, выход которого подключен к ицформационному входу второго регистра, тактовый вход которого является вторым управля. ,ющим входом устройства, а выход соединен с первым входом пятого сумматора и входом старших разрядов регистра адреса, выходы которого подключены к входам блока постоянной памяти, выход которого соединен с первым входом второго блока умножения, выход которога подключен к первому входу третьего регистра, второй вход которого является девятым инФормационным входом устройства а выход подключен к

СмотретьЗаявка

4281067, 09.07.1987

ВИННИЦКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ

КЛЕМЕШОВ АНАТОЛИЙ АЛЕКСАНДРОВИЧ, МУСАЕВ ИКРАМ МОХТАРАМ ОГЛЫ, ШАРЕЙКО ЛЕВ АЛЕКСАНДРОВИЧ, ЮХИМЧУК СЕРГЕЙ ВАСИЛЬЕВИЧ

МПК / Метки

МПК: H03M 13/15

Метки: боуза-чоудхури, исправления, кодов, ошибок, хоквингема

Опубликовано: 23.12.1989

Код ссылки

<a href="https://patents.su/6-1531227-ustrojjstvo-dlya-ispravleniya-oshibok-kodov-bouza-choudkhuri-khokvingema.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для исправления ошибок кодов боуза-чоудхури хоквингема</a>

Предыдущий патент: Устройство для преобразования кодов

Следующий патент: Устройство контроля девиации частоты

Случайный патент: Устройство для измерения свч-мощности