Устройство для суммирования двух чисел с плавающей запятой

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

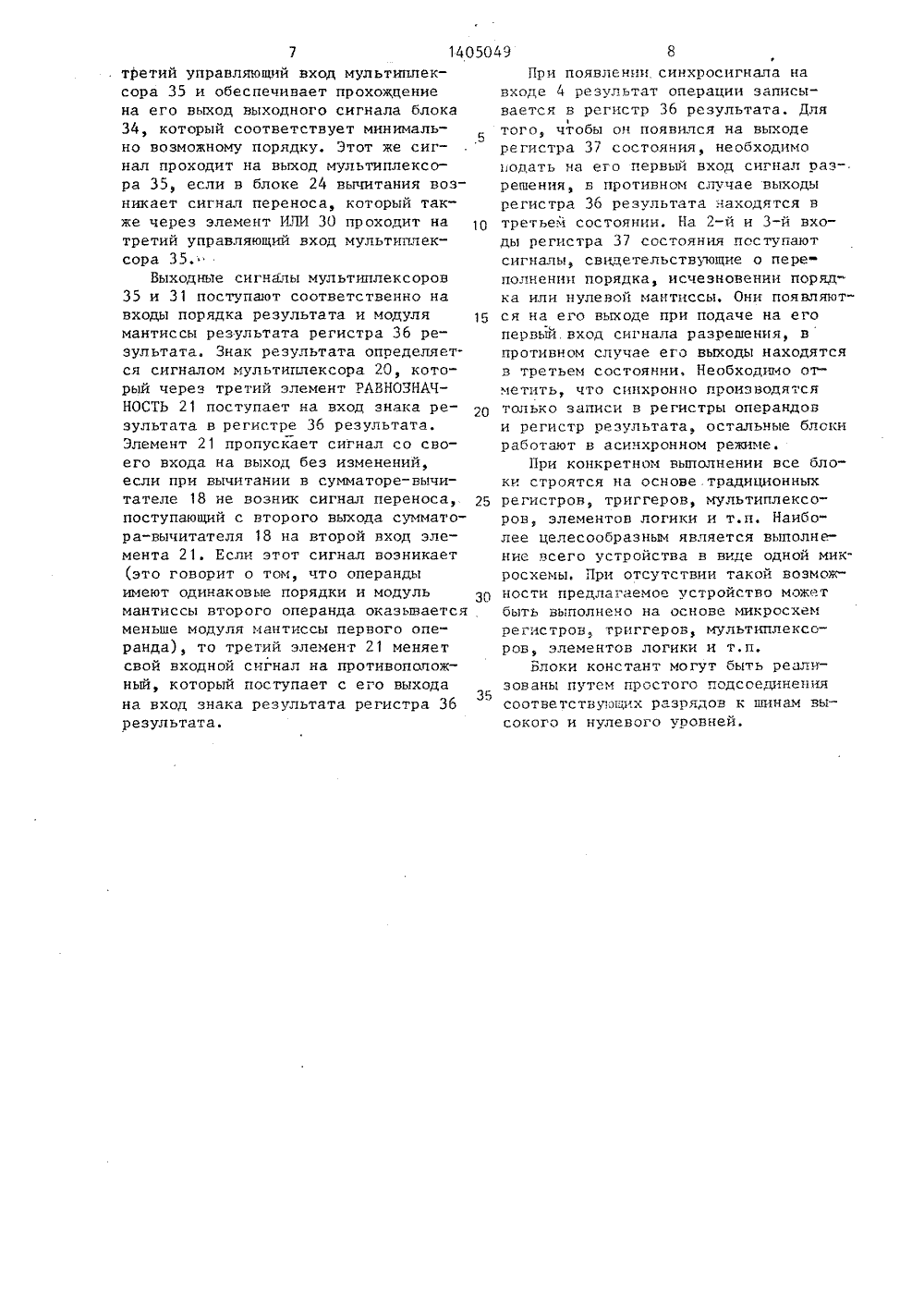

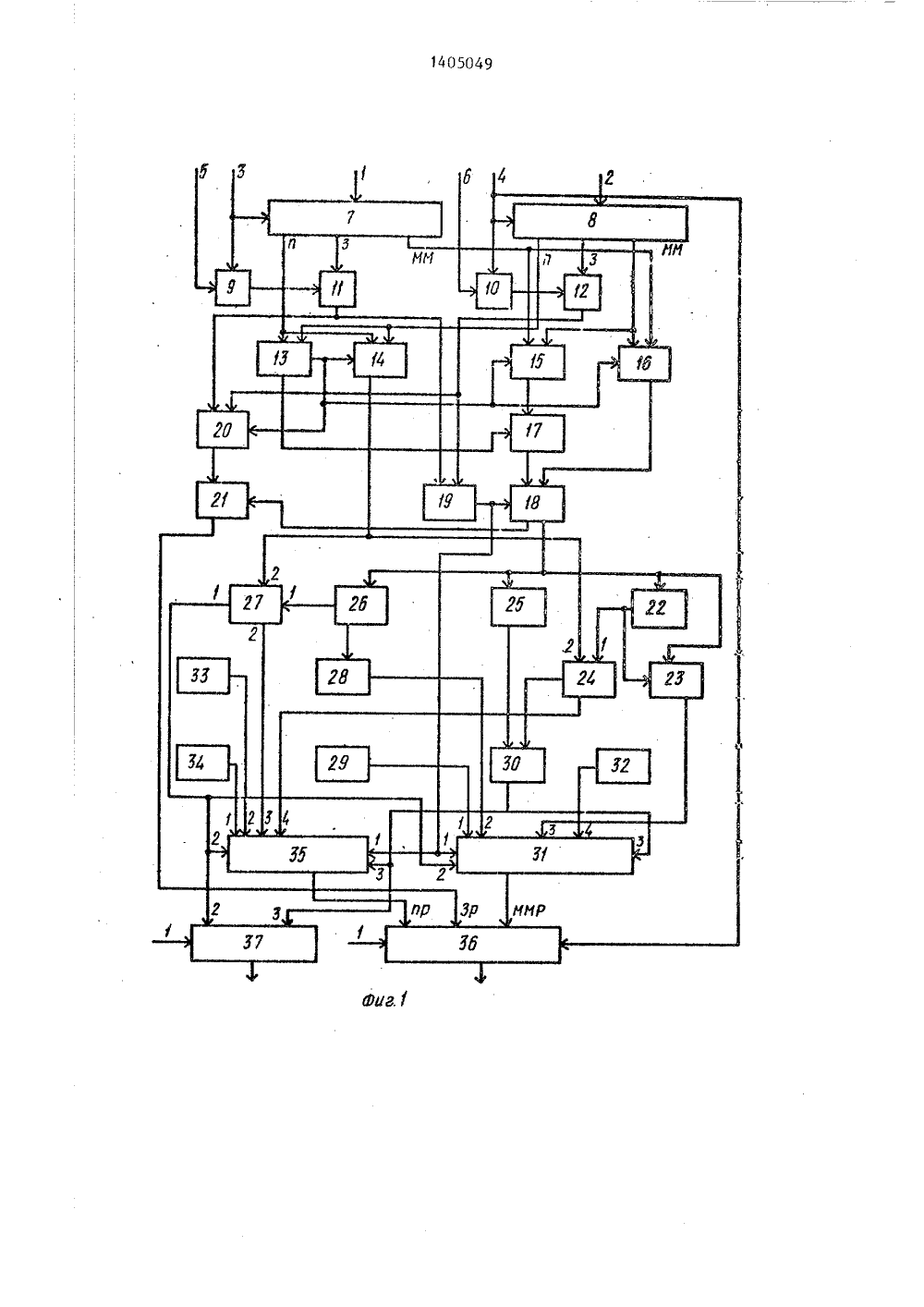

Текст

(56) Патент Японкл. 6 06 Р 7/50,Электроника,с.61-66, рис. 1,л. У 23в, Ю.А.Афанасьев 88.8)и В 54-44617, опублик. 1979 982, т. 55, Мф анты максимальноголок константы мининтиссы, мультиплекорядка,блок коодуля мантиссь ального модуля ГОСУДАРСТВЕННЫИ НОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТ ВТОРСКОМУ СВИДЕТЕЛЬСТВ(54)(57) УСТРОЙСТВО ДЛЯ СУММИРОВАНИЯДВУХ ЧИСЕЛ С ПЛАВАЮЩЕЙ ЗАПЯТОЙ, содержащее регистры первого и второгооперандов, компаратор, мультиплексор,первый и второй блоки обмена, блоксдвйга вправо, сумматор-вычитатель,шифратор приоритета, блок инкремента,блок сдвига влево, блок вычитания,блок округлсния, регистр состояния,регистр результата, блок сдвига вправо на один разряд, причем информационные входы первого и второго операндов устройства соединены соответственно с информационными входами регистров первого и второго операндов, выходы порядков регистров первого ивторого операндов соединены соответственно с первыми входами компаратора и мультиплексора и с вторыми входами компаратора и мультиплексора,выход результата сравнения порядковоперандов компаратора соединен с управляющим входом мультиплексора, выход которого соединен с информационным входом блока инкремента, выходмодуля разности порядков операндовкомпаратора соединен с управляющимвходом блока сдвига вправо, информационный вход которого соединен с выходом первого блока, обмена, выходблока сдвига вправо соединен с первым информационным входом сумматора-вычи, тателя, второй информационный вход которого соединен с выходом второго блока обмена, выход результата сумматора-вычитателя соединен с входом блока сдвига вправо на один разряд, выход выполнения операции сдвига блока сдвига вправо на один разряд соединен с счетным входом блока инкремента, выход шифратора приоритета соединен с входом вычитаемого блока вычитания и управляющим входом блока сдвига влево, о т л и ч а ю щ е е с я тем, что, с целью увеличения быстродействия, в устройство введены первый и второй элементы И, первьп, вто- а рой и третий элементы РАВНОЗНАЧНОСТЬ, мультиплексор знака, элемент ИСКЛЮ-. ЧАЮЩЕЕ ИЛИ, дешифратор нуля, элемент ИЛИ, блок константы максимального порядка, блок константы минимального сор порядка результата и мультиплексор модуля мантиссы, вход сигналасмены знака первого операнда устройства соединен с первым входом первого5 лемента И, второй вход которогосоединен с входом синхронизации записи первого операнда устройства и свходом разрешения записи регистрапервого операнда, выход знака которого соединен с первым входом первогоэлемента РАВНОЗНАЧНОСТЬ, второй входкоторого соединен с выходом первогоэлемента И, вход сигнала смены знакавторого операнда устройства соединенс первым входом второго элементаРАВНОЗНАЧНОСТЬ, второй вход которогосоединен с входом синхронизации записи второго операнда устройства, вхо1405049 дом разрешения записи регистра состояния и с входом разрешения записи регистра второго операнда, выход зна. ка которого соединен с первым входом второго элемента РАВНОЗНАЧНОСТЬ, вто рой вход которогс соединен с выходом второго элемента И, выход модуля мантиссы регистра первого операнда соединен с первыми информационными входами первого и второго блоков обмена, выход модуля мантиссы регистра второго операнда соединен с вторыми информационными входами первого и второго блоков обмена, управляющие входы которых соединены с управляющим входом мультиплексора знака и выходом результата сравнения порядков операндов компаратора, выход первого элемента РАВНОЗНАЧНОСТЬ соединен с первым информационным входом мультиплексора знака и первым входом элемента ИСКЛ 10 ЧАК 6 фЕ ИЛИ, второй вход которого соединен с вторым информационным входом мультиплексора знака и выходом второго элемента РАВНОЗНАЧНОСТЬ; выход мультиплексора знака соединен с первым входом третьего элемента РАВНОЗНАЧНОСТЬ, второй вход которого соединен с выходом переноса сумматора-вычитателя, выход результата которого соедчнен с входом шифратора приоритета, входом дешифратора нуля и информационным входом уменьшаемого блока вычитания, выход переноса которого соединен с первым входом элемента ИЛИ, второй вход которого соеди - нен с выходом дешифратора нуля выФ ход блока сдвига вправо на один разряд соединен с входом блока округления, первый, второй, третий, четвертый информационные входы мультиплексора модуля мантиссы соединены соответственно с выходами блока констан 1Изобретение относится к цифровой вычислительной технике и может быть использовано при построении арифметических устройств вычислительных машин, а также в устройствах цифровой обработки сигналов, работающих в системе счисления с плавающей запятой. ты максимального модуля мантиссы,блока округления, блока сдвига влевои блока константы минимального модулямантиссы, первый, второй, третий ичетвертый информационные входы мультиплексора порядка результата соединены соответственно с выходами блокаконстанты минимального порядка, блокаконстанты максимального порядка, выходом результата блока инкремента ивыходом результата блока вычитания,выход элемента ИСЮПООАЮЩЕЕ ИЛИ соединен с входом признака операции сумматора-вычитателя, первыми входамиуправления мультиплексора порядкарезультата и мультиплексора модулямантиссы, выход переполнения блокаинкремента соединен с вторыми входамиуправления мультиплексора порядкарезультата и мультиплексора модулямантиссы и первым информационным входом регистра состояния, второй информационный вход которот о соединен стретьими управляющими входами мультиплексора порядка результата и мультиплексора модуля мантиссы и выходомэлемента ИЛИ, вход порядка регистрарезультата соединен с выходом мультиплексора порядка результата, выходтретьего элемента РАВНОЗНАЧНОСТЬ соединен с входом знака регистра результата, вход модуля мантиссы которогосоединен с выходом мультиплексорамодуля мантиссы, вход разрешения выдачи результата устройства соединенс тактирующим входом регистра результата, выход которого соединен с выходом результата устройства, вход разрешения выдачи состояния устройствасоединен с тактирующим входом регистра состояния, выход которого сое.динен с выходом состояния устройства. 2Цель изобретения - увеличение быстродействия.На фиг.1 представлена структурная схема устройства для суммирования двух чисел с плавающей запятой; на фиг.2 - схема первого (второго) элемента И.5049 3 140Устройство для суммирования двух чисел с плавающей запятой содержит вход 1 первого операнда, вход 2 второго операнда, вход 3 синхронизации записи первого операнда, вход 4 синхронизации записи второго операнда, вход 5 сигнала смены знака первого операнда, вход 6 сигнала смены знака второго операнда, регистры первого 7 и второго 8 операнда, первый 9 и второй 10 элементы И 9, первый 11 и второй 12 элементы РАВНОЗНАЧНОСТЬ, компаратор 13, мультиплексор 14, первый 15 и второй 16 блоки обмена, блок 17 сдвига вправо; сумматор-вычитатель 18, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 19, мультиплексор 20 знака, третий элемент РАВНОЗНАЧНОСТЬ 2 1, шифратор 22 приоритета, блок 23 сдвига влево, блок 24 вычитания, дешифратор 25 нуля, блок 26 сдвига вправо на один разряд, блок 27 инкремента, блок 28 округления, блок 29 константы максимального модуля мантиссы, элемент ИЛИ 30, муцьтиплексор 31 модуля мантиссы результата блок 32 константы минимального модуля мантиссы, блок 33 константы максимального порядка, блок 34 константы минимального порядка, мультиплексор 35 порядка результата, регистр 36 результата и регистр 37 состояния.Первый (второй) элемент И (фиг,2) содержит КБ-триггер, элемент НЕ, элемент ИЛИ, элемент ИЛИ-НЕ.Устройство работает следующим образом.При поступлении сигнала синхро - низации на вход 4 в регистр второго операнда записывается второй операнд, поступающий на его второй вход. Синхронно с этим результат предыдущей операции записывается в регистр результата. На вход 3 сигнал подается Либо синхронно с сигналом входа 4, либо несколько позже, либо вообще не подается (когда первый операнд не меняется). Сигнал входа 3 синхронизирует запись первого операнда в регистр первого операнда. При необходимости знак мантиссы операнда может быть изменен на противоположный. Для этого на входы 5 и 4 подаются соответственно сигнал смены знака первого операнда и сигнал смены знака второго операнда. При совпадении сигналов 3 и 5 первый элемент И 9 вырабатывает сигнал, переключающий первый элемент РАВНОЗНАЧНОСТЬ 11 в ре 10 15 20 25 30 35 40 45 50 55 жим смены знака, в противном случае первая схема совпадения вырабатывает сигнал, переключающий элемент 11 в режим, когда он просто пропускает знак операнда со своего входа на выход. Аналогично работает второй элемент РАВНОЗНАЧНОСТЬ 12 и второй элемент И 10.Выходные сигналы элементов 11 и 12 поступают на входы мультиплексора 20 знака и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 19, выходной сигнал которого поступает на сумматор-вычитатель и определяет вид операции (суммирование или вычитание), которая производится над модулями мантисс. Порядки операндов с соответствующих выходов регистров первого 7 и второго 8 операнда поступают на входы компаратора 13 и мультиплексора 14. На первом выходе компаратора 13 получается сигнал, определяемый тем, какой из порядков больше, на втором выходе получается сигнал модуля разности порядков, поступающий на управляющий вход блока 17 сдвига вправо и определяющий число разрядов, на которое производится сдвиг вправо при выравнивании порядков.Первый выходной сигнал компаратора 13 поступает на управляющие входы мультиплексора 14, первого 15 и второго 16 блоков обмена и мультиплексор знака. На входы блоков 15 и 16 обмена поступают модули мантисс с соответствующих выходов регистров 7 и 8. Второй блок 16 обмена выдает на своем выхода модуль мантиссы операнда с большим порядком, который поступает на второй вход сумматора-вычитателя. Первый блок 15 обмена пропускает на свой выход модуль мантиссы операнда с меньшим порядком, мультиплексор 14 - больший из порядков, а мультиплексор 20 знака - знак мантиссы операнда с большим порядком.При равенстве порядков блок 16 пропускает модуль мантиссы второго операнда, блок 15 - модуль мантиссы первого операнда, блок 14 - порядка второго операнда, блок 20 - знак второго операнда. Выходной сигнал блока 16 поступает на второй вход сумматора-вычитателя 18, а выходной сигнал блока 15 поступает на первый вход сумматора-вычитателя 18 через блок 17 сдвига вправо, реализующий операцию выравнивания порядков, которая140504производится путем сдвига вправо модуля мантиссы операнда с меньшим порядком на число разрядов, равное модулю разности порядков,Сумматор-вычитатель 18 производитнепосредственно суммирование или вычитание модулей мантисс операндов.Результат появляется на его первомвыходе в прямом коде, Если произво -дится сложение, то дальнейшую обработку выходного сигнала (поступающ" -го с первого выхода) блока 18 производят блоки 26 и 28. Блок 26 сдвигавправо на один разряд осуществляетнормализацию выходного сигнала блока18 путем сдвига при необходимостивправо на один разряд, далее выходнойсигнал блока 26 поступает на блок 28,где он округляется до количества разрядов, определяемого Форматом представления входных операндов и резулвтата, и с его выхода поступает навторой информационный вход мультиплексора 31 модуля мантиссы результата,2 г,Кроме этого, блок 27 инкремента вслучае осуществления сдвига в блоке26 прибавляет единицу к порядку, поступающему на его второй вход с выходамультиплексора 14. На втором выходеблока 27 получается результирующийпорядок, который поступает на третийинформационный вход мультиплексора 35порядка результата. Если в блоке 27инкремента происходит переполнение,то на его первом выходе появляетсясигнал, который поступает на вторыеуправляющие входы мультиплексоров35 и 31 и второй вход регистра 37состояния.40 Если в сумматоре-вычитателе 18 производится вычитание, то дальнейшую обработку его выходного сигнала производят блоки 22 и 23, а порядок результата вычисляет блок 24 вычитания. Шифратор 22 приоритета определяет число разрядов, на которое нужно сдвинуть влево модуль мантиссы, поступающий с первого выхода блока 18, чтобы произвести его нормализацию. Сигнал, соответствующий этому числу разрядов, поступает на первыйчЬвход блока 24 вычитания и на первыи вход блока 23 сдвига влево. Блок 2355 осуществляет сдвиг модуля мантиссы влево после чего его выходной сигналЭпоступает на третий информационный вход мультиплексора 31. 9 6Блок 24 вычитания производит вычитание из порядка, поступающего на его второй вход с выхода мультиплексора 14, выходного сигнала шифратора 22 приоритета, и результирующий сигнал с его выхода поступает на четвертый информационный вход мультиплексора порядка результата.Мультиплексор 31 модуля мантиссы результата работает следующим образом. Если в блоке 18 производится сложение и в блоке 27 нет переполнения, то на его выход проходит выходной сигнал блока 28 округления, если же в блоке 27 происходит переполнение, то на его выход проходит выходной сигнал блока 29, который соответствует максимально возможному модулю мантиссы.Если в блоке 18 производится вычитание и в блоке 24 вычитания че возникает сигнал переноса (поступающий с второго выхода блока 24 через элемент ИЛИ 30 на третий управлиощий вход мультиплексора 31), то на его выход проходит выходной сигнал блока 23, если же в блоке 24 вычитания возникает перенос (что означает, что порядок стал меньше минимально возможного) или дешифратор 25 нуля выработал сигнал, соответствующий нулевому модулю мантиссы, то на выход мультиплексора 31 проходит выходной сигнал блока 32, который соответствует минимально возможному модулю мантиссы.Мультиплексор 35 работает следующим образом. Если в блоке 18 производится сложение и в блоке 27 нет переполнения, то на его выход проходит выходной сигнал блока 27 инкремента, если же в блоке 27 переполнение, то на его выход проходит выходной сигнал блока 33, который соответствует максимально возможному порядку. Если в блоке 18 производится вычитание и на выходе элемента ИЛИ 30, на выходы которого поступает выходной сигнал схемы анализа на нуль и сигнал переноса блока 24 вычитания, нет сигнала, сигнализирующего о выходе из нормального режима, то на выход мультиплексора 35 проходит выходной сигнал блока 24 вычитания.Если при вычитании в блоке 18 получается нулевой модуль мантиссы, то выходной сигнал дешифратора 25 нуля через элемент ИЛИ 30 поступает на1405049 третий управляющий вход мультиплексора 35 и обеспечивает прохождение на его выход выходного сигнала блока 34, который соответствует минимально возможному порядку. Этот же сигнал проходит на выход мультиплексора 35, если в блоке 24 вычитания возникает сигнал переноса, который также через элемент ИЛИ 30 проходит на третий управляющий вход мультиплексора 35,Выходные сигналы мультиплексоров 35 и 31 поступают соответственно на входы порядка результата и модуля мантиссы результата регистра 36 результата. Знак результата определяется сигналом мультиплексора 20, который через третий элемент РАВНОЗНАЧНОСТЬ 21 поступает на вход знака результата в регистре 36 результата, Элемент 21 пропускает сигнал со своего входа на выход без изменений, если при вычитании в сумматоре-вычитателе 18 не возник сигнал переноса, поступающий с второго выхода сумматора-вычитателя 18 на второй вход элемента 21. Если этот сигнал возникает (это говорит о том, что операнды имеют одинаковые порядки и модуль мантиссы второго операнда оказывается меньше модуля мантиссы первого операнда), то третий элемент 21 меняет свой входной сигнал на противоположный, который поступает с его выхода на вход знака результата регистра 36 результата. 8При появлении синхросигнала навходе 4 результат операции записывается в регистр 36 результата. Для1того, чтобы он появился на выходерегистра 37 состояния, необходимоподать на его первый вход сигнал раз-.решения, в противном случае выходырегистра 36 результата находятся в 10 третьем состоянии. На 2-й и 3-й входы регистра 37 состояния поступаютсигналы, свидетельствукнцие о переполнении порядка, исчезновении порядка или нулевой мантиссы, Они появляют ся на его выходе при подаче на егопервый. вход сигнала разрешения, впротивном случае его выходы находятсяв третьем состоянии. Необходимо отметить, что синхронно производятсятолько записи в регистры операндови регистр результата, остальные блокиработают в асинхронном режиме.При конкретном выполнении все блоки строятся на основе традиционных 25 регистров, триггеров, мультиплексоров, элементов логики и т.п. Наиболее целесообразным является выполнение всего устройства в виде одной мик.росхемы, При отсутствии такой возмож- ЗП ности предлагаемое устройство можетбыть выполнено на основе микросхемрегистров, триггеров, мультиплексоров, элементов логики и т.п.Блоки констант могут быть реализованы путем простого подсоединения 35соответствующих разрядов к шинам высокого и нулевого уровней.Подписное Зака Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 6/53 ВНИИП по 133035, Тираж 704 Государственного елам изобретений сква, Ж, Рауш комитета СССРи открытийкая наб., д, 4/

СмотретьЗаявка

3971561, 31.10.1985

ПРЕДПРИЯТИЕ ПЯ Р-6886, СПЕЦИАЛЬНОЕ ПРОЕКТНО-КОНСТРУКТОРСКОЕ БЮРО "ДИСКРЕТ" ОДЕССКОГО ПОЛИТЕХНИЧЕСКОГО ИНСТИТУТА

ГАЛЧЕНКОВ ОЛЕГ НИКОЛАЕВИЧ, АФАНАСЬЕВ ЮРИЙ АППОЛИНАРЬЕВИЧ, ЛАУБЕРГ НАДЕЖДА МИХАЙЛОВНА

МПК / Метки

МПК: G06F 7/50

Метки: двух, запятой, плавающей, суммирования, чисел

Опубликовано: 23.06.1988

Код ссылки

<a href="https://patents.su/7-1405049-ustrojjstvo-dlya-summirovaniya-dvukh-chisel-s-plavayushhejj-zapyatojj.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для суммирования двух чисел с плавающей запятой</a>

Предыдущий патент: Устройство для обработки цифровых данных

Следующий патент: Устройство для вычисления обратной величины нормализованной двоичной дроби

Случайный патент: Переключатель потоков