Процессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

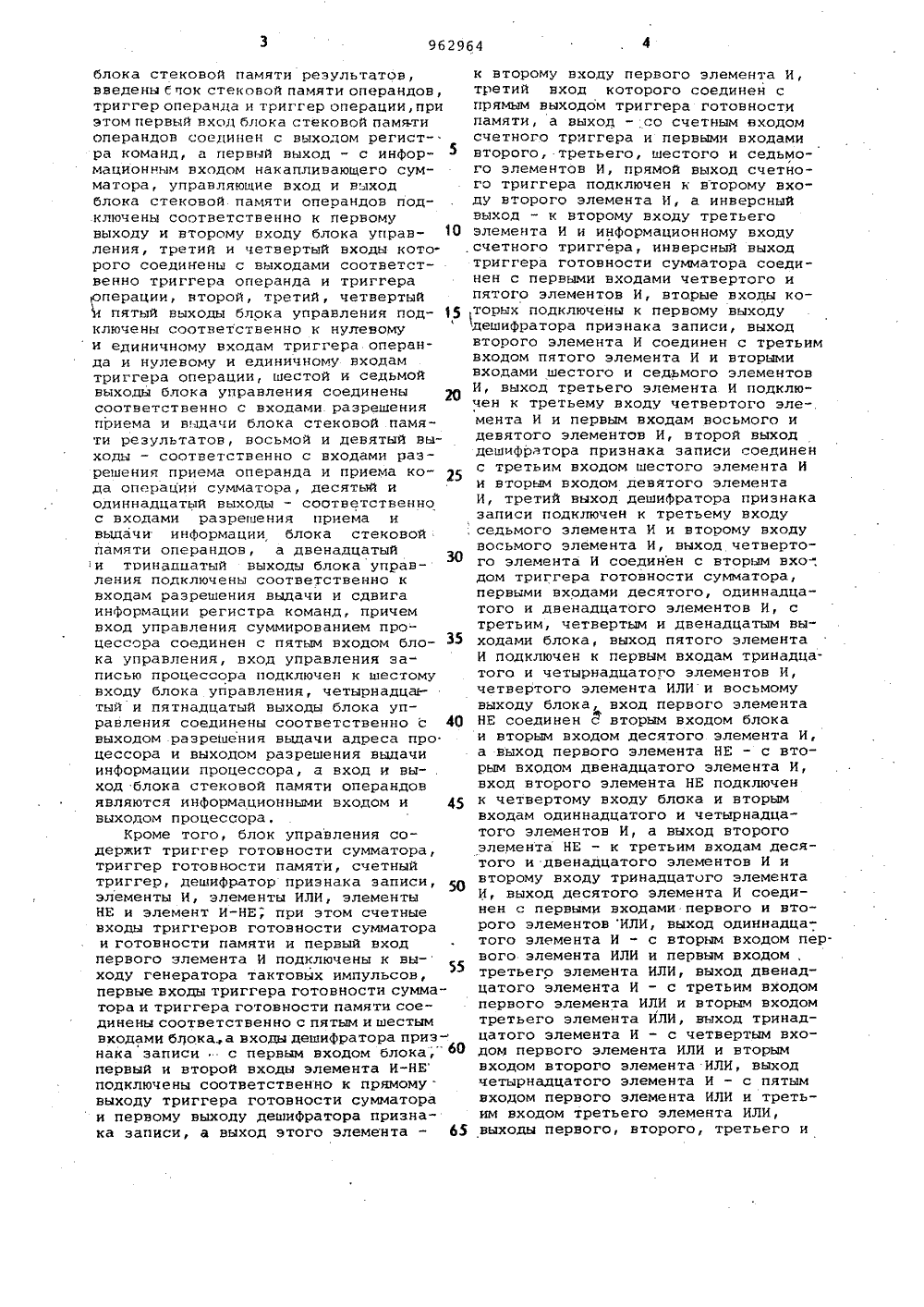

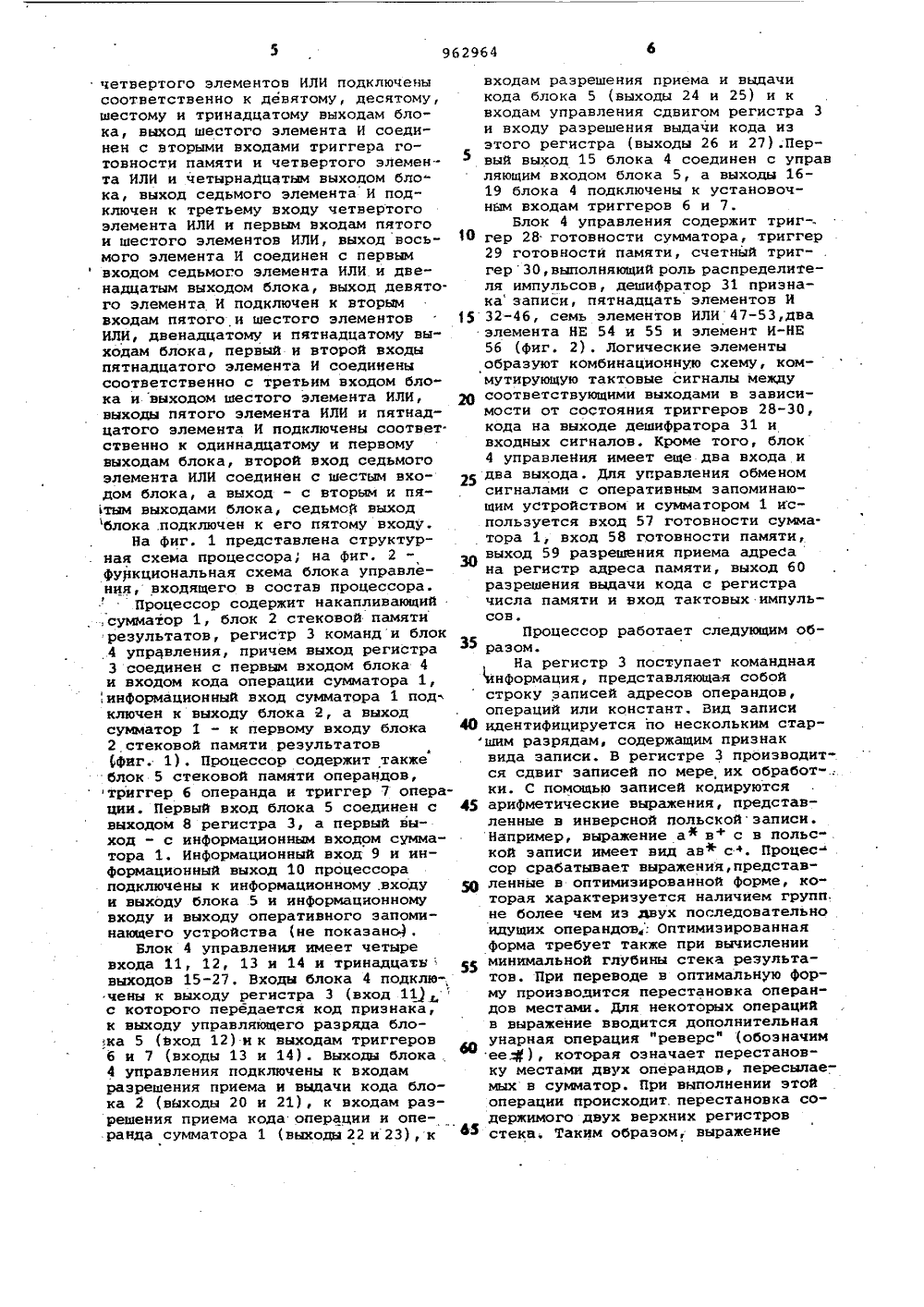

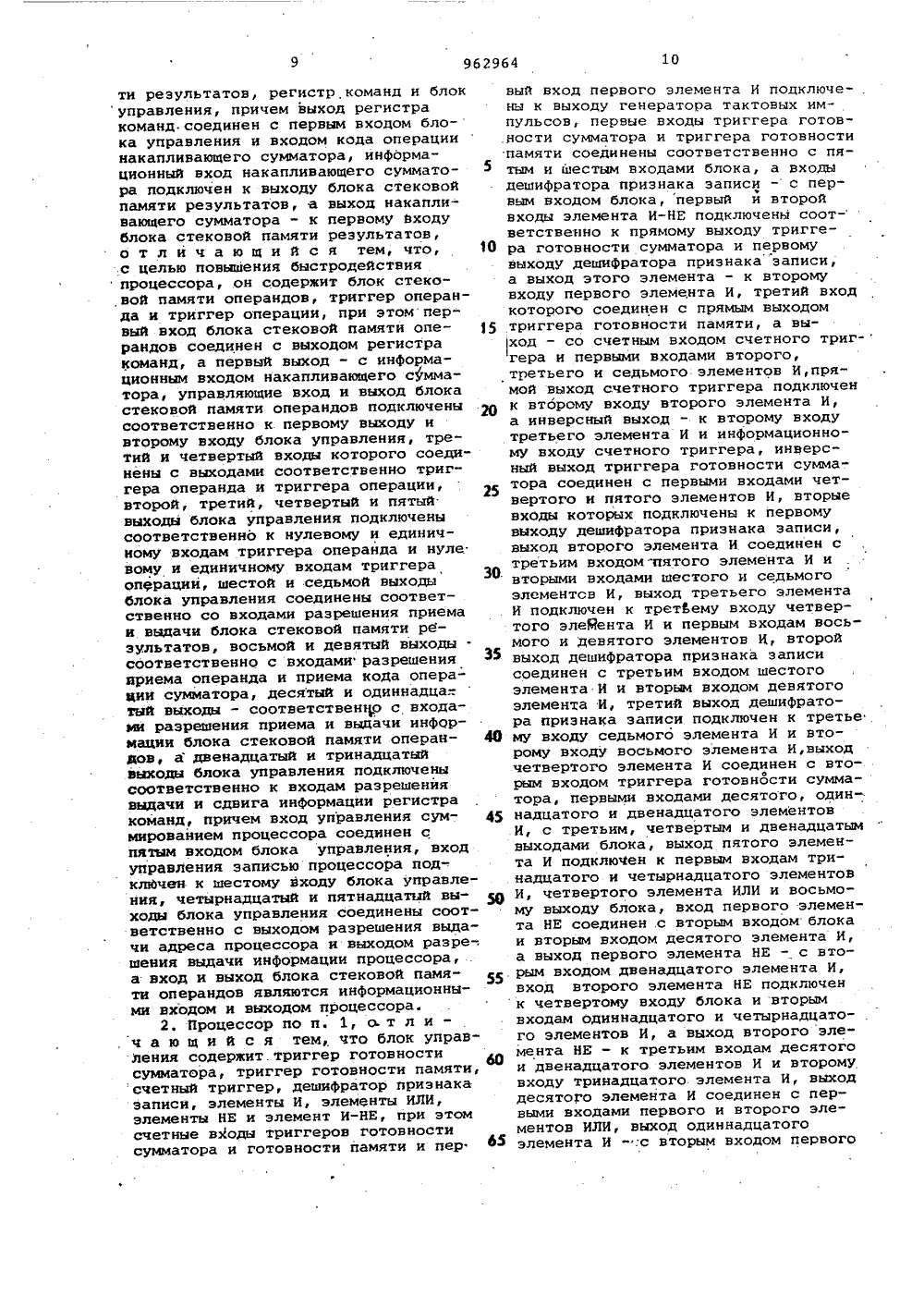

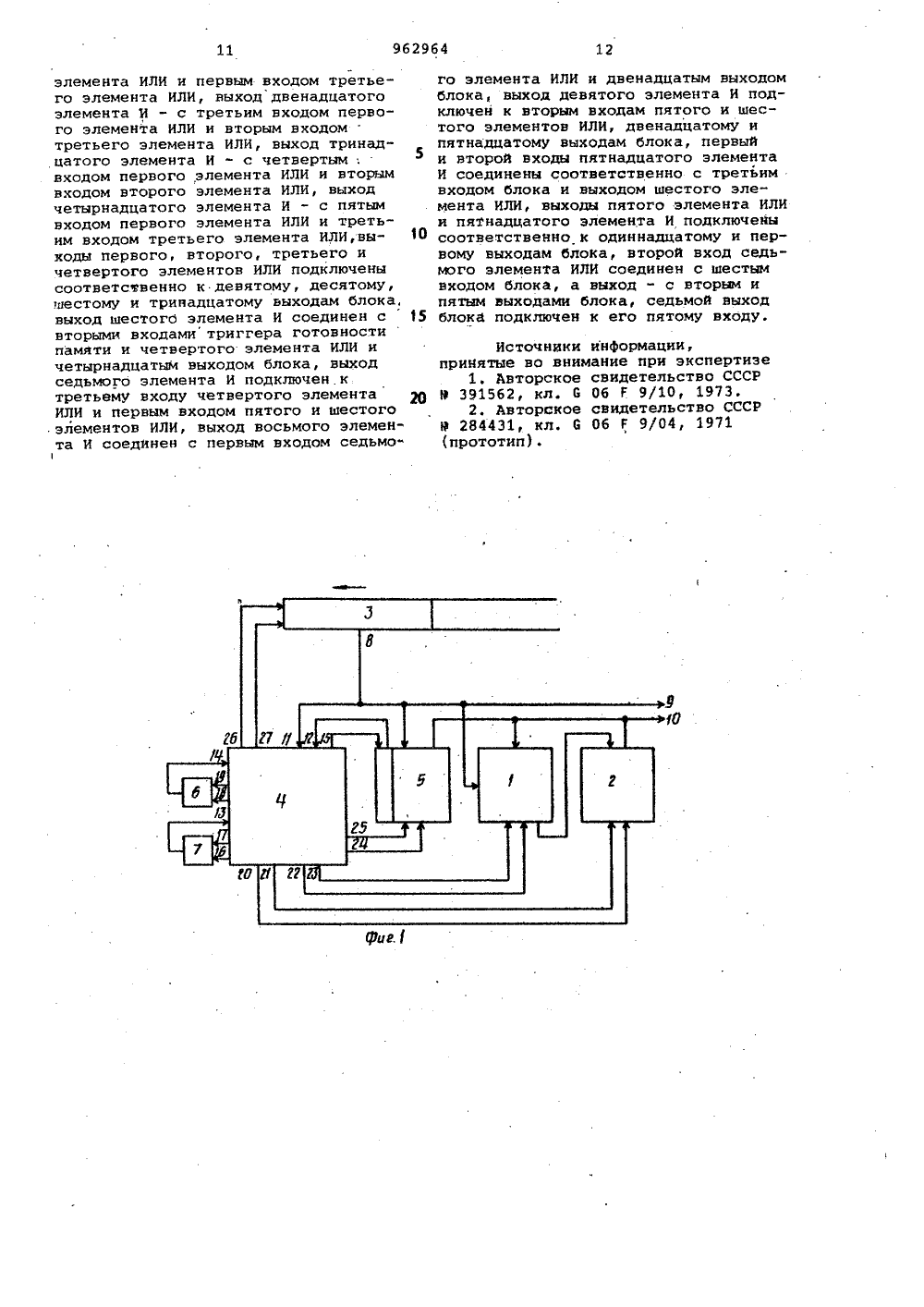

Союз СоветскихСоциалистическнхРеспублик ОПИСАНИЕ ИЗОБРЕТЕНИЯ 4 ф К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(23) Приоритет 61 06 Г 15/00 Государственный комитет СССР по делам изобретений и открытий(71) Заявитель Московский ордена Трудового Красного Знамени физический институт(54), ПРОЦЕССОР Изобретение относится к вычислительной технике,и может быть использовано в процессорах, в которых при меняются языки высокого уровня.Известен процессор, позволяющий вычислять арифметические выражения, представленные в польской записи, и содержащий регистр команд, блок режима работы, дешифратор адреса и дешиФратор кода операции, используемые для управления стековой памятью. С помощью этих блоков осуществляется загрузка операндов в стековую память и выполнение операций над ними в арифметическом устройстве 11..Недостаток этого процессора - низкое быстродействие.Наиболее близким к предлагаемому является процессор, который предназ- начен для вычисления выражений, пр дставленных в инверсной польской записи. Процессор содержит оперативное запоминающее устройство, стек результатов, стек адресов операндов, ре" гистр адреса, счетчик адреса стека результатов, счетчик операндов, ре-гистр команд и два регистра арифмети- ческого устройства. Командная информация состоит из слогов, содержащих коды операций и адреса операндов, упакованйых в непрерывную строку, поступающую на вход регистра команд. Адреса неиспользованных в данный моментоперандов погружаются в стек адресов,а используемые операнды .извлекаютсяиз оперативного запоминающего устройства и пересылаются в регистры арифметического устройства. Промежуточные результаты сохраняются в стекерезультатов 2.Недостатком известного процессора является низкое быстродействие,обусловленное последовательным характером обработки входной строки - подготовкой операндов и выполнением операций.Цель изобретения - повьхаение быстродействия процессора.Поставленная цель достигается тем,что.в процессор, содержащий накапливающий сумматор, блок стековой памяти результатов, регистр команд и блокуправления, причем выход регистра команд соединен с первым входом блока 25 управления и входом кода. операции на,капливающего сумматора, информационный вход накапливающего сумматораподключен к выходу блока стековойпамяти результатов, а выход накапли- ЗО вающего сумматора - к первому входу962964 блока стековой памяти результатов, введены Г чок стековой памяти операндов, триггер операнда н триггер операции,при этом первый вход блока стековой памяти операндов соединен с выходом регистра команд, а первый выход - с информационным входом накапливаюцего сумматора, управляюшие вход и выход блока стековой памяти операндов подключены соответственно к первому выходу и второму входу блока управ ления, третий и четвертый входы которого соединены с выходами соответственно триггера операнда и триггераперации, второй, третий, четвертыйпятый выходы блока управления под ключены соответственно к нулевомуи единичному входам триггера операнда и нулевому и единичному входам триггера операции, шестой и седьмой выходы блока управления соединены щ соответственно с входами разрешения приема и выдачи блока стековой памяти результатов, восьмой и девятый выходы - соответственно с входами разрешения приема операнда и приема ко да операции сумматора, десятый и одиннадцатый выходы - соответственнос входами разрешения приема ивыдачи информации блока стековойпамяти операндов, а двенадцатый и тринадиатый выходы блока управления подключены соответственно квходам разрешения выдачи и сдвигаинформации регистра команд, причемвход управления суммированием процессора соединен с пятым входом блока управления, вход управления записью процессора подключен к шестомувходу блока управления, четырнадца- тый и пятнадцатый выходы блока управления соединены соответственно с 40выходом раэреШения выдачи адреса процессора и выходом разрешения выдачиинформации процессора, а вход и вы- .ход блока стековой памяти операндовявляются информационными входом и 45выходом процессора.Кроме того, блок управления содержит триггер готовности сумматора, триггер готовности памяти, счетныйтриггер, дешифратор признака записи,элементы И, элементы ИЛИ, элементыНЕ и элемент И-НЕ; при этом счетныевходы триггеров готовности сумматораи готовности памяти и первый входпервого элемента И подключены к вы-ходу генератора тактовых импульсов, первые входы триггера готовности сумматора и триггера готовности памяти соединены соответственно с пятым и шестым входами блока, а входы дешифратора приз нака записи с первым входом блока, 60 первый и второй входы элемента И-НЕ подключены соответственно к прямому . выходу триггера готовности сумматораи первому выходу дешифратора признака записи, а выход этого элемента - 65 4к второму входу первого элемента И, третий вход которого соединен с прямым выходом триггера готовности памяти, а выход - со счетным входом счетного триггера и первыми входами второго, третьего, шестого и седьмого элементов И, прямой выход счетного триггера подключен к второму входу второго элемента И, а инверсный выход - к второму входу третьего элемента И и информационному входу счетного триггера, инверсный выход триггера готовности сумматора соединен с первыми входами четвертого и пятого элементов И, вторые входы которых подключены к первому выходу дешифратора признака записи, выход второго элемента И соединен с третьим входом пятого элемента И и вторымивходами шестого и седьмого элементовИ, выход третьего элемента И подключен к третьему входу четвертого эле-.мента И и первым входам восьмого идевятого элементов И, второй выходдешифрратора признака записи соединенс третьим входом шестого элемента Ии вторым входом девятого элементаИ, третий выход дешифратора признаказаписи подключен к третьему входуседьмого элемента И и второму входувосьмого элемента И, выход четвертого элемента И соединен с вторым вхо-,дом триггера готовности сумматора,первыми входами десятого, одиннадцатого и двенадцатого элементов И, стретьим, четвертым и двенадцатым выходами блока, выход пятого элементаИ подключен к первым входам тринадцатого и четырнадцатого элементов И,четвертого элемента ИЛИи восьмомувыходу блока, вход первого элементаНЕ соединен с вторым входом блокаи вторым входом десятого элемента И,а выход первого элемента НЕ - с вторым входом двенадцатого элемента И,вход второго элемента НЕ подключенк четвертому входу блока и вторымвходам одиннадцатого и четырнадцатого элементов И, а выход второгоэлемента НЕ - к третьим входам десятого и двенадцатого элементов И ивторому входу тринадцатого элементаИ, выход десятого элемента И соединен с первыми входами первого и второго элементов ИЛИ, выход одиннадцатого элемента И - с вторым входом пер. вого элемента ИЛИ и первым входом,третьего элемента ИЛИ, выход двенадцатого элемента И - с третьим входомпервого элемента ИЛИ и вторым входомтретьего элемента ИЛИ, выход тринадцатого элемента И - с четвертым входоМ первого элемента ИЛИ и вторымвходом второго элемента ИЛИ, выходчетырнадцатого элемента И - с пятымвходом первого элемента ИЛИ и третьим входом третьего элемента ИЛИ,выходы первого, второго, третьего ивходам разрешения приема и выдачикода блока 5 (выходы 24 и 25) и квходам управления сдвигом регистра 3и входу разрешения выдачи кода изэтого регистра (выходы 26 и 27).Первый выход 15 блока 4 соединен с Управляющим входом блока 5, а выходы 1619 блока 4 подключены к установочным входам триггеров 6 и 7.Блок 4 управления содержит триг-.10 гер 28 готовности сумматора, триггер29 готовности памяти, счетный триггер 30,выполняющий роль распределителя импульсов, дешифратор 31 признака записи, пятнадцать элементов И 1532-46, семь элементов ИЛИ 47-53,дваэлемента НЕ 54 и 55 и элемент И-НЕ56 (фиг, 2) . Логические элементыобразуют комбинационную схему, коммутирующую тактовые сигналы между 2 О соответствующими выходами в зависимости от состояния триггеров 28-30,кода на выходе дешифратора 31 ивходных сигналов. Кроме того, блок4 управления имеет еще два входа и 25 два выхода. Для Управления обменомсигналами с оперативным запоминающим устройством и сумматором 1 используется вход 57 готовности сумма.тора 1, вход 58 готовности памяти,выход 59 разрешения приема адресана регистр адреса памяти, выход 60разрешения выдачи кода с регистрачисла памяти и вход тактовых импульсов.Процессор работает следующим обЗ 5 разом.На регистр 3 поступает команднаянформация, представляющая собойстроку записей адресов операндов,операций или констант. Вид записи 40 идентифицируется по нескольким старторая характеризуется наличием групп, не более чем из двух последовательно идущих операндов,: Оптимизированная Форма требует также при вычислении 55 минимальной глубины стека Результатов. При переводе в оптимальную форму производится перестановка операндов местами. Для некоторых операций в выражение вводится дополнительная унарная операция "реверс" (обозначим ееЩ ), которая означает перестановку местами двух операндов, пересылаемых в сумматор. При выполнении этой операции происходит. перестановка содержимого двух верхних регистров ф 5 стека. Таким образом, выражение четвертого элементов ИЛИ подключены соответственно к девятому, десятому, шестому и тринадцатому выходам блока, выход шестого элемента И соединен с вторыми входами триггера готовности памяти и четвертого элемента ИЛИ и четырнадцатым выходом бло" ка, выход седьмого элемента И подключен к третьему входу четвертого элемента ИЛИ и первым входам пятого и шестого элементов ИЛИ, выход восьмого элемента И соединен с первым входом седьмого элемента ИЛИ и двенадцатым выходом блока, выход девятого элемента И подключен к вторым входам пятого и шестого элементов ИЛИ, двенадцатому и пятнадцатому выходам блока, первый и второй входы пятнадцатого элемента И соединены соответственно с третьим входом блока и выходом шестого элемента ИЛИ, выходы пятого элемента ИЛИ и пятнадцатого элемента И подключены соответ. ственно к одиннадцатому и первому выходам блока, второй вход седьмого элемента ИЛИ соединен с шестым входом блока, а выход - с вторым и пятым выходами блока, седьмой выход блока .подключен к его пятому входу.На фиг. 1 представлена структурная схема процессора, на фиг. 2 фуркциональная схема блока управления, входящего в состав процессора.Процессор содержит накапливающий ,сумматор 1, блок 2 стековой памяти результатов, регистр 3 команди блок 4 управления, причем выход регистра 3 соединен с первым входом блока 4 и входом кода операции сумматора 1, информационный вход сумматора 1 под ключен к выходу блока 2, а выход сумматор 1 - к первому входу блока 2 стековой памяти результатов фиг. 1). Процессор содержит также блок 5 стековой памяти операндов, триггер б операнда и триггер 7 операции. Первый вход блока 5 соединен с 4 выходом 8 регистра 3, а первый выход " с информационным входом сумматора 1, Информационный вход 9 и инФормационный выход 10 процессора подключены к информационному, входу и выходу блока 5 и информационному входу и выходу оперативного запоминающего устройства (не показаноБлок 4 управления имеет четыре входа 11, 12, 13 и 14 и тринадцатывыходов 15-27. Входы блока 4 подклю-.,чены к выходу регистра 3 (вход 11) с которого передается код признака, к выходу управляющего разряда бло,ка 5 (вход 12) и к выходам триггеров б и 7 (входы 13 и 14). Выходы блока 4 управления подключены к входам разрешения приема и выдачи кода блока 2 (выходы 20 и 21), к входам разрешения приема кода операции и операнда сумматора 1 (выходы 22 и 23), к шим разрядам, содержащим признак вида записи. В регистре 3 производится сдвиг записей по мере их обработ-ки. С помощью записей кодируютсяарифметические выражения, представленные в инверсной польской записи.Например, выражение аф в+ с в польской записи имеет вид ав+ с. Процессор срабатывает выражения, представленные в оптимизированной форме, ко 962964я/ ( а ф Ь. с" д ) будет иметь вид авфсд к ++ ХПри обнаружении признака операндав регистре 3 блок 4 управления сбрасывает триггер 6 в нуль.Адрес операн-. 5 да передается на выход регистра 3, а код операнда со входа 9 поступает в блок 5. Блок 4 анализирует состояние триггера 7 и записывает в управ" ляющнй разряд блока 5 нуль если триггер 7 находится в нулевом состоя- ниК, после чего триггерустанавливаЕтся в единицу, Это означает, что, обнаружен первый операнд пары, Если триггер 7 находится в единице, то в управляющий разряд записывается единица, что означает обнаружение второго операнда пары.При обнаружении нрйзнака констан. ты производится тот же набор действий: сброс триггера 6 в нуль, анализ 2 О состояния триггера 7 и запись приз". нака парности з управляющий разряд блока 5, но значение константы передается в блек 5 с регистра 3, При обнаружении признака операции код операции передается на управляющий вход сумматора 1. Далее производится загрузка операндов. Если триггер б находится в единице, т.е. предыдущей записью была операция, то оба ЗО операнда извлекаются из блока 2; если он находится в нуле, то первый операнд извлекается иэ блока 5.Если признак парности равен единице, то второй операнд также извлекается из блока 5, если нулю, то он извлекается из блока 2. Результат выполнения операции зайисывается в блок 2.Послеэтого триггер 6 устанавливается в единицу, а триггер 7 - в нуль, Во время выполнения очередной операции блок 4 про" изводит сдвиг информации в регистре3 н анализ признака следующей записи.Если запись - константа, тоее значение пересылается в блок 5, если опе- ранд, то производится извлечение его 45 содержиМого из оперативного запоми" .нающего устройства, т.е. подготовка юперандов, как описано выше,Блок 4 .управления работает следующим образом. В исходном состоянии 50 триггеры б и 7 находятся в нуле, а триггеры 28-30 - в единице. Дешифратор 31 выдает на нулевом выходе сигнал соответствующий признаку кодаоперации, на выходе "1" ; адресу операнда, на выходе "2" - константе.Обработка каждого вида записи осуществляется эа два такта, между которыми может быть пауза, связанная с ожиданием готовности памяти. Появление . Япризнака адреса операнда (сигнал иавыходе "1" дешифратора 31) приводитк передаче адреса на регистр адреса оперативного запоминающего устройст" ва (сигнал на выходе 59), а триггер 29 устанавливается в нуль, блокируя дальнейшее поступление тактовых импульсов. Сигнал готовности памяти со входа 58 устанавливает триггер 29 в единицу, разрешая поступление очередного импульса на счетный вход триггера 30. Во втором такте производится прием кода операнда с регистра числа, оперативного запоминающего устройства в блок 5 (по сигналам с выходов 26 и 60) и сдвиг кода в регистре 3. Появление признака константы (сигнал на выходе "1" дешифратора) вызывает передачу кода константы из регистра 3 в блок 5 по сигна- лам с выходов 25 и 27 у . Во втором такте производится сдвиг кода в регистре 3 на длину кода константы. Так как коды адреса, константы и операции могут иметь разную длину, то блок 4 имеет три различных выхода для управления сдвигом, обозначенных общим номером 26. Появление признака кода операции приводит к тому, в ,что в зависимости от состояния триггера б 1(вход 14 ) производится или прием первого, а затем второго операнда (по сигналу со входа 12) в сумматор 1 иэ блока 5 (пс сигналам на выходах 20 и 23),или из разных блоков стековой памяти (по сигналам на выходах 20 и 23 ф 23 и 24), Затем триггер 28 устанавливается в единицу, Далее блок управления может продолжать анализ признаков и подготовку операндов. Действия по обработке следующей записи кода операции при отсутствии готовности сумматора 1 блокируются триггером 28 и элементом И-НЕ 56. Каждая передача информации сопровождается выдачей двух сигналов, разрешения выдачи и разрешения приема на управляющие входы источника и приемника (кроме выдачи иэ сумматора). При вычислении выражения авсдф + ;ф выборка операндов с и д может быть совмещена с умножением, а выборка операнда г со сложением.Таким образом, введение в процессор блока стековой памяти операндов глубиной в два регистра и двух триггеров, характеризующих вид предшествующей записи позволяет повысить его быстродействие за счет совмещения времени выборки операндов иэ оперативного запоминающего устройства с выпол- . нением предыдущей операции. При отношении между временем выборки иэ оперативного запоминающего устройства и средним временем выполнения операции 1:1 производительность предлагаемого процессора на 20 больше,чем известного процессора. Формула изобретения1. Процессор, содержащий накапливающий сумматор, блок стековой памя 9629 б 4ти результатов, регистр команд и блокуправления, причем выход регистра команд соединен с первым входом блока управления и входом кода операциинакапливающего сумматора, информационный вход накапливающего сумматора подключен к выходу блока стековойпамяти результатов, а выход накапливающего сумматора " к первому входу блока стековой памяти результатов, о т л и ч а ю щ и й с я тем, что, ,с целью повышения быстродействия процессора, он содержит блок стековой памяти операндов, триггер операнда и триггер операции, при этомпервый вход блока стековой памяти операндов соединен с выходом регистра команд, а первый выход - с информационным входом накапливающего сумматора, управляющие вход и выход блока стековой памяти операндов подключенысоответственно к первому выходу и второму входу блока управления, третий и четвертый входы которого соедииены с выходами соответственно триггера операнда и триггера операции, второй, третий, четвертый и пятый выходы блока управления подключены соответственно к нулевому и единичиому входам триггера операнда и нулевому и единичному входам триггера операции, шестой и седьмой выходы блока управления соединены соответственно со входами разрешения приема и вщачи блока стековой памяти результатов, восьмой и девятый выходы . соответственно с входами разрешения приема операнда и приема кода операции сумматора, десятый и одиннадца.-. тый выходы - соответственно с входаии разрешения приема и выдачи информации блока стековой памяти операндов, а двенадцатый и тринадцатый выходы блока управления подключены соответственно к входам разрешения выдачи и сдвига информации регистра команд, причем вход управления суммированием процессора соединен спятым входом блока управления, входуправления записью процессора подключен к шестому входу блока управления, четырнадцатый и пятнадцатый выходы блока управления соединены соответственно с выходом разрешения выдачи адреса процессора и выходом разре-,шения выдачи информации процессора, а вход и выход блока стековой памяти операндов являются информационными входом и выходом процессора.2. Процессор по п. 1, о.т л и -ч а ю щ и й с я тем, что блок управления содержит. триггер готовностисумматора, триггер готовности памяти,счетный триггер, дешифратор признаказаписи, элементы И, элементы ИЛИ,элементы НЕ и элемент И-НЕ, при этомсчетные воды триггеров готовностисумматора и готовности памяти и пер вый вход первого элемента И подключе- .ны к выходу генератора тактовых импульсов, первые входы триггера готовности сумматора и триггера готовностипамяти соединены соответственно с пя 5 тым и шестым входами блока, а входыдешифратора признака записи - с первым входом блока, первый й второйвходы элемента И-НЕ подключены соответственно к прямому выходу тригге 10 ра готовности сумматора и первомувыходу дешифратора признака записи,а выход этого элемента - к второмувходу первого элемента И, третий входкоторого соединен с прямым выходом15 триггера готовности памяти, а выход - со счетным входом счетного триг-гера и первыми входами второго,третьего и седьмого элементов И,прямой выход счетного триггера подключен.2 О к второму входу второго элемента И,а инверсный выход - к второму входутретьего элемента И и информационному входу счетного триггера, инверсный выход триггера готовности сумматора соединен с первыми входами четвертоГо и Пятого элементов И, вторыевходы которых подключены к первомувыходу дешифратора признака записи,. выход второго элемента И соединен стретьим входом "пятого элемента И ивторыми входами шестого и седьмогоэлементов И, выход третьего элемента. И подключен к третьему входу четвертого элейента И и первым входам восьмого и девятого элементов И, второйвыход дешифратора признака записисоединен с третьим входом шестогоэлемента И и вторым входом девятогоэлемента И, третий выход дешифратора признака записи подключен к третье46 му входу седьмого элемента И и вто"рому входу восьмого элемента И,выходчетвертого элемента И соединен с вторым входом триггера готовности сумматора, первыми входами десятого, одиннадцатого и двенадцатого элементовИ, с третьим, четвертым и двенадцатымвыходами блока, выход пятого элемента И подключен к первым входам тринадцатого и четырнадцатого элементов59 И, четвертого элемента ИЛИ и восьмому выходу блока, вход первого элемента НЕ соединен .с вторым входом блокаи вторым входом десятого элемента И,а выход первого элемента НЕ - с вторым входом двенадцатого элемента И,вход второго элемента НЕ подключенк четвертому входу блока и вторымвходам одиннадцатого и четырнадцатого элементов И, а выход второго элемента НЕ - к третьим входам десятогои двенадцатого элементов И и второмувходу тринадцатого элемента И, выходдесятого элемента И соединен с первыми входами первого и второго элементов ИЛИ, выход одиннадцатогоф 5 элемента И в :с вторым входом первого12 962964 9 ие. элемента ИЛИ и первым входом третьего элемента ИЛИ, выход двенадцатогоэлемента И - с третьим входом первого элемента ИЛИ и вторым входомтретьего элемента ИЛИ, выход тринад,цатого элемента И - с четвертым,входом первого, элемента ИЛИ и вторымвходом второго элемента ИЛИ, выходчетырнадцатого элемента И - с пятымвходом первого элемента ИЛИ и третьим входом третьего элемента ИЛИ,выходы первого, второго, третьего ичетвертого элементов ИЛИ подключенысоответственно к девятому, десятому,шестому и тринадцатому выходам блока,выход шестого элемента И соединен свторыми входамитриггера готовностипамяти и четвертого элемента ИЛИ ичетырнадцатым выходом блока, выходседьмого элемента И подключен ктретьему входу четвертого элементаИЛИ и первым входом пятого и шестогоэлементов ИЛИ, выход восьмого элемента И соедннен с первым входом седьмо1 го элемента ИЛИ и двенадцатым выходомблока выход девятого элемента И подключен к вторым входам пятого и шестого элементов ИЛИ, двенадцатому ипятнадцатому выходам блока, первыйи второй входы пятнадцатого элементаИ соединены соответственно с третьимвходом блока и выходом шестого элемента ИЛИ, выходы пятого элемента ИЛИи пятнадцатого элемента И подключеиы 1 О соответственно к одиннадцатому и первому выходам блока, второй вход седьмого элемента ИЛИ соединен с шестымвходом блока, а выход - с вторым ипятым выходами блока, седьмой выход 15 блока подключен к его пятому входу. Источники инФормации,принятые во внимание при экспертизе1, Авторское свидетельство СССР2 О 9 391562, кл. С 06 Г 9/10, 1973,2. Авторское свидетельство СССР9 284431, кл. С 06 Г 9/04, 1971Заказ Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 5 ЛО Ти ВНИИПИ Госудапо делам и 113035, Москв ж 731твеиного коми бретений и отЖ, Раушск Подписта СССРытийнаб, д. 4

СмотретьЗаявка

3228970, 04.01.1981

МОСКОВСКИЙ ОРДЕНА ТРУДОВОГО КРАСНОГО ЗНАМЕНИ ИНЖЕНЕРНО ФИЗИЧЕСКИЙ ИНСТИТУТ

СТЕПАНОВ АЛЕКСЕЙ НИКОЛАЕВИЧ, ГАНЬКИН АЛЕСАНДР ЛЬВОВИЧ, ЗАХАРЕВИЧ НИКОЛАЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 15/00

Метки: процессор

Опубликовано: 30.09.1982

Код ссылки

<a href="https://patents.su/7-962964-processor.html" target="_blank" rel="follow" title="База патентов СССР">Процессор</a>

Предыдущий патент: Устройство для управления памятью

Следующий патент: Многопроцессорная вычислительная система

Случайный патент: Привод конвейерного поезда