Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

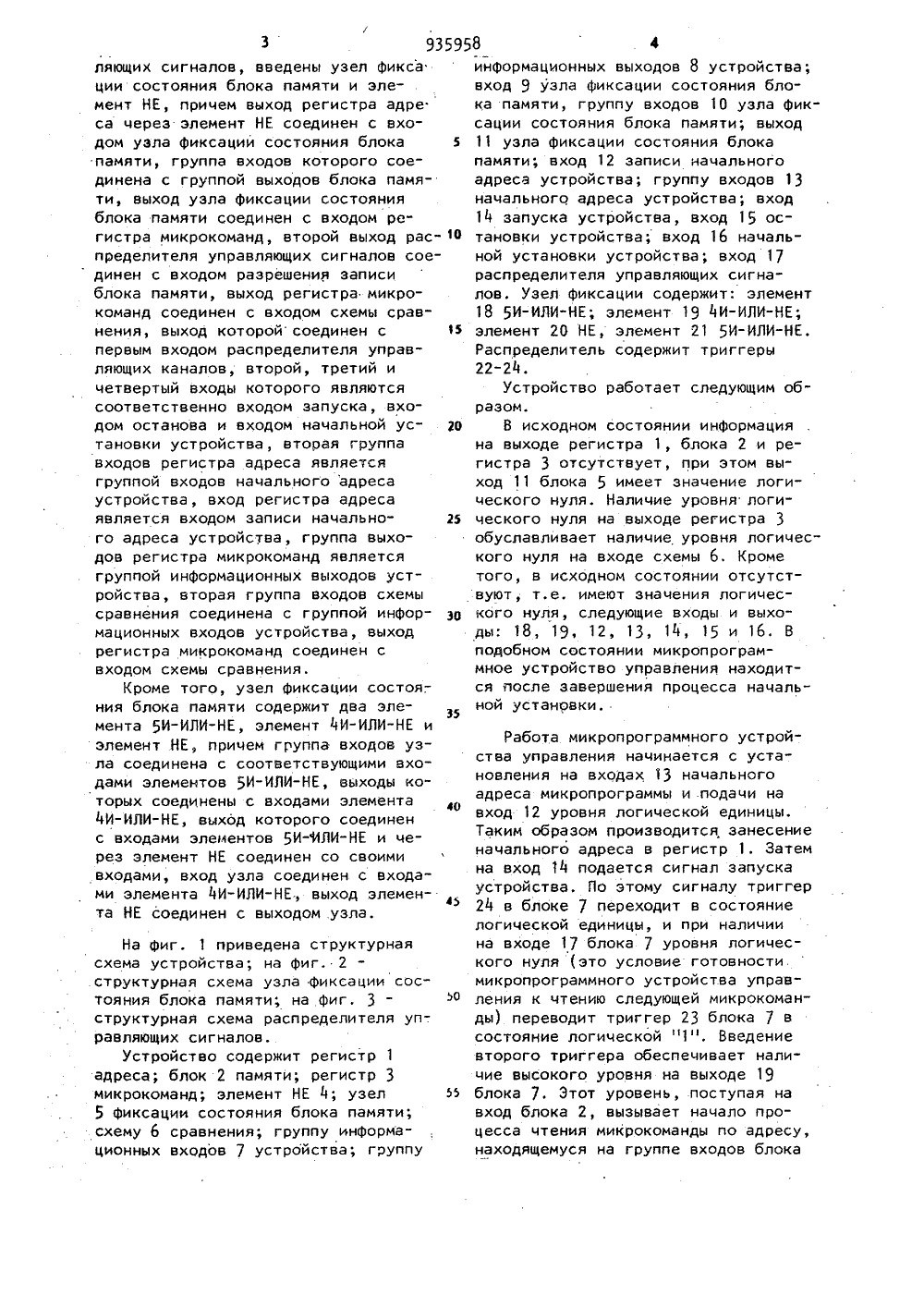

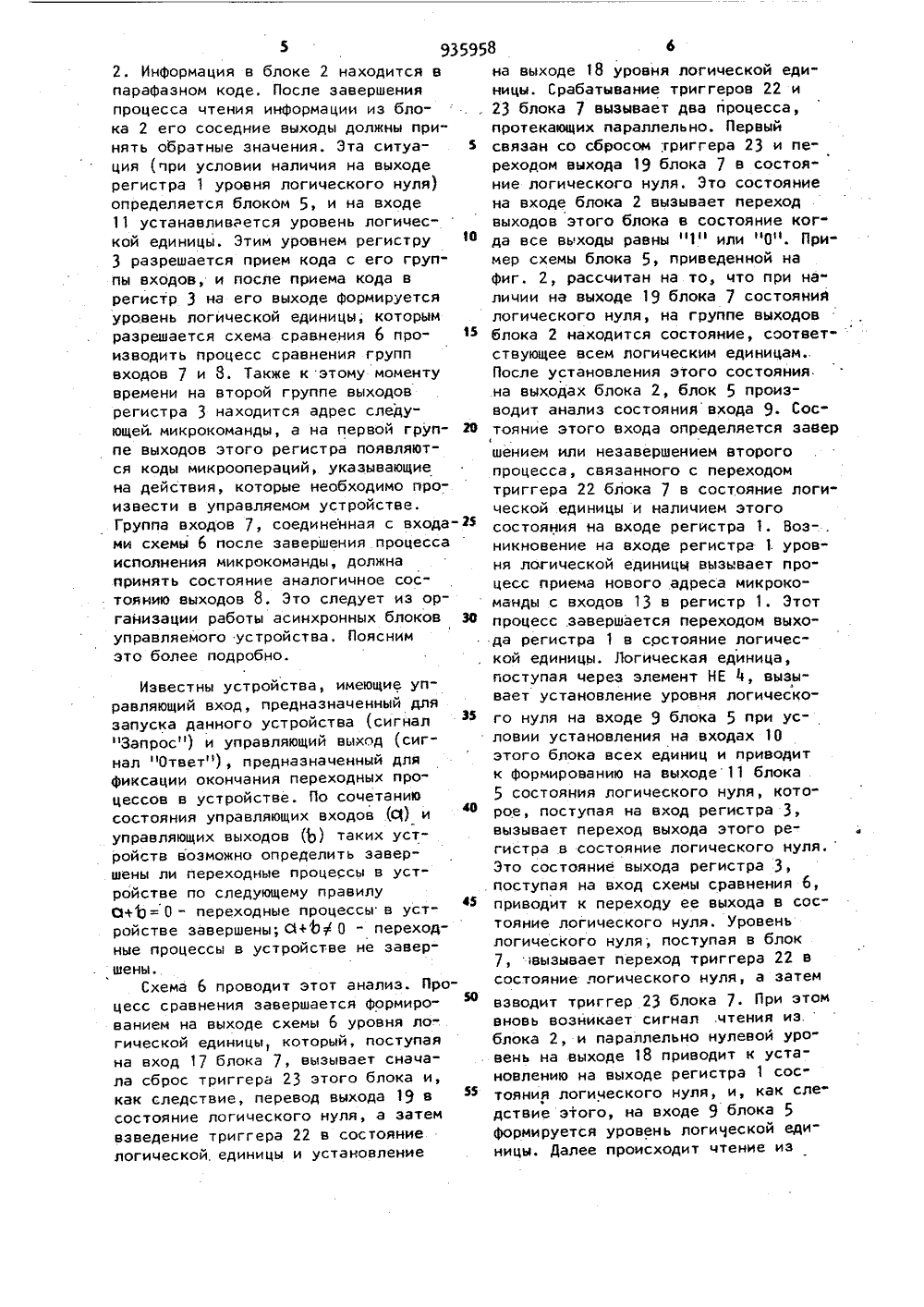

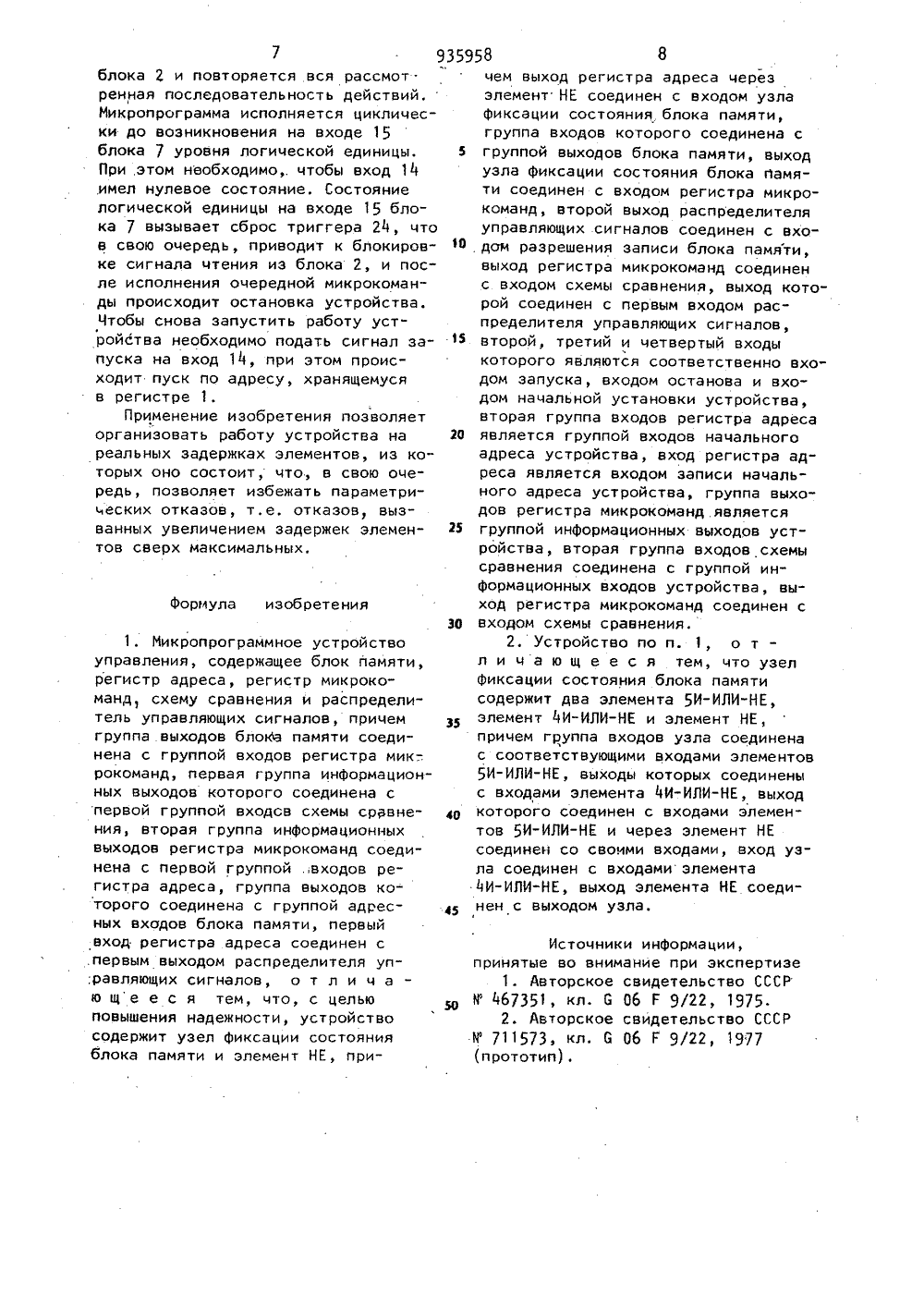

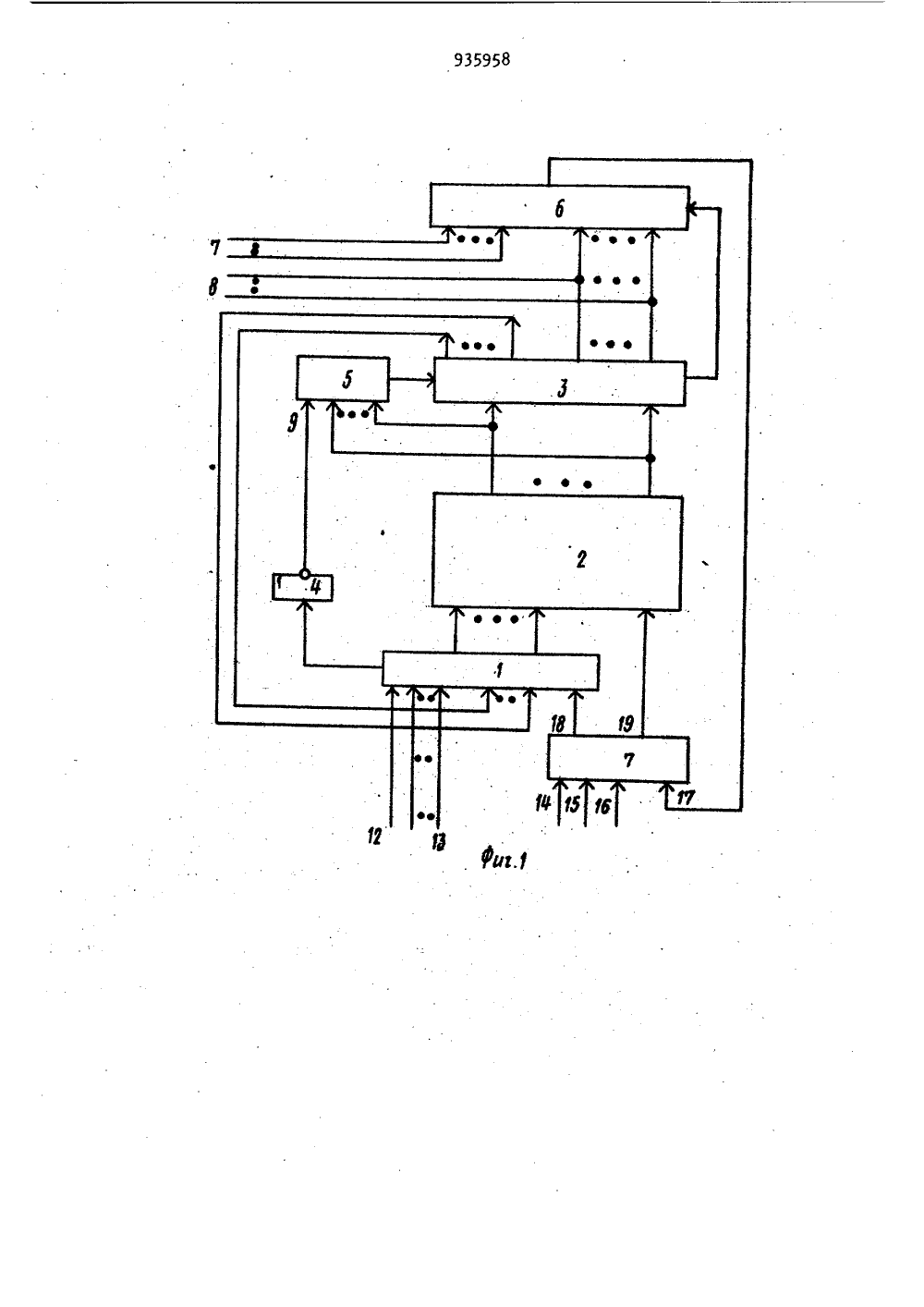

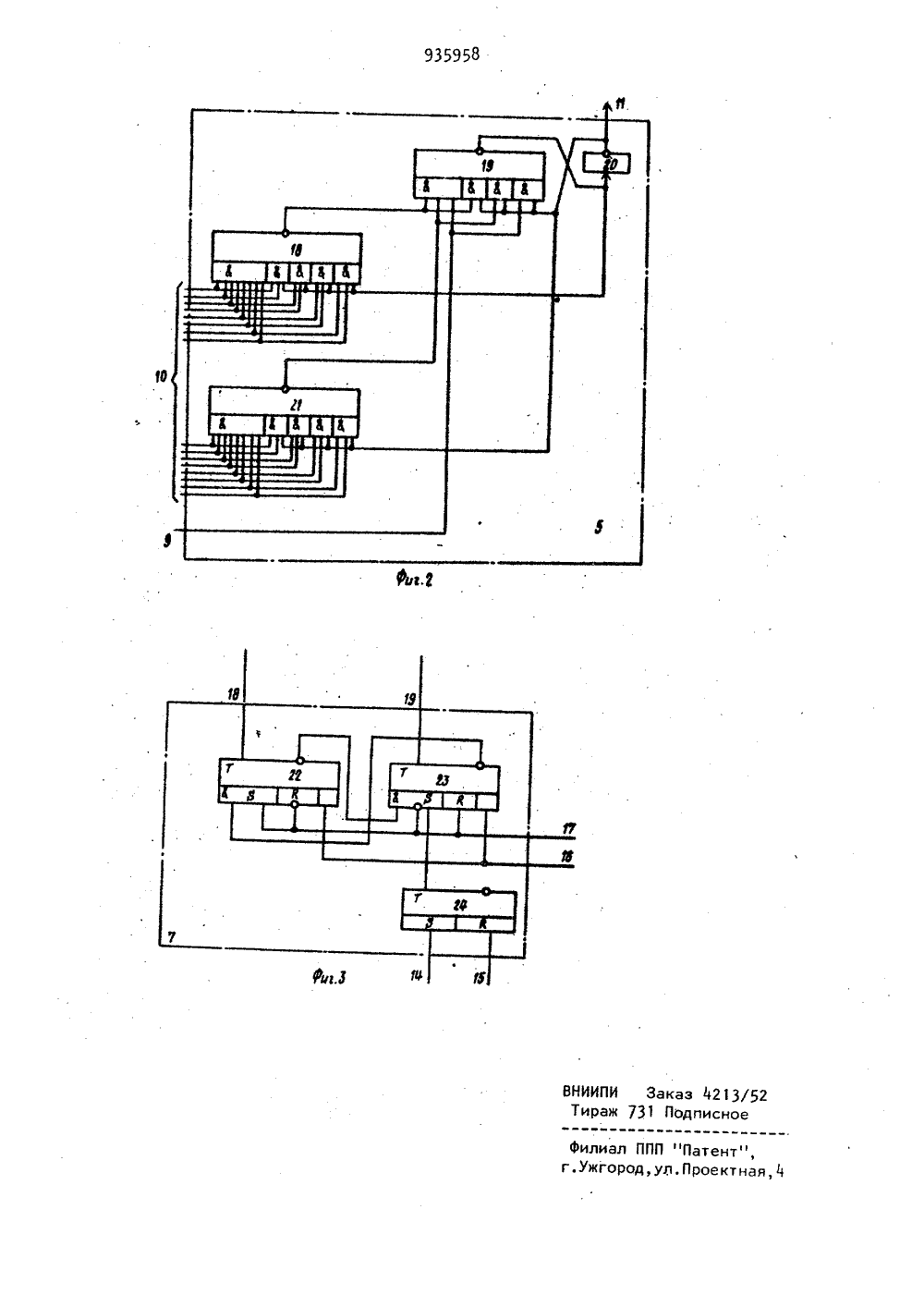

О П И С А Н И Е (п)935958ИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоветскикСоциаиистическиаРесиубиик(5 )М. Кл. с присоединением заявки,%(23) Приоритет 6 06 Г 9/22 Ркударс 1 вапаб квинтет СИР ае авви взв 3 ретевнй и епуытвй(5 Ь) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ Изобретение относится к вычислительной технике и может быть использовано в качестве устройства управления цифровых вычислительных машин (ЦВМ).Известно микропрограммное уст- . ройство управления, содержащее блок памяти микропрограмм, адресный регистр, регистр микрокоманд, дешифраторы, линии задержки и логическиеФО схемы. Устройство вырабатывает набор сигналов (микроопераций) управляющих работой различных блоков и устройств ЦВМ.Недостаток известного устройства1 состоит в том, цто оно обладает низкой надежностью. Наиболее близким к изобретению по технической сущности и достигае 20 мому результату является микропрог" раммное устройство с контролем переходов, содержащее блок памяти микропрограмм, адресный регистр, регистр микрокоманды, схему сравнения, регистр сдвига и блок управления 21,Однако у этого устройства низкая надежность.Цель изобретения - повышение надежности устройства.Поставленная цель достигается тем, цто в микропрограммное устройство управления, содержащее блок памяти, регистр микрокоманд, схему сравнения и распределитель управляющих сигналов, причем группа выходов блока памяти соединена с группой входов регистра микрокоманд, первая группа информационных выходов которого соединена с первой группой входов схемы сравнения, вторая группа инФормационных выходов регистра микро- команд соединена с первой группой входов регистра адреса, группа выходов которого соединена с группой адресных входов блока памяти, первый вход регистра адреса соединен с первым выходом распределителя управ 3 9359 ляющих сигналов, введены узел фикса ции состояния блока памяти и элемент НЕ, причем выход регистра адре са через элемент НЕ соединен с входом узла фиксации состояния блока 5 памяти, группа входов которого соединена с группой выходов блока памяти, выход узла фиксации состояния блока памяти соединен с входом регистра микрокоманд, второй выход рас пределителя управляющих сигналов сое динен с входом разрешения записи блока памяти, выход регистра микро- команд соединен с входом схемы сравнения, выход которой соединен с 35 первым входом распределителя управляющих каналов, второй, третий и четвертый входы которого являются соответственно входом запуска, входом останова и входом начальной ус О тановки устройства, вторая группа входов регистра адреса является группой входов начального адреса устройства, вход регистра адреса является входом записи начально го адреса устройства, группа выходов регистра микрокоманд является группой информационных выходов устройства, вторая группа входов схемы сравнения соединена с группой инфор- зо мационных входов устройства, выход регистра микрокоманд соединен с входом схемы сравнения.Кроме того, узел фиксации состоя; ния блока памяти содержит два элемента 5 И-ИЛИ-НЕ, элемент 4 И-ИЛИ-НЕ и элемент НЕ, причем группа входов узла соединена с соответствующими входами элементов 5 И-ИЛИ-НЕ, выходы которых соеди.нены с входами элемента 4 И-ИЛИ-НЕ, выход которого соединен с входами элементов 5 И-МЛИ-НЕ и через элемент НЕ соединен со своими входами, вход узла соединен с входами элемента 4 И-ИЛИ-НЕ., выход элемента НЕ соединен с выходом узла. На фиг. 1 приведена структурная схема устройства; на фиг. 2структурная схема узла фиксации состояния блока памяти; на фиг. 3 - структурная схема распределителя управляющих сигналов.Устройство содержит регистр 1 адреса; блок 2 памяти; регистр 3 микрокоманд; элемент НЕ 4; узел 55 5 фиксации состояния блока памяти;схему 6 сравнения; группу информационных входов 7 устройства; группу информационных выходов 8 устройства; вход 9 узла фиксации состояния блока памяти, группу входов 10 узла фиксации состояния блока памяти; выход 11 узла фиксации состояния блока памяти; вход 12 записи начального адреса устройства; группу входов 13 начального адреса устройства; вход 14 запуска устройства, вход 15 остановки устройства; вход 16 начальной установки устройства; вход 17 распределителя управляющих сигналов. Узел фиксации содержит: элемент 18 5 И-ИЛИ-НЕ; элемент 19 4 И-ИЛИ-НЕ; элемент 20 НЕ, элемент 21 5 И-ИЛИ-НЕ, Распределитель содержит триггеры 22-24.Устройство работает следующим образом.В исходном состоянии информация на выходе регистра 1, блока 2 и регистра 3 отсутствует, при этом выход 11 блока 5 имеет значение логического нуля. Наличие уровня логического нуля на выходе регистра 3 обуславливает наличие уровня логического нуля на входе схемы 6. Кроме того, в исходном состоянии отсутствуют, т.е, имеют значения логического нуля, следующие входы и выходы: 18, 19 12, 13, 14, 15 и 16. В подобном состоянии микропрограммное устройство управления находится после завершения процесса начальной установки. Работа микропрограммного устройства управления начинается с установления на входах 13 начального адреса микропрограммы и подачи на вход 12 уровня логической единицы. Таким образом производится занесение начального адреса в регистр 1. Затем на вход 14 подается сигнал запуска устройства. По этому сигналу триггер 24 в блоке 7 переходит в состояние логической единицы, и при наличии на входе 17 блока 7 уровня логического нуля (это условие готовности. микропрограммного устройства управления к чтению следующей микрокоманды) переводит триггер 23 блока 7 в состояние логической "1". Введение второго триггера обеспечивает наличие высокого уровня на выходе 19 блока 7. Этот уровень, поступая на вход блока 2, вызывает начало процесса чтения микрокоманды по адресу, находящемуся на группе входов блока5 93 2. Информация в блоке 2 находится в парафазном коде. После завершения процесса чтения информации из блока 2 его соседние выходы должны принять обратные значения. Эта ситуация (чри условии наличия на выходе регистра 1 уровня логического нуля) определяется блоком 5, и на входе 11 устанавливается уровень логической единицы. Этим уровнем регистру 3 разрешается прием кода с его группы входов, и после приема кода в регистр 3 на его выходе Формируется уровень логической единицы, которым разрешается схема сравнения 6 производить процесс сравнения групп входов 7 и 8. Также к этому моменту времени на второй группе выходов регистра 3 находится адрес следующей. микрокоманды, а на первой группе выходов этого регистра появляются коды микроопераций указывающие на действия, которые необходимо произвести в управляемом устройстве. Группа входов 7, соединенная с входами схемы 6 после завершения процесса исполнения микрокоманды, должна принять состояние аналогичное состоянию выходов 8. Это следует из организации работы асинхронных блоков зо управляемого устройства. Поясним это более подробно. 5958 6 15 26 тояние этого входа определяется завершением или незавершением второго Известны устройства, имеющие управляющий вход, предназначенный для запуска данного устройства (сигнал "Запрос" ) и управляющий выход (сигнал "Ответ" ), предназначенный длй фиксации окончания переходных процессов в устройстве. По сочетанию состояния управляющих входов (С 1) и управляющих выходов (О) таких устройств возможно определить завер" шены ли переходные процессы в уст" ройстве по следующему правилу О+9= 0 - переходные процессы в устройстве завершены; О+Э 0 - переходные процессы в устройстве не завершеныСхема 6 проводит этот анализ. Процесс сравнения завершается формированием на выходе схемы 6 уровня логической единицы, который, поступая на вход 17 блока 7, вызывает сначала сброс триггера 23 этого блока и, как следствие, перевод выхода 19 в состояние логического нуля, а затем взведение триггера 22 в состояние логической, единицы и установление 35 40 45 5055 на выходе 18 уровня логической единицы. Срабатывание триггеров 22 и23 блока 7 вызывает два процесса,протекающих параллельно. Первыйсвязан со сбросом триггера 23 и переходом выхода 19 блока 7 в состояние логического нуля. Это состояниена входе блока 2 вызывает переходвыходов этого блока в состояние когда все вьходы равны "1" или "0". При" мер схемы блока 5, приведенной нафиг. 2, рассчитан на то, что при наличии на выходе 19 блока 7 состояний логического нуля, на группе выходовблока 2 находится состояние, соответ" ствующее всем логическим единицамПосле установления этого состоянияна выходах блока 2, блок 5 производит анализ состояния входа 9. Соспроцесса, связанного с переходомтриггера 22 блока 7 в состояние логи"ческой единицы и наличием этогосостояния на входе регистра 1. Ноз- .никновение на входе регистра 1. уровня логической единицЫ вызывает процесс приема нового адреса микрокоманды с входов 13 в регистр 1. Этотпроцесс завершается переходом выхода регистра 1 в состояние логической единицы. Логическая единица,поступая через элемент НЕ Ь, вызывает установление уровня логического нуля на входе 9 блока 5 при условии установления на входах 1 Оэтого блока всех единиц и приводитк формированию на выходе 11 блока5 состояния логического нуля, которое, поступая на вход регистра 3,вызывает переход выхода этого регистра .в состояние логического нуля.Это состояние выхода регистра 3,поступая на вход схемы сравнения 6,приводит к переходу ее выхода в состояние логического нуля. Уровеньлогического нуля; поступая в блок7, 1 вызывает переход триггера 22 всостояние логического нуля, а затемвзводит триггер 23 блока 7. При этомвновь возникает сигнал .чтения из.блока 2, и параллельно нулевой уровень на выходе 18 приводит к установлению на выходе регистра 1 состояния логического нуля, и, как следствие этого, на входе 9 блока 5формируется уровень логической единицы. Далее происходит чтение из9359 Формула изобретения 1. Микропрограммное устройство управления, содержащее блок памяти, регистр адреса, регистр микрокоманд, схему сравнения и распределитель управляющих сигналов, причем группа выходов блошка памяти соединена с группой входов регистра мик-. рокоманд, первая группа информационных выходов которого соединена с первой группой входсв схемы сравнения, вторая группа информационных выходов регистра микрокоманд соединена с первой группой .,входов регистра адреса, группа выходов ко- торого соединена с группой адресных входов блока памяти, первый вход регистра адреса соединен с .первым выходом распределителя уп,равляющих сигналов, о т л и ч а ю ще е с я тем, что, с целью повышения надежности, устройство содержит узел фиксации состояния блока памяти и элемент НЕ, при 35 блока 2 и повторяется вся рассмот ренная последовательность действий.Микропрограмма исполняется циклически до возникновения на входе 15блока 7 уровня логической единицы, 5 При .этом нвобходимо,. чтобы вход 14 имел нулевое состояние. Состояние логической единицы на входе 15 блока 7 вызывает сброс триггера 24, что в свою очередь, приводит к блокировке сигнала чтения из блока 2, и после исполнения очередной микрокоманды происходит остановка устройства.Чтобы снова запустить работу устройства необходимо подать сигнал запуска на вход 14, при этом происходит пуск по адресу, хранящемуся в регистре 1.Применение изобретения позволяет организовать работу устройства на 2 О реальных задержках элементов, из которых оно состоит, что, в свою очередь, позволяет избежать параметрических отказов, т,е. отказов, вызванных увеличением задержек элемен- О тов сверх максимальных. 58 8чем выход регистра адреса через элемент НЕ соединен с входом узла фиксации состояния блока памяти, группа входов которого соединена с группой выходов блока памяти, выход узла фиксации состояния блока памяти соединен с входом регистра микро- команд, второй выход распределителя управляющих сигналов соединен с входом разрешения записи блока памяти, выход регистра микрокоманд соединен с входом схемы сравнения, выход которой соединен с первым входом распределителя управляющих сигналов, второй, третий и четвертый входы которого являются соответственно входом запуска, входом останова и входом начальной установки устройства, вторая группа входов регистра адреса является группой входов начального адреса устройства, вход регистра адреса является входом записи начального адреса устройства, группа выходов регистра микрокоманд.является группой информационных выходов устройства, вторая группа входов схемы сравнения соединена с группой информационных входов устройства, вы- хоД регистра микрокоманд соединен с входом схемы сравнения.2. Устройство по п. 1, о т л и ч а ю щ е е с я тем, что узел фиксации состояния блока памяти содержит два элемента 5 И-ИЛИ-НЕ, элемент 4 И-ИЛИ-НЕ и элемент НЕ, причем группа входов узла соединена с соответствующими входами элементов 5 И-ИЛИ-НЕ, выходы которых соединены с входами элемента 4 И-ИЛИ-НЕ, выход которого соединен с входами элементов 5 И-ИЛИ-НЕ и через элемент НЕ соединен со своими входами, вход узла соединен с входами элемента 4 И-ИЛИ-НЕ, выход элемента НЕ соединен с выходом узла.3 Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССРЮ 467351, кл, С 06 Г 9/22 19752. Авторское свидетельство СССРН 711573, кл. О 06 Р 9/22, 1977

СмотретьЗаявка

2962062, 23.07.1980

ПРЕДПРИЯТИЕ ПЯ А-3706

ЛОБАЧЕВ СЕРГЕЙ ЛЬВОВИЧ, ПЕЛЕНОВИЧ ИГОРЬ ИВАНОВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 15.06.1982

Код ссылки

<a href="https://patents.su/6-935958-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Синхронное устройство управления

Следующий патент: Микропрограммное устройство управления

Случайный патент: Разъем для двухпроводного кабеля из скрученных проводников