Сумматор-вычитатель по модулю

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1075259

Автор: Кабанов

Текст

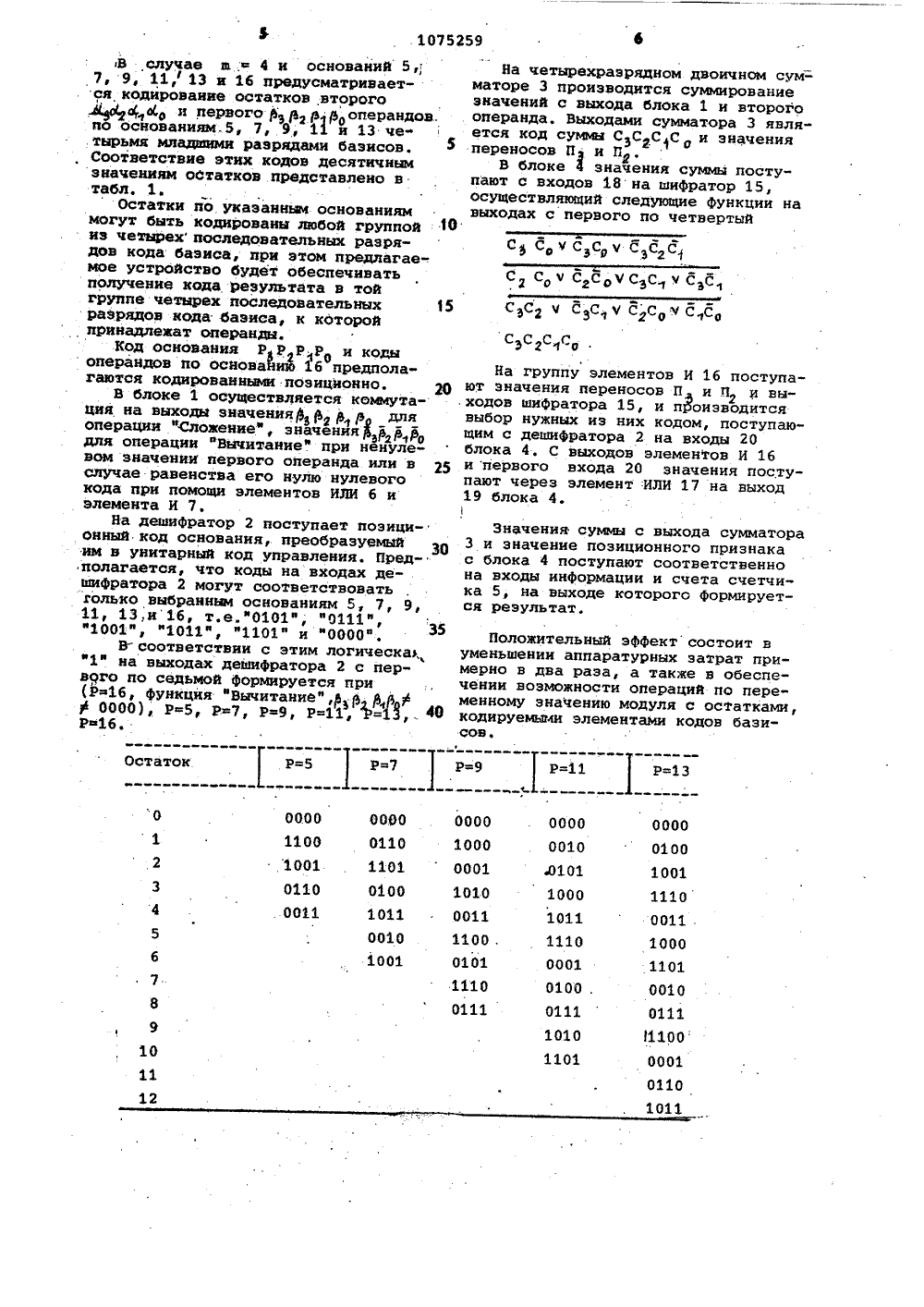

,.801075 дц 0 06 Р 7/49 ОСУДАРСТВЕННЫЙ КОМИТЕТ ССС О ЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЬ П Д 1 ТИИОПИСАНИЕ ИЗОБРЕТЕНИЯ ) ВИДЕТЕЛЬСТВУ ТОРСНО(54)(57) 1. СУММАТОР-ВЦЧИТАТЕЛЬПО ."10 ДУЛЮ, содержащий сумматор,блок инвертирования кода, причеминформационные входы блока инвертирования кода соединены с шинойпервого операнда сумматора-вычитателя по модулю, первый управляющийвход блока инвертирования кода соединен с управляющим входом "Сложения" сумматора-вычитателяпо модулю,первая и вторая группы входов сумматооа соединены соответственно свыходами блока инвертирования кодаи шиной второго операнда сумматоравычитателя по модулю, о т л и ч а ющ и й с я тем, что, с .целью сокра"щения аппаратурных затрат, он содержит дешифратор, счетчик, блок формИрования позиционного признака, элемент ИЛИ и элемент И, причем шина первого операнда сумматора-в чита:теля по модулю соединена с соответ ствующими входами элемента ИЛИ, выход которого соединен с первым вхо-дом элемента И, второй вход которого соединен с управляющим входом фВычитание" сумматора-вычитателя по модулю, выход элемента И соединен с вторым управляющим входом "блока инвертирования и первым входом дешифратора, входы с второго по оп+1)-й которого соединены с шиной кода основания сумматора-вычитателя по модулю, выходы дешифрато-.,ра соединены с соответствующими управляющими входами блока формирования позиционного признака, информа ционние входа которого соединены соответственно с выходами разрядных сумм и переносов сумматора, выходы разрядных сумм которого сое- Я динены соответственно с входами счетчика, выходы которого являются выходами результата сумматора-вычитателя по модулю, выход блока формирования позиционного признака соединен со счетным входом счетчика и является выходом позиционного признаа сумматора-вычитателя по модулю.1075259 30 2. Сумматор-вычитатель по п.1, о т л и ч а ю щ и й с я тем, что, блок Формирования позиционного признака содержит группу элементов И, элемент ИЛИ и шифратор причем управляющие входы блока соединены соот ветственно спервым входом элемента ИЛИ и первыми входами элементов И группы, вторые входы которых соедиИзобретение относится к вычислительной технике и может быть использовано в вычислительных машинах,работающих с числами в системе остаточных классов. 5Известны сумматоры по модулю,содержащие непозиционный сумматор 1.Недостатком данных сумматоров является необходимость в дополнительном позиционном сумматоре для получения дополнения второго операнда,что повышает аппаратурные затраты.Наиболее близким техническим решением к изобретению является сумматор-вычитатель по модулю, содержащий позиционный и непозиционныйсумматоры, две группы элементов И,группу элементов ИЛИ, блок инвертирования кода, блок переполнения позиционного сумматора, причем входыблока инвертирования кода соединены 20с шиной первого числа, управляющийвход блока инвертирования кода - сшиной управления, выходы блока инвертирования кода соединены с первой группой входов позиционного 25сумматора, вторая группа входов которого соединена с шиной второгочисла, третья группа входов позиционного сумматора соединена с ши.ной кода дополнения, выходы позиционного сумматора соединены с входами блока переполнения позиционногосумматора,и первыми входами элементов И первой группы, вторые входы ко-.торых подключены к первому выходу З 5блока переполнения позиционногосумматора, выходы элементов И первой группй подключены к первым входам элементов ИЛИ группы, вторые .входы которых соединены с выходамиэлементов И второй группы, выходыэлементов ИЛИ группы являвтся выходами сумматора по модулю, первые входы. элементов И второй группы подключены к выходам непозиционного сумматора, вторые входы элементов И вто- ,45рой группы подключены к второму выХоду блока переполнения позицион.ного сумматора, первая группа входовнепоэиционного сумматора подключена иены соответственно с информационными входами с (в+1)-го блока ивыходами шифратора, входы которогосоединены соответственно с информационными входами с первого по щ-йблоки, выходы элементов И группысоединены соответственно с входами элемента ИЛИ,начиная со второго, выходэлемента ИЛИ является выходом блока. 2к выходам блока инвертирования кода, вторая группа входов непозиционного сумматора подключена к шине второго числа 21..Недостатком известного сумматора по модулю является наличие позиционного сумматора, осуществляющего сложение трех чисел, что повышает аппаратурные затраты.Целью изобретения является сокра" щение аппаратурных затрат. Поставленная цель достигается тем, что сумматор-вычитатель по модулю, содержащий сумматор, блок инвертирования кода, причем инфор-мационные входы блока инвертирования кода соединены с шиной первого операнда сумматора-вычитателя по модулю, первый управляющий вход блока инвертирования кода соединен с управляющим входом "Сложения" сумматора-вычитателя по модулю, первая и вторая группы входов сумматора соединены соответственно с выходами блока инвертирования кода и шиной второго операнда сумматоравычитателя по модулю, содержит дешифратор, счетчик, блок формирования позиционного признака, элемент ИЛИ и элемент И, причем шина первого операнда сумматора-вычитателя по модулю соединена с соответствующими входами элемента ИЛИ, выход которого соединен с первым входом элемента И, второй вход которого соединен с управляющим входом "Вы"- читанием сумматора-вычитателя по модулю, выход элемента И соединен с вторыми управляющим входом блока инвертирования и первым входом дешифратора, входы с второго по (ш+1)-й которого соединены с шиной кода осно- вания сумматора-вычитателя по модулю, выходы.дешифратора соединены с соответствующими управляющими входами блока Формирования позиционного признака, информационные входы которого соединены соответствен- но а выходами разрядных сумм и переносов сумматора, выходы разрядныхсумм которого соединены соответственно с входами счетчика, выходыкоторого являются выходами результата сумматора-вычитателя по модулю,выход блока формирования позиционного признака соединен со счетнымвходом счетчика и является выходомпозиционного признака сумматора-вычитателя по модулю.Блок Формирования позиционногопризнака содержит группу элементовИ, элемент ИЛИ и шифратор, причемуправляющие входы блока соединенысоответственно с первым входом элемента ИЛИ и первыми входами элементов И группы, вторые входы которыхсоединены соответственно с информационными входами с (ш+1)-го блокаи выходами шифратора, входы которого соединены соответственно с информационными входами с первого пош-й блоки, выходы элементов И группысоединены соответственно с входамиэлемента ИЛИ, начиная со второго,выход элемента ИЛИ является выходом блока,На. Фиг, 1 представлена схемасумматора-вычитателя по модулю; на.фиг. 2 - схема блока позиционногопризнака для случая ш=4 и оснований5, 7, 9, 11, 13 и 1 б.Сумматор-вычитатель по модулюсодержит блок 1 инвертирования кода,дешифратор 2, сумматор 3, блок 4формирования позиционного признака,счетчик 5, элемент ИЛИ б, элементИ 7, шины 8 и 9 первого и второгооперандов, шину 10 кода основания,управляющие входы 11 и 12 "Сложе-.нием и фВычитание", выходную шину13, выход 14 позиционного признака,Блок 4 содержит шифратор 15,группу элементов И 1 б, элемент ИЛИ17, информационные входы 18, выход19, управляющие входы 20.ПредуСматривается кОдированиеостатка с по основанию Р, имеющемуразрядность ш, группой из ш последовательных разрядов элемента двоичного базиса системы остаточных классов, который определяется двоичнымэначенцем выражения вида(), (,2 -1 (Р-с)Ргде Ч(Р) - функция Эйлера основания Р.Коды Н(с 6) цикличны в разрядности,и.при сложении кодов базисов справедливо соотношение В+ Ф ) =Ям)+В(Р)+ПЧЧ(Р) где П - значение переноса в разРяд Ч(Р).Для ненулевого значения вычита" емого вычитание заменяется сложением с обратным кодом вычитаемого, 10 15 20 25 30 Значение переноса П является признаком, который позволяет коррек-. тировать сумму рангов, складываемых в в системе остаточных классов чисел;Поскольку код базиза не может содержать более (ш) единиц подряд, то значения П(Р), равное единице, должно формироваться и при получении .единичных значений в ш последоваТельных разрядах кода суммы. Коды базисов равномерно расположены на числовом диапазоне, поэтому при получении суммы в ш - разрядах допустима ми;Нимизация определения принадлежности кода суммы к коду базиса. Если код суммы не принадлежит коду базиса значение Г,является единичным.и значение модульной суммы на единицу выше полученной, Воэможность минимизации в анализе принадлежности кода, суммы в ш разрядах к коду базиса позволяет достаточно просто оп" ределять по коду суммы единичное значение ПЧ(Р,Сумматор-вычитатель по модулю работает следующим образом.Блок 1 осуществляет передачу прямого значения кода первого операнда на входы сумматора 3 для функции сложения или инверсного значения кода на входы сумматора для Функции вычитания при ненулевом значении операнда. Одновременно передается значение функции "Вычитание" при ненулевом операнде на один изходов дешифратора 2 для обеспечения корректировки разности по основанию, равному степени двойки. Дешиф-. ратор 2 по коду основания Р вырабатывает унитарный код управления вычислением позиционного признака,40 этот унитарный код поотупает на блок 4. Сумматором 3 осуществляетсядвоичное сложение кода второго операнда со значением поступающего сблока 1 кода. Значение суммы с сум матора 3, а также переносы из старших разрядов сумматора поступаютна информационные входы блока 4 и навходы счетчика 5. В блоке 4 Формируется сигнал позиционного призна ка, кОтОРый вычисляется пО кОду суммы для оснований, у которых .Ч 1 Р) ъ ш,или непосредственно соответствуетзначению переноса с какого-либо раз, ряда сумматора для оснований, у которых Ч(Р),4 ш, Под ш подразумевается разрядность наибольшего основания, и в этой разрядности предполагается представление кодов операндов. Счетчик 5 передает на выходыустройства код с выходов сумматора в случае равенства позиционного признака логическому нулю или увеличенный на единицу код с выходов сумматора в случае равенства позиционного признака логической едини це1075259 3 0 30 32 1 Р=9 Остаток 0000 1100 1001 0110 , 0011 ОООО 0110 1101 0100 1011 0010 1001 0000 1000 0001 1010 0011 1100 0101 1110 0111 0000 0010 0101 1000 1011 1110 0001 0100 .0111 1010 1101 ОООО 0100 1001 1110 0011 1000 1101 0010 0111 1100 3 4 5 б 7 8 9 10 11 12 0001 0110 1011 В случае а . 4 и основайий 5,;7, 9, 11,ф 13 и 16 предусматривается кодирование остатков второго .Йфаер и первого фй рроперандов по основаниям.5, 7, 9, 11 й 13 че" .тырьмя младшнми разрядами базисов. Соответствие этих кодов десятичным значениям остатков представлено в табл. 1.Остатки по укаэанным основаниям могут быть кодироваиы любой группой 10 из четырехпоследовательных разрядов кода базиса, при этом предлагае-. мое устройство будет обеспечивать получение кода результата в той группе четырех последовательных 5 разрядов кода базиса, к которой принадлежат операнды.Код основания Р Р РР и коды операндов по основайию 16 предполагаются кодированными позиционно. 20В блоке 1 осуществляется коммутация на выходы значения ф р для операции Сложение", значения у рф 0 для операции фВычитаниеф при ненулевом значении первого операнда или в случае равенства его нулю нулевого кода при помощи элементов ИЛИ б и элемента И 7.На дешифратор 2 поступает позиционный код основания, преобразуемый им в унитарный код управления. Предполагается, что коды на входах дешифратора 2 могут соответствовать голько выбранным основаниям 5, 7, 9, 11 ю 13 и 1 бю т.е.ф 0101 ф, н 0111 ф, "1001", "1011", "1101" иВ- соответствии с этим логическа ф 1 ф на выходах дешифратора 2 с первого по седьмой Формируется при (р 16, функция фВычитание", ф фй Ф ф ОООО)у Рф=5, Р 7, Рфф 9 у Р=11 ф Рш 16. На четырехраэрядном двоичном сум= маторе 3 производится суммирование значений с выхода блока 1 и второго операнда. Выходами сумматора 3 является код суммы СЗС С 1 С 0 и значения переносов П и ПВ блоке 4 значения суммы поступают с входов 18 на шифратор 15, осуществляющий следующие функции на выходах с первого по четвертый С 2 С Ч С СЧ СС У СэС 1 СС 2 ч СЗС 1 Ч ССам С,С СС На группу элементов И 16 поступают значения переносов П и П и вы-г ходов шифратора 15, и п 8 оиэводится выбор нужных из ннх кодом, поступающим с дешифратора 2 на входы 20 блока 4, С выходов элементов И 16 и первого входа 20 значения поступают через элемент:ИЛИ 17 на выход 19 блока 4.Значения суммы с выхода сумматора 3 и значение позиционного признака с блока 4 поступают соответственно на входы информации и счета счетчика 5, на выходе которого формируется результат. Положительный эффект состоит в уменьшении аппаратурных затрат примерно в два раза, а также в обеспечении возможности операций по переменному значению модуля с остатками, кодируемыми элементами кодов базисов.Ф1075259 оставитель А, Клюевехред С.Мигунова Коррект Р. ЦИц Редакт Гяск Филиал ППП фЧатентф, г. Уагород, ул. Проектная, 4 Закаэ 499/42 Ти ВНИИПИ Госу по делам 113035, Москв699 Подписственного комитета СССбретений ц открытийЖ, Раушская наб., д

СмотретьЗаявка

3529367, 28.12.1982

ПРЕДПРИЯТИЕ ПЯ В-2189

КАБАНОВ ВЛАДИМИР ЛЕОНИДОВИЧ

МПК / Метки

МПК: G06F 7/49

Метки: модулю, сумматор-вычитатель

Опубликовано: 23.02.1984

Код ссылки

<a href="https://patents.su/5-1075259-summator-vychitatel-po-modulyu.html" target="_blank" rel="follow" title="База патентов СССР">Сумматор-вычитатель по модулю</a>

Предыдущий патент: Устройство для определения экстремумов непрерывного сигнала генератора

Следующий патент: Устройство для суммирования -разрядных последовательно поступающих чисел

Случайный патент: Устройство для управления доильным аппаратом