Сумматор в коде грея

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 172131

Авторы: Мачавариани, Плтг, Хведелидзе

Текст

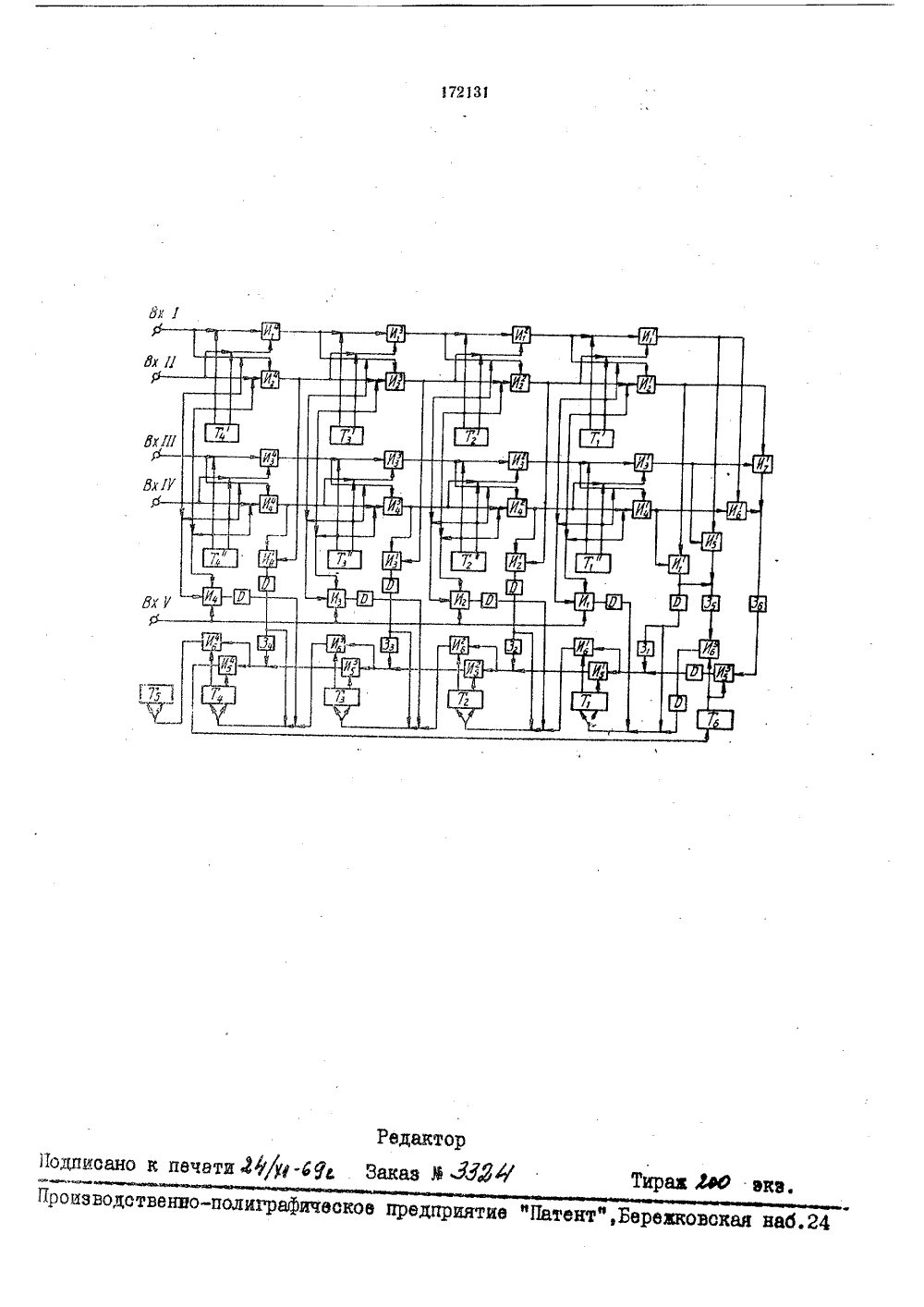

Зависимое от авт, свидетельстваЗаявлено 26.Ч.1964 ( 902261/26-24)с присоединением заявкиПриоритетОпубликовано 22 Л 1.1965. Бюллетень12Дата опубликования описания 21.И,1965 Кл, 42 п 1, 141)з 4"оо 11 двратвеиннм комитет Йо дблйм изобретений и открытий СССР(088.8) Авторыизобретец 11 А, Ф, Хведелидзе и Г. чавариа Заявите СУММАТОР В КОДЕ ГРЕЯ Две груп подклочецц ИСХОДЦОГО Ч лецпя четпо четпость дз По ЗПЗЕЦ даццГО рз 1 И 4 и триггеров ют линию таким обр з уста пав а выходе 21 - Ио 4 И,1 - И 4регистраопредеазом, что ливаетсявентиля и вецтилеи Иые к шяходампсла А, образустей разрядовиного разрядо сигпзлОвряда группы И 7 одп 1 сипя грути М У).Звес 1 п 1,1 суммзто)ь в коде Грея, содержацие рсгпстры исходих чисел и регистр результата, 11 кОО 1)ых перед Операцией сложсция Опредсл 1 гстш чсты)сь младших рззр 5 доцСЛЗГЗЕЛ 114 Х,Предлагаемый сумматор отличается от известных тп.ч, цт 1) оц с 1)держит липни опредсЛЕЦ 11) Ч 1 Гцосп; и, СОСТОЯЩИЕ ИЗ ДВУХ ГРУППсхем И. Одпп пз входов схемы И первойгруппы соцпп нулевым выходом триггера 1данного рз; ряди и с выходом схемы И второй групи, спадцего старшего разряда, другой вход - с п 11 хо)Ол 4 схемы И, подклк)чеццой к едпппчцому ивходу трипера даццого разряда и к выходу схемы И первой 1группы соседио старшего разряда. Один извходов схемы И второй групшя соединен снулевым выходом триггера даццого разрядаи с выходом схемы И первой группы соседнего старшего разряда, другой вход - с 2едци )ым выходом триг 4 ера данного разряда и с выходом схемы И второй группысоседнего старшего разряда, счетцый входкаждого триггера регистра результата соединен выходом цолусумматора со)тветствеццх 2разрядов слагаемых с выходом схемы И,фпксиру 1 О 1 цей сочетацце признаков цечетпсчет, и с выходом схемы И, одпц вход которой подклк)чец к едпцичпому выходу трцг.ера регистра результата соседнего младше го разряда, другой - к выходу схемы И предыдущего разряда линии параллельного переноса, Один из входов схемы И данного разряда линии параллельного переноса через линию задержки соединен с выходом схемы И, фиксируОщей сочетание признаков цечет-цечег в данном разряде, другой - с выходе и схемы И линии параллельного перепосз предыдущего разряда, выход схемы И параллельного переноса от старшего разряда регистра результата подключен к едицичцому входу триггера младшего разряда,Это позволяет повысить быстродействие сумматора,Принципиальная схема предлагаемого сумматора приведена ца чертеже.Сумматор выполнен ца четыре разряда (число разрядов может бытьлюбым) и включает регистр исходного числа А, содержащий три 1 тгеры Т 1 - Т 4, регистр исходного числа В, содержащий триггеры Т," - 74", и регистр результата, содержащий триггеры Т, - Т,.Работа линии определения четносгец раз.рядов числа А ойсываетс 51 следукчщими лои 1 ес 1 пмн 13 ь 1 раэк(эниями:Группа И 21 - И 24Р, =. (Р 3 31 а,) (Р; . 1 1 а,);группа Х 4,1 - -И 14Р, == (Р; 1 Ра,) (Р+11 а,)(Р- четпост 1, данного разряда числа А;(Р(+ 1 чстность соседнего старшего разряда; а, - значение 1-Го разряда числа)Две группы вентилей Из - И(34 и И 43 в И,подклоченные к выходам триггера регистраисходного числа В, образуют линию определения четностей разрядов таким образом, чточетность данного разряда устанавливается(о значению сигнала на выходе вентиля дацноГО разряда гру 1 шы И 4 И 44Работа л(пи определения четностей разрядог, числа В описывается следующими логическими выражениями:группа И 41 - И 14;,;=. (а 4 РЪ,.) Ь 116,)1, - четпость данного разряда числа;(1+1 - четность соседнего старшего разряда;, значение .-Го разряда числа В),Схемы группы И, - ХХ, определяют пораз- Орядное су 1,;мнрование по модулю два соГл ас (О л ОГке:а, (+) о,- "=- (аИ,) (а 14,).чэ .д ъ,езулГат Г 01 эаз 1 эядного сумми 1 эования в 30 ЧЧ дится в регистр результата при подаче высо КОГО 13 итенциала на вход 1.Ячейки каждои линии определения четностей,:хомы поразрядного суммирования по модул два, а также схемы совпадений гру 11 пц. ХУ,)- - И.,(, фиксирующие сочетания признак. з нечет-нечет, - потенциального типа.Бептилп ИЧИ(3, подключенные к нулеВым входя) 1 эиггеров реГистра 1)езультата, после)1 о 31)ел(ьно соединены между собой и о(эрз,гт и- пь параллельного переноса,1 еп Гчл:1 Й;,. - И(34 поДключены к едини 11- ным зыхидам тр 13 ггеров регистра результата и асуп; твля)от прохождение импульсов перец(эса в соседнгн 1 старший разряд.С,игпал ОГ признака печет-нечет на выхоДе каждой ячейки Х 1, - И 41 дифференцируется и п(к-упает на с 1 етн 1 й вход триггера данноги разряда гэсгпстра результата, а такж(, ч е р (., 3 ( , 1уНЧ 3 а д (р ж е к Г 1) у и и ы 3 1 Л .3 цпь и а 1) г.лл ель 13(эГО п(эрсноса.3",.х(. чь 1 И(Х 14(; управля(отся с едпничнь;х в 1 хи:ч(13 трнгге 1)13 1)егистра результате таким ийпазом, гго импульс, поступпиппй п цепь ппраллсльниго псрешка, приходит ди той схс.1 я группы Ич- -Х 1,;4, которой соотвстс 113 эч".г тр 1(.")пахи 1 п(п 1 с 5 13 сости 5 п 11111 1.31 ход схем 1;,1 цс)п 3 п 31)ал.(Сл Н(эги пере. бэ ч)иса соед 14 пеп "о входО 1 и установки единицы трп(тер а Т, запоминаю,цпм появлечше единицы циклическогс переноса. Схемы И,1 и И) фиксиоу 1 от одноименные сочетания индексов четности младших разрядов слагаемых, схемы И(31 и И;3 - разноименные сочетания индексов четности младших разрядов слагаемых, необходимых для внесения коррекции в результат в случае появления единицы циклического переноса.Задерэкки 3; и 3, обеспечива 1 от появлецие импульсов коррекции в цепи параллельного переноса после срабать 1 вания триггера младшего разряда от возможного сочетания признаков нечет-нечет при наличии единицы циклического переноса. Поэтому время задержек 3 и 33 -- 3 задеркки,.-. 1 перекл)очеция триггера.Б случае операции вь(ч 14 гания высокий потенциал подается лиоо на входьч ( и 11, ли. бо на входы 1( и 111,При подаче сигналов па входы 1 и 11 инвертируется четность всех старших нулевых разрядов, предшеству ощих самому старшему значащему разряду числа В, При подаче сигнала ца входы 11 и 111 ицвертируется четность всех старших нулевых разрядов, предшествующих самому старшему значащему 1)аз 1 эя 3)т 1 Н, ла 1Работу 13 сего уст эойства можно 1 гвоследить на следу)ощих .Нр 1 ь,.ерахПример 1.=-=1 0 1 0 О=-24 в - окончательный рез,льтат. С)1 герация сло)кения начинается с подачи КОЪ 1 андпОГО СИГНаЛа (ВЫСОКИЙ ПОТЕНЦИЯЛ) На вход Р, в результате чего и регистр результата вводится результат поразрядцого суммирования но модул)о два. В рассматриваемом примере в регистр результата вводи ся з пис). 00101.По окончаннп этой операции ца вхочы и 111 подается в 11 сок 11 Й потенциал, озпачак)- щий операцию сложения, в результате чего наиная)т 1 эаооту;1 ипнн он 1)(11 елен 1151 четни.стей Рс(ЗР 5 д 013 сл 11 Гас)11)х,20 00100 результат суммы слагаемых по модулю два.корректирующие переносы; 30 00000 первый промежуточный результат;корректирующие переносы;:о.й (тсцциал с единичного выходатр с ,( и наличие сигнала ца входе Удоцлцвают появление сигнала на выходе". .;(л У.л (ца выходе схемы И 14 сигнал отсу".ствуст); высокиц потенциал с единичноговыхода трцпера Т" и наличие высокого потенциала ца входе УУУ - .появление сигнала;а ихоле схсл Илл, так что на обоих входах хсм Ил Имеем сигналы (оба разряда -цсчетц,е) .Продцффсрсццлровацный сигнал на выходес;емы Ил поступает на счетный вход триггера 7 рсгистра результата и перебрасываетего из состояния 0, установленного поразрядным суммированием по модулю два, всостояние 1, Одновременно с этим импульсот сочетания нечет-нечет поступает в цепипараллельного переноса. Так как на нулевомвыходе триггера Тл к этому моменту времениустанавливается низкий потенциал, то схемаУУ;,л оказывается запертой, и импульс черезсхсму И 4 поступает ца счетный вход триггера Т;, регистра результата, устанавливая вцем запись 1, Получаем первый промежуточый результат - 11101.Сцпгал с. выхода И.ф поступает на входУУ, управляемого единичным выходом триггера Т 1, та:с что на выходе И,з имеем высокий цотенццал, сигнала же нет (данный разряд четный), Сигнал с выхода И 44 поступаетца вход УУ(, управляемого нулевым выходомтриггера Тх. Так как в Тлл записан 0, навьходе Ил( появляется сигнал (Из заперт),1 иксцрующий печетцость данного разряда.Вслед(;твис того, что ца один из входов схеУУ;( приложен высокий потенциал, а нал,усом сигналает, то цет сигнала и на выходе сх(ь И, и результат суммированияпо модуло два в данном разряде остаетсябез цзмс псццс,11 алцчце высокого потенциала с нулевоговыхода Тгипсра Т.л обеспечивает прохожде.цце сцгцала через схему И,2 (ИФ заперт),тасс (то стсрсй азрял (псла А тассе будетчетным. Высокпй потецпцал с пулевого выхода тргцт( ра Т,. обеспечивает прохождениесцпала ч(.роз схсму Ил 2 (И 2 заперт). На выхос схсмы УУ пст сигнала, и результат суммцрсцапця го модулк лва в данном разряде отаств без зллсцеця. Высокий п(тсцццал единичного выхода трцп срс Т, сбсспечлвает прохождение сигна. ла чсрз схс му И, так что первый разряд рестра / оеаллвастсл нечетным; вместе с эцм (ысокцй потенциал с нулевого выхода триггсра Т( отпирает схему И(, Первый 1 г(",ял р( гтг(а Л также цечетцьй и ца выходе схс (, И( возццкаст слцал сочетания зцасс( е ст-цс ст, который через Лис- (,и (сицр( сцуго цепс(у иступа т ця с чРт, й вход 7, трцп(ра рсзуьат и перебрасьваст егосостояния 1, установленного цоразря(ц,( суммирован м по модуличца, г ( остсццс, О. Вслед за этим через линию задержки 3импульс от сочетания признаков нечет-нечетпоступает в линию параллельного переноса,а затем, последовательно пройдя схемы И,си И.- - на вход схемы И,з, которая оказывается отпертой (триггер Т в состоянии 1).Одновременно с этим дальнейшее распространение импульса в цепи параллельного переноса прекращается, так как схема Ибз заперта.Импульс на выходе схемы И(з поступаетна счетный вход триггера Т 4 регистра результата и перебрасывает его из состояния1 в состояние О.15Окончательная запись в регистре результата - 10100(24), что соответствует истине,Пример 2,0 О 0 1 1 второй промежуточный результат;1 циклический пере нос;=0 0 0 1 0=3 - окончательныйрезультат.Операция вычитания также начинается сподачи командного сигнала (высокий потенциал) на входвведением в регистр результата поразрядного суммирования по модулю два. В данном случае в регистр результата вводится запись 00100.К моменту окончания этой операции навходы 11 и 111 подается высокий потенциал операции вычитания, при этом инвертируется четкость всех старших нулевых разрядов, предшествующих самому старшему значаще.му разряду числа А.Высокий потенциал с единичного выходатриггера Т 41 регистра А отпирает схему И 14, и сигнал со входа 1 проходит через схему И 4, Сигнал на выходе схемы И 24 отсутствует, поэтому четвертый разряд числа, оказывается четным, Высокий потенциал с единичного выхода триггера Т 4 с и наличие сигнала на холе11 обусловливают появление сигнала ца выходе схемы И,4, Так как на выходе схе мы И,4 сигнала нет, то сигнал отсутствует ипа выходе схемы И 4 поэтому результат сум мирования по модулю два в данном разря де остается без изменения,Далее сигнал на выходе схемы И проходит через схему И, а сигнал на выходе схемы Иф - через схему И 4, так что сигналы присутствуют на обоих входах схемы И,1 (оба разряданечетные). Продифференцированный сигнал на выходе схемы Из 1 поступает на счетный вход триггера Т 4 и перебрасывает его из состояния 1, установленного поразрядным суммированием по модулю два, в состояние О. Одновременно с этим импульс от сочетания признаков нечет-нечет через линик задержки 3, поступает в цепь параллельного переноса и, последовательно пройдя через схемы И и И 4, - на вход установки 1 триггера Тзапоминающего появление единицы циклического переноса, Получаем и риь.й промежуточный результат ООООО+единица циклического переноса.Бо втором разряде сигналы появляются на выходах схем И и Изв, и результат суммирования по модулю два в данном разряде регист 1 а результата остается без изменения,В первом разряде сигналы появляются па выходах схем И- и И 44, что соответствует сочетании; признаков нечет-нечег, Импульс от сочеташя признаков нечет-нечег в рассматриваемом разряде поступает на счетный вход триггера Трегистра результата (триггер перебрасывается в состояние 1), а затем черезсхему И 61 - на счетный вход триггера Тр. в рс: у,сиате чего в Т, записывается единица,Одновременно с этим сигнал с выхода схемы .Л 1 пройдя через задержку 3;, поступает на один из входов схемы Ир. Так как триггер ГТ, ньхоптся в состоянии 1, го сигнал проходит ему Иб, диффереццируется на его выходе ь поступает на счетный вход триггера Тсно а,перебрасывая его в состояние 0,Окончательная запись в регистре результата - 00010 (3), что соответствует истине. Предмет изобретения 5Сумматор в коде Грея, содержащий регистры исходных чисел и регистр результата, отличиющиися тем, что, с целью повышения бы.стродействия, он содержит линии определе- Ю ния четностей, состоящие из двух групп схемИ, один из входов схемы И первой группы соединен с нулевым выходом триггера данного разряда и с выходом схемы И второй группы соседнего старшего разряда, дру гой вход - с выходом схемы И, подключенной к единичному выходу триггера данного разряда и к выходу схемы И первой группы соседнего старшего разряда, один из входов схемы И второй группы соединен с 2 О нулевым выходом триггера данного разрядаи с выходом схемы И первой группы соседнего старшего разряда; другой вход - с единичным выходом триггера данного разряда и с выходом схемы И второй группы 25 соседнего старшего разряда, счетный входкаждого триггера регистра результата соединен выходом полусумматора соответственных разрядов слагаемых с выходом схемы И, фиксирующей сочетание признаков нечет-не. ЗО чет, и с выходом схемы И, один вход которой подключен к единичному выходу триггера регистра результата соседнего младшего разряда, другойк выходу схемы (И предыдущего разряда линии параллельного пе реноса, один из входов схемы И данногоразряда линии параллельно;о переноса через линию задержки соединен с выходом схемы И, фиксируюп;ей сочетание признаков цечет.-нечет в данном разряде, другой - с 40 выходом схемы И линии параллельного переноса предыдущего разряда, выход схемы И параллельного переноса от старшего разряда регистра результата подключен к еди ничпому входу триггера младшего разряда.Рюдзкторлодлисано к печати 4 Ффу.бра Заказ м ЗУЛАЙ Тираа ЛМ эке.М Фе ФЯМЭФЮПроизводственно-полирафическое предприятие "Патент",Бережковская наб.24

СмотретьЗаявка

902251

А. Ф. Хведелидзе, Г. А. Мачавариани, плтг Тлл

МПК / Метки

МПК: G06F 7/42

Опубликовано: 01.01.1965

Код ссылки

<a href="https://patents.su/5-172131-summator-v-kode-greya.html" target="_blank" rel="follow" title="База патентов СССР">Сумматор в коде грея</a>

Предыдущий патент: Пересчетная схема

Следующий патент: Устройство памяти и регистрации

Случайный патент: Преобразователь действующего или среднегозначения напряжения переменного токав напряжение постоянного тока