Параллельный счетчик по модулю -дешифратор количества единиц в -разрядном двоичном коде

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

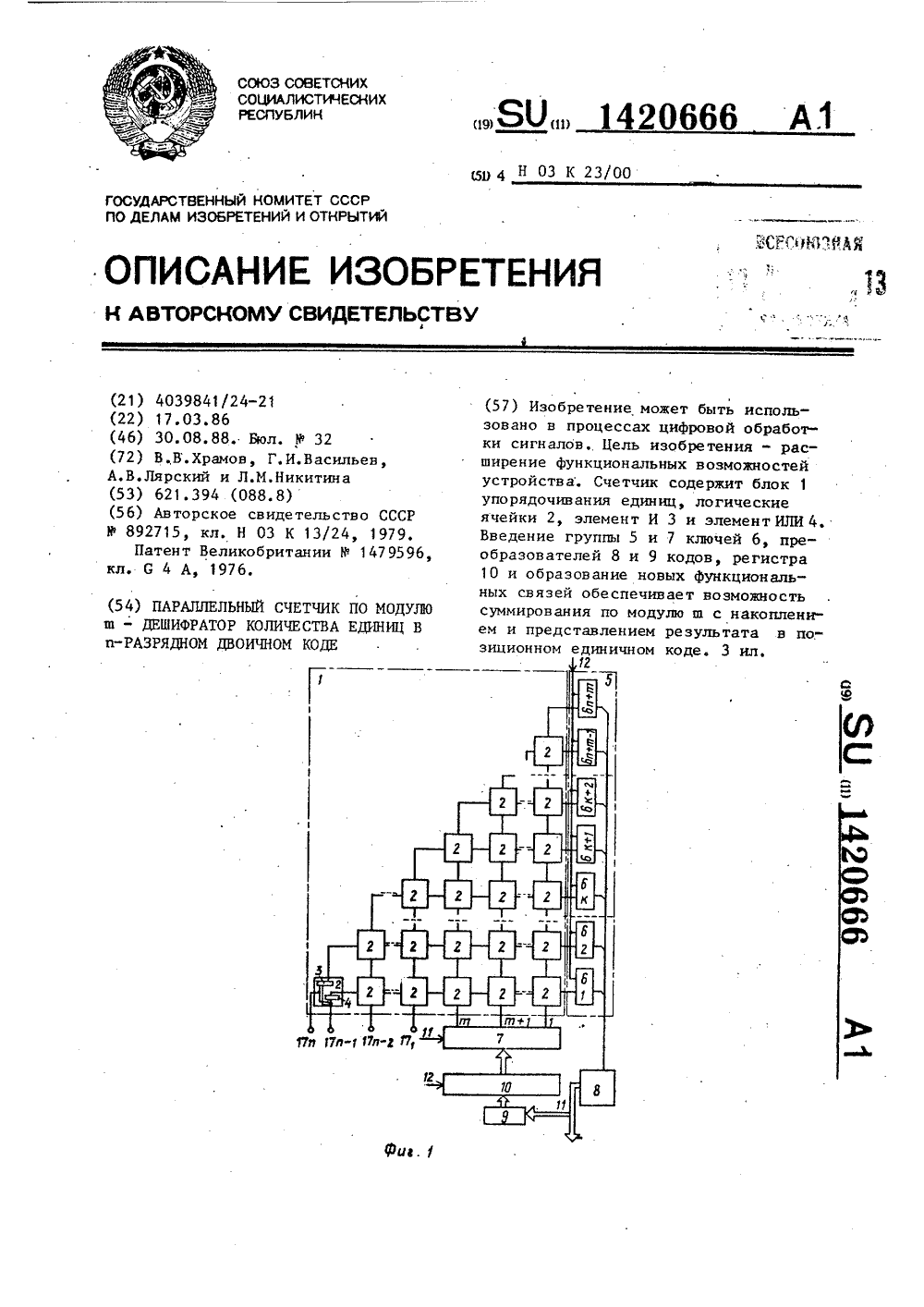

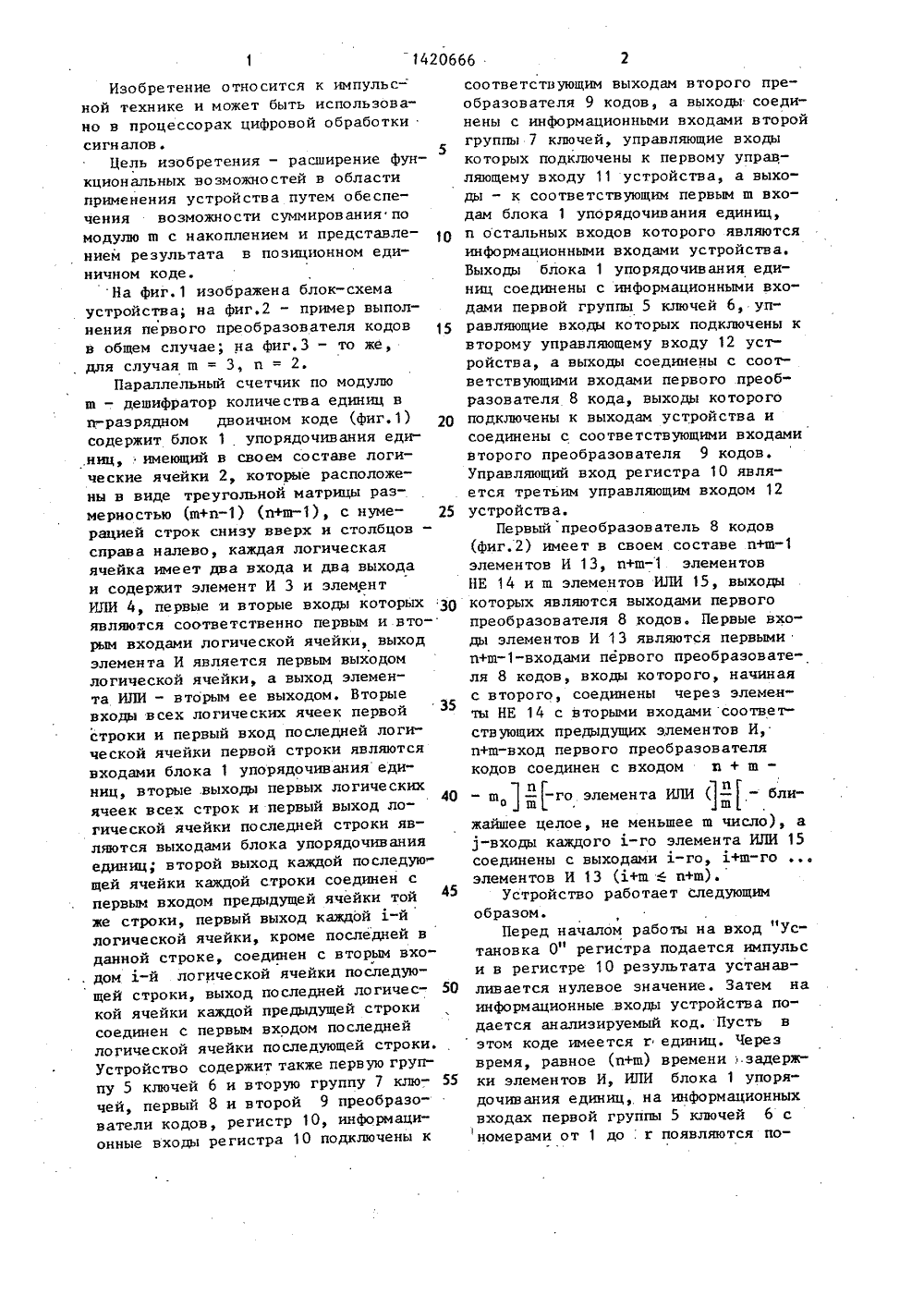

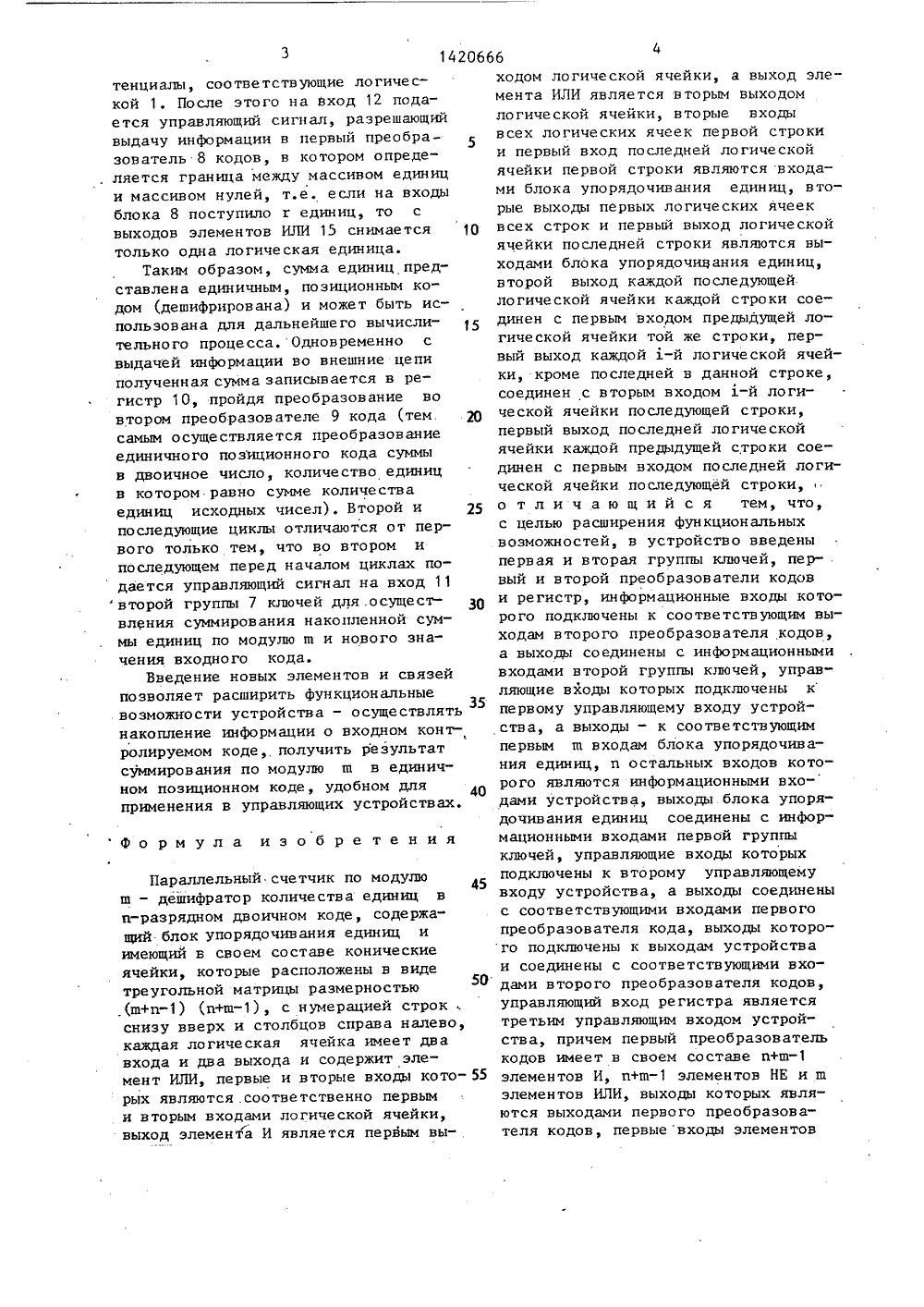

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 19) (1 20666 А.1 23 00 ОПИСАНИЕ ИЗОБРЕТЕНИЯ АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Л в о СССР 1979. 147 9596,(54) ПАРАЛЛЕЛЬНЫЙ СЧЕТЧИК ш - ДЕШИФРАТОР КОЛИЧЕ СТВА и-РАЗРЯДНОМ ДВОИЧНОМ КОДЕ О МОДУЛЮДИНИЦ В ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИИ(57) Изобретение может быть использовано в процессах цифровой обработки сигналов. Цель изобретения - расширение функциональных возможностей устройства. Счетчик содержит блок 1 упорядочивания единиц, логические ячейки 2, элемент И 3 и элемент ИЛИ 4. Введение группы 5 и 7 ключей 6, преобразователей 8 и 9 кодов, регистра 10 и образование новых функциональных связей обеспечивает возможность суммирования по модулю ш с накоплением и представлением результата в позиционном единичном коде. 3 ил.2Изобретение относится к импульс-ной технике и может быть использовано в процессорах цифровой обработкисигналов,Цель изобретения - расширение функциональных возможностей в областиприменения устройства путем обеспечения возможности суммирования помодулю ш с накоплением и представлением результата в позиционном единичном коде.На фиг.1 изображена блок-схемаустройства; на фиг,2 - пример выполнения первого преобразователя кодовв общем случае; на фиг.3 - то же,для случая ш = 3, п = 2.Параллельный счетчик по модулюш - дешифратор количества единиц ви-разрядном двоичном коде (фиг.1) 20содержит блок 1 упорядочивания еди,ниц, имеющий в своем составе логические ячейки 2, которые расположены в виде треугольной матрицы размерностью (ш+и) (и+ш), с нумерацией строк снизу вверх и столбцов -справа налево, каждая логическаяячейка имеет два входа и два выходаи содержит элемент И 3 и элементИЛИ 4, первые и вторые входы которых 30являются соответственно первым и вто-рым входами логической ячейки, выходэлемента И является первым выходомлогической ячейки, а выход элемента ИЛИ - вторым ее выходом. Вторыевходы всех логических ячеек первойстроки и первый вход последней логической ячейки первой строки являютсявходами блока 1 упорядочивания единиц, вторые .выходы первых логических40ячеек всех строк и первый выход логической ячейки последней строки являются выходами блока упорядочиванияединиц; второй выход каждой последующей ячейки каждой строки соединен с45первым входом предыдущей ячейки тоиже строки, первый выход каждой д-йлогической ячейки, кроме последней вданной строке, соединен с вторым вхо. дом -й логической ячейки последующей строки, выход последней логической ячейки каждой предыдущей строкисоединен с первым входом последнейлогической ячейки последующей строки.Устройство содержит также первую группу 5 ключей 6 и вторую группу 7 ключей, первый 8 и второй 9 преобразователи кодов, регистр 10, информационные входы регистра 10 подключены к соответствующим выходам второго преобразователя 9 кодов, а выходы соединены с информационными входами второй группы 7 ключей, управляющие входы которых подключены к первому управляющему входу 11 устройства, а выходы - к соответствующим первым ш входам блока 1 упорядочивания единиц, и остальных входов которого являются информационными входами устройства. Выходы блока 1 упорядочивания единиц соединены с информационными входами первой группы 5 ключей 6, управляющие входы которых подключены к второму управляющему входу 12 устройства, а выходы соединены с соответствующими входами первого преобразователя 8 кода, выходы которого подключены к выходам устройства и соединены с соответствующими входами второго преобразователя 9 кодов. Управляющий вход регистра 10 является третьим управляющим входом 12 устройства.Первый преобразователь 8 кодов (фиг.2) имеет в своем составе и+шэлементов И 13, п+шэлементов НЕ 14 и ш элементов ИЛИ 15, выходы которых являются выходами первого преобразователя 8 кодов. Первые входы элементов И 13 являются первыми и+ш-входами первого преобразователя 8 кодов, входы которого, начиная с второго, соединены через элементы НЕ 14 с вторыми входами соответствующих предыдущих элементов И, и+ш-вход первого преобразователя кодов соединен с входом и + ш пГ 1 пГ - ш- -го элемента ИЛИ ( -- бли",1 шжайшее целое, не меньшее ш число), а 1-входы каждого -го элемента ИЛИ 15 соединены с выходами й.-го, д+ш-го элементов И 13 (1+ши+ш).Устройство работает следующим образом.Перед началом работы на вход "Установка 0" регистра подается импульс и в регистре 10 результата устанавливается нулевое значение. Затем на информационные входы устройства подается анализируемый код. Пусть в этом коде имеется г единиц. Через время, равное (и+ш) времени: задержки элементов И, ИЛИ блока 1 упорядочивания единиц, на информационных входах первой группы 5 ключей 6 с номерами от 1 до, г появляются потенциалы, соответствующие логической 1. После этого на вход 12 подается управляющий сигнал, разрешающий выдачу информации в первый преобразователь 8 кодов, в котором опреде. ляется граница между массивом единиц и массивом нулей, т.е. если на входы блока 8 поступило г единиц, то с выходов элементов ИЛИ 15 снимается 10 только одна логическая единица.Таким образом, сумма единиц представлена единичным, позиционным кодом (дешифрирована) и может быть использована для дальнейшего вычислительного процесса. Одновременно с выдачей информации во внешние цепи полученная сумма записывается в регистр 10, пройдя преобразование во втором преобразователе 9 кода (тем. самым осуществляется преобразование единичного позиционного кода суммы в двоичное число, количество единиц в котором равно сумме количества единиц исходных чисел). Второй и 25 последующие циклы отличаются от первого только тем, что во втором и последующем перед началом циклах по дается управляющий сигнал на вход 11 второй группы 7 ключей для .осуществления суммирования накопленной суммы единиц по модулю ш и нового значения входного кода.Введение новых элементов и связей позволяет расширить функциональные возможности устройства - осуществлять накопление информации о входном контролируемом коде, получить результат суммирования по модулю ш в единичном позиционном коде, удобном для 40 применения в управляющих устройствах.Формула изобретенияПараллельный счетчик по модулю ш - дешифратор количества единиц в и-разрядном двоичном коде, содержащий блок упорядочивания единиц и имеющий в своем составе конические ячейки, которые расположены в виде треугольной матрицы размерностью (ш+и) (и+ш), с нумерацией строк, снизу вверх и столбцов справа налево, каждая логическая ячейка имеет два входа и два выхода и содержит элемент ИЛИ, первые и вторые входы которых являются .соответственно первым и вторым входами логической ячейки, выход элемента И является первым выходом логической ячейки, а выход элемента ИЛИ является вторым выходомлогической ячейки, вторые входывсех логических ячеек первой строкии первый вход последней логическойячейки первой строки являются входа -ми блока упорядочивания единиц, вторые выходы первых логических ячееквсех строк и первый выход логическойячейки последней строки являются выходами блока упорядочивания единиц,второй выход каждой последующейлогической ячейки каждой строки соединен с первым входом предыдущей логической ячейки той же строки, первый выход каждой -й логической ячейки, кроме последней в данной строке,соединен с вторым входом 1-й логической ячейки последующей строки,первый выход последней логическойячейки каждой предыдущей строки соединен с первым входом последней логической ячейки последующей строки,о т л и ч а ю щ и й с я тем, что,с целью расширения функциональныхвозможностей, в устройство введеныпервая и вторая группы ключей, первый и второй преобразователи кодови регистр, информационные входы которого подключены к соответствующим выходам второго преобразователя кодов,а выходы соединены с информационнымивходами второй группы ключей, управляющие входы которых подключены кпервому управляющему входу устройства, а выходы - к соответствующимпервым ш входам блока упорядочивания единиц, и остальных входов которого являются информационными входами устройства, выходы блока упорядочивания единиц соединены с информационными входами первой группыключей, управляющие входы которыхподключены к второму управляющемувходу устройства, а выходы соединеныс соответствующими входами первогопреобразователя кода, выходы которого подключены к выходам устройстваи соединены с соответствующими входами второго преобразователя кодов,управляющий вход регистра являетсятретьим управляющим входом устройства, причем первый преобразователькодов имеет в своем составе и+ш элементов И, п+шэлементов НЕ и шэлементов ИЛИ, выходы которых являются выходами первого преобразователя кодов, первыевходы элементов14206 бб 61 пгвходом и+ш-ш--го элемента ИЛИшЧпГ- ближайшее целое не меньшее3 ши- число), а 1-е входы каждого д-гоэлемента ИЛИ соединены с выходами1-го, 1+ш элементов И ( + шс а + ш)И являются первыми и+швходами первого преобразователя кодов, входыпервого преобразователя кодов, начиная с второго, соединены через элементы НЕ с вторыми входами предыдущего элемента И, и+ш-вход первогопреобразователя кодов соединен с и Составитель П.Смирноведактор А.Маковская Техред Л. Олийнык Корректор. Л. ай Заказ 334/57 Тир ВНИИПИ Госуд по делам 113035, Москва9 е Подпиого комитета СССий и открытийаушская наб., д. стве брет -35,Производственно-полиграфическое предприятие, г. Ужгород, ул, Проектная,

СмотретьЗаявка

4039841, 17.03.1986

СЕРПУХОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНО-ИНЖЕНЕРНОЕ УЧИЛИЩЕ РАКЕТНЫХ ВОЙСК ИМ. ЛЕНИНСКОГО КОМСОМОЛА

ХРАМОВ ВЛАДИМИР ВИКТОРОВИЧ, ВАСИЛЬЕВ ГЕННАДИЙ ИННОКЕНТЬЕВИЧ, ЛЯРСКИЙ АРКАДИЙ ВАСИЛЬЕВИЧ, НИКИТИНА ЛЮБОВЬ МИХАЙЛОВНА

МПК / Метки

МПК: H03K 23/00

Метки: двоичном, дешифратор, единиц, коде, количества, модулю, параллельный, разрядном, счетчик

Опубликовано: 30.08.1988

Код ссылки

<a href="https://patents.su/4-1420666-parallelnyjj-schetchik-po-modulyu-deshifrator-kolichestva-edinic-v-razryadnom-dvoichnom-kode.html" target="_blank" rel="follow" title="База патентов СССР">Параллельный счетчик по модулю -дешифратор количества единиц в -разрядном двоичном коде</a>

Предыдущий патент: Счетное устройство с контролем

Следующий патент: Счетчик импульсов

Случайный патент: Компонентный дифференциальный магнитометр